Interleave address generator

A technology of address generation and address, applied in the direction of responding to error generation, using interleaving technology for error correction/detection, redundant code for error detection, etc., can solve problems such as large processing burden, processing delay, and large burden of interleaving patterns

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

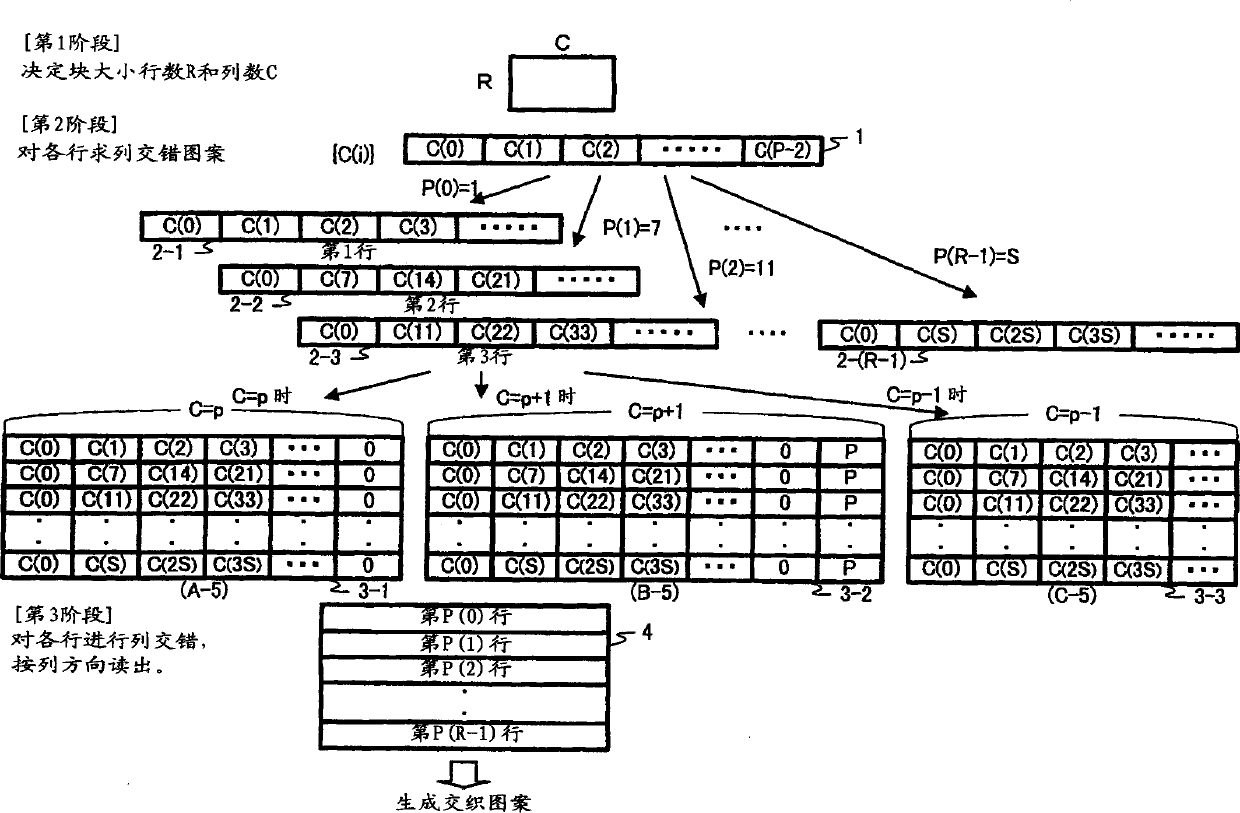

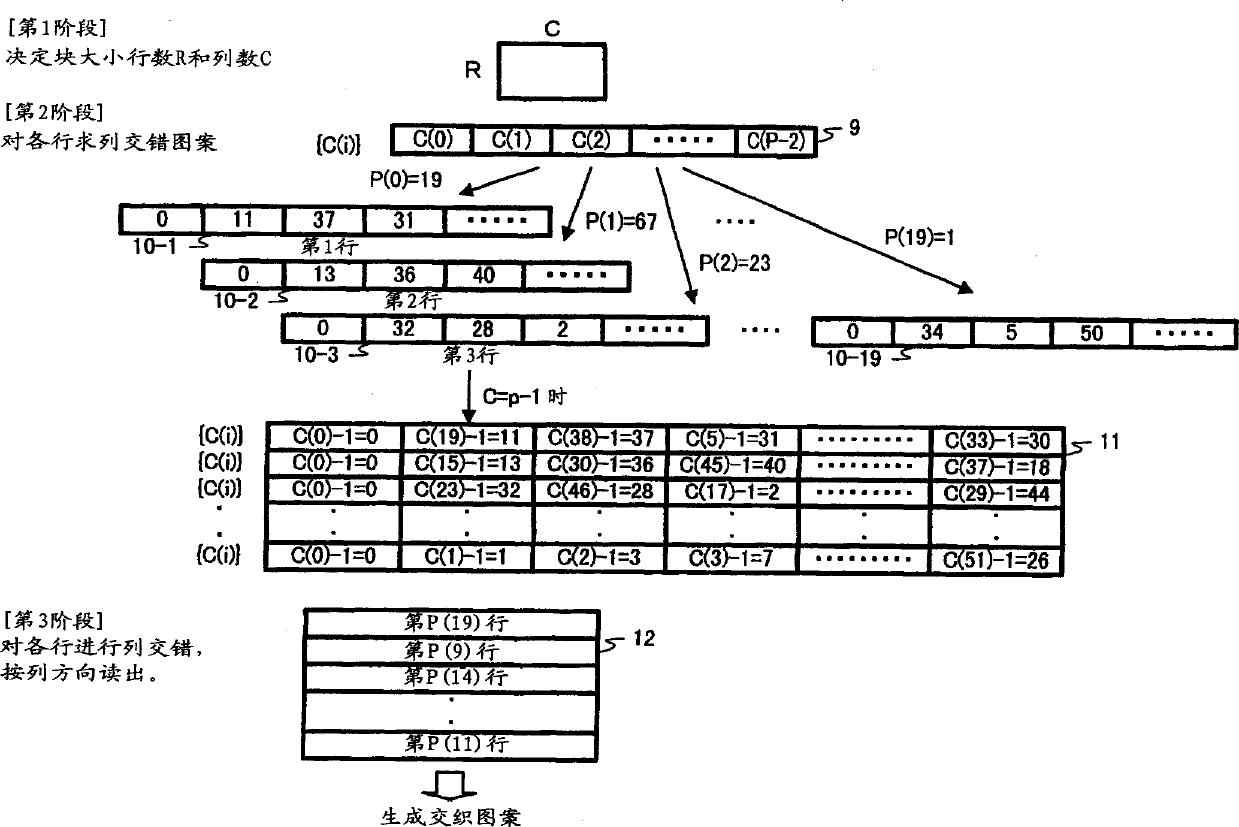

Method used

Image

Examples

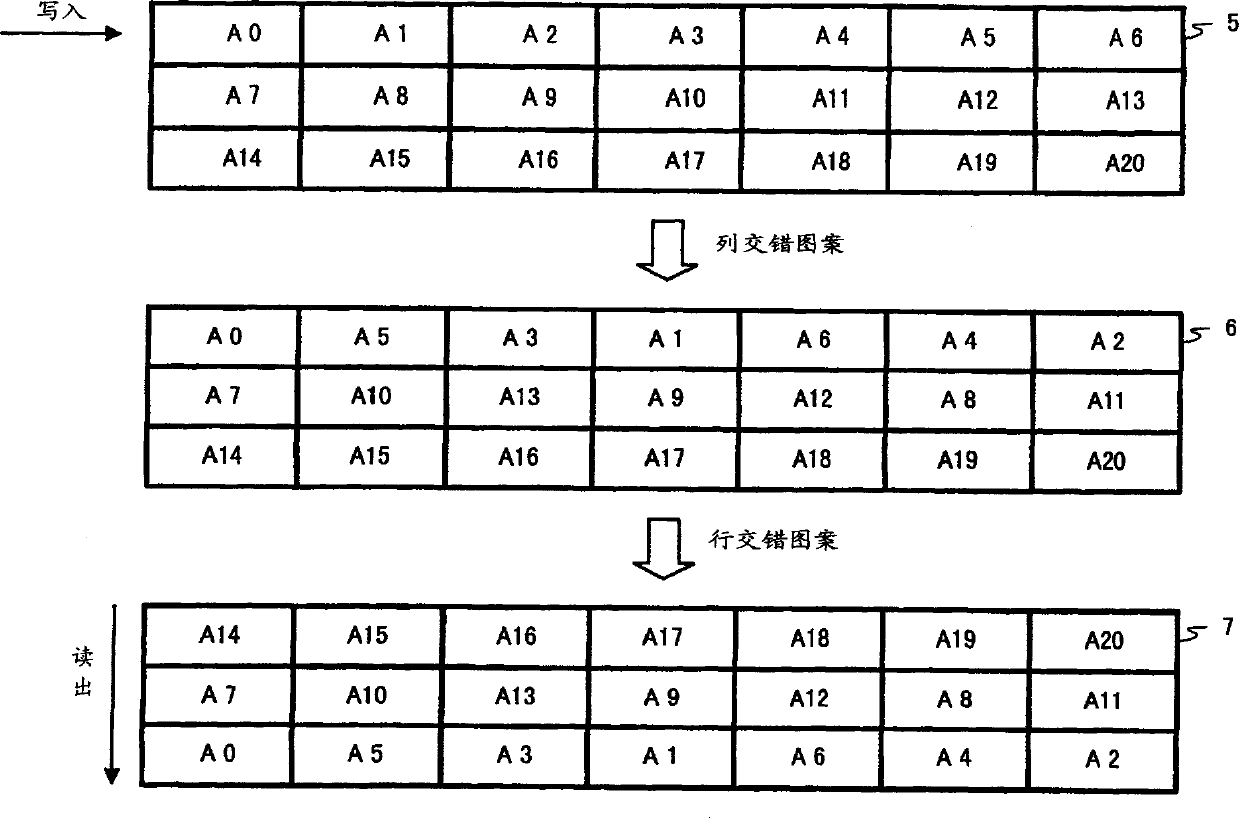

Embodiment 1

[0146] Fig. 7 is a block diagram showing the structure of an interleaving address generation device according to Embodiment 1 of the present invention. As shown in the figure, the interleave address generation device of this embodiment has: row counter 11, memory address generation device 12, memory 13 (second storage unit), memory 14 (first storage unit), multiplier 15 (address offset shift calculation unit), an adder 16, and a size comparison unit 17. On the other hand, the memory address generation device 12 has a memory 21 (third storage means), a selector 22 , an adder 23 , a comparison and difference device 24 , a selector 25 , and a FIFO 26 .

[0147] The row counter 11 sequentially outputs the row numbers of each row from the first row to the memory 14 and the memory 12 . In this case, in the case of outputting the row number of the Mth row, j=M-1 is output. That is, first, the row numbers j=0 to j=R-1 of the first column are output, and then the row numbers j=0 to j...

Embodiment 2

[0165] In Embodiment 2, a turbo encoding apparatus having the interleaving address generating apparatus of Embodiment 1 will be described. Fig. 11 is a block diagram showing the structure of a turbo encoding device according to the second embodiment.

[0166] The turbo encoding device 40 of this embodiment includes: recursive organization convolutional encoders 41 , 43 , and an interleaver 42 .

[0167] The recursive tissue convolutional encoder 41 encodes the input information sequence with a recursive tissue convolutional code. The interleaver 42 performs the interleaving described in the first embodiment on the similarly input information sequence. The recursive convolutional encoder 43 receives the information sequence output from the interleaver 42 as input, and performs encoding of a recursive convolutional code.

[0168] Next, the operation of the turbo encoding device 40 configured as described above will be described. The information sequence input to the turbo enc...

Embodiment 3

[0173] In Embodiment 3, a turbo decoding apparatus having the interleave address generating apparatus of Embodiment 1 will be described. The turbo decoding device receives and decodes the code sequence output from the turbo coding device of the third embodiment. Fig. 12 is a block diagram showing the structure of a turbo decoding device according to the third embodiment.

[0174] The turbo decoding device 50 of this embodiment has: soft output decoders 51 , 53 , an interleaver 52 , and a deinterleaver 54 .

[0175] The soft output decoder 51 encodes the received sequence encoded by the recursive convolutional encoder 41 shown in Embodiment 2 based on prior information from the deinterleaver 54 described later, and the received sequence that is output without encoding. sequence for error correction decoding. This prior information is soft decision information of the received sequence 1 bit earlier. The interleaver 52 interleaves the output of the soft output decoder 51 using...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap