Pretaking rack and panel construction of sequence type data system and its operation method

A technology of a data system and an operation method, which is applied in the direction of electrical digital data processing, instruments, etc., can solve the problems of reduced performance, many pins, and increased packaging cost of the scaling engine 20, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

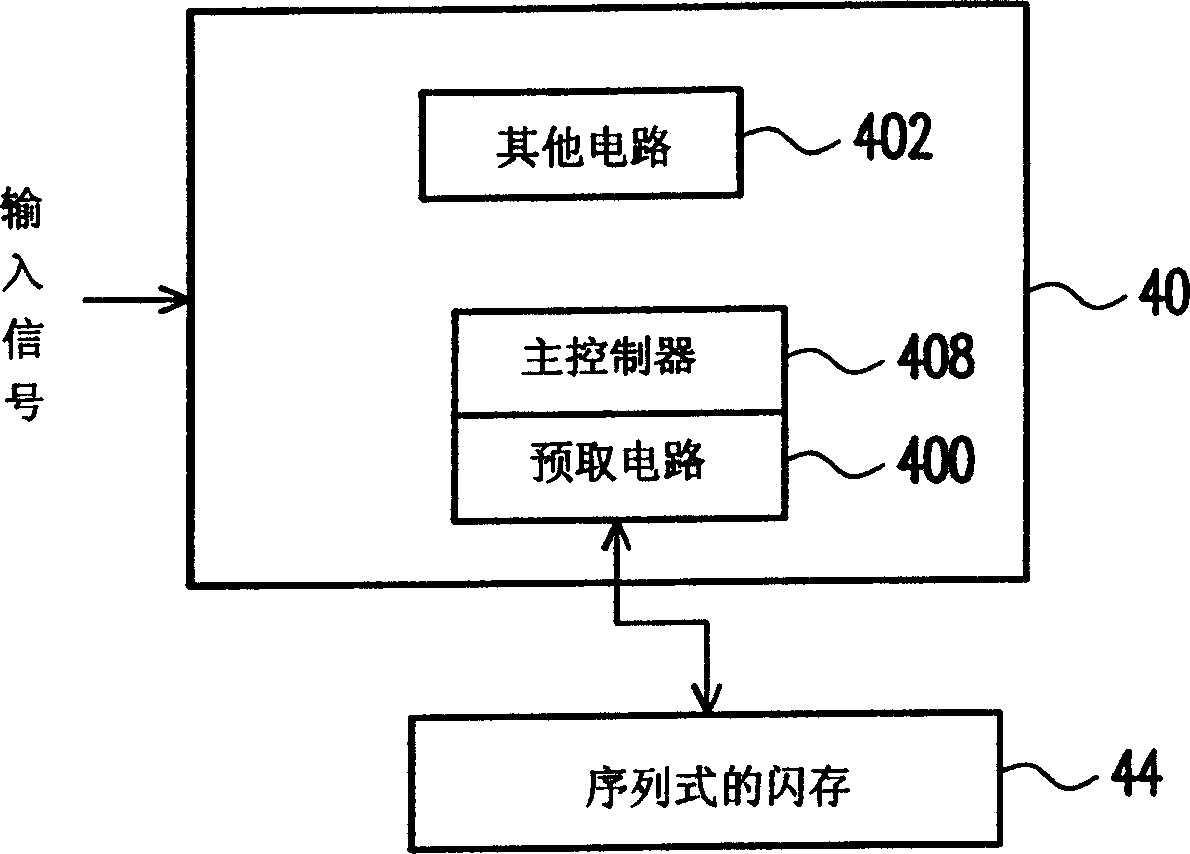

[0032] figure 2 A circuit block diagram of a prefetch architecture of a serial data system according to a preferred embodiment of the present invention is shown, in which a prefetch circuit is built in and a serial flash memory is plugged in. In this figure, a scaling engine 40 and other circuits 402 are included, and the sequential flash memory 44 , the prefetching circuit 400 and the main controller 408 constitute the prefetching architecture of the serial data system. Wherein, the scaling engine 40 includes a main controller 408 and a built-in prefetch circuit 400 . In addition, the scaling engine 40 is plugged with a serial flash memory 44 .

[0033] According to the present invention, since the prefetching circuit 400 is built in the scaling engine 40, the prefetching circuit 400 can pre-fetch the data and instructions required by the main controller 408, and wait for the main controller 408 to fetch them, which overcomes the sequential flash memory 44 Insufficient band...

no. 2 example

[0035] Please refer to image 3 , which shows a schematic block diagram of a prefetch architecture of a sequential data system of the present invention. Wherein, the main controller 60 operates according to the clock pulse signal, and sends commands through the main controller bus 62 to obtain data. As those skilled in the art know, the main controller 60 can be an 8-bit or 16-bit main controller. , but not limited to this. Moreover, the prefetching circuit 64 is connected to the main controller bus 62 to provide data, and pre-fetches the instructions and data required by the main controller 60 , waiting for the main controller 60 to fetch. The serial memory 68 provides data to the prefetch circuit 64 through the serial bus 66. As those familiar with the art know, the serial bus 66 interface can be I 2 C bus, serial peripheral interface bus or LPC bus, but not limited thereto.

[0036] Wherein, the buffer memory 644 is also included in the prefetch circuit 64 to store the d...

no. 3 example

[0048] Please refer to Figure 4 , which shows a flow chart of another serial data system prefetch architecture operation method of the present invention, this operation method is suitable for the prefetch circuit to obtain data from the serial memory through the serial bus, and through the main controller bus Send data to the host controller. Among them, the serial bus and the main controller bus use different communication protocols, and the method flow is as follows:

[0049] s102. The main controller sends the data address value to the prefetching circuit via the main controller bus.

[0050] s104. Go to the prefetch circuit to find the data corresponding to the data address value.

[0051] s106. The prefetching circuit judges whether the data corresponding to the data address value already exists in the prefetching circuit.

[0052] s108 , proceeding to step s106 , if the data corresponding to the data address value already exists in the prefetch circuit, then copy the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com