Sequencing frequency divider

A frequency dividing device, the technology of input clock, applied in the direction of using record carrier and instructions for program control, data processing power supply, etc., can solve the problems of jitter, the duty cycle is not 50%-50%, etc., to achieve the effect of low operating clock

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] Regarding the technology, means and specific structural features adopted by the present invention to achieve the above-mentioned purpose, a preferred and feasible embodiment is now given, and further disclosed by illustrations, as follows.

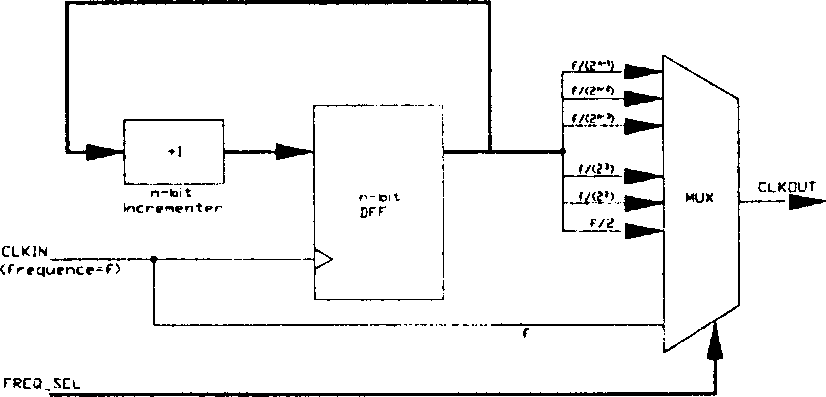

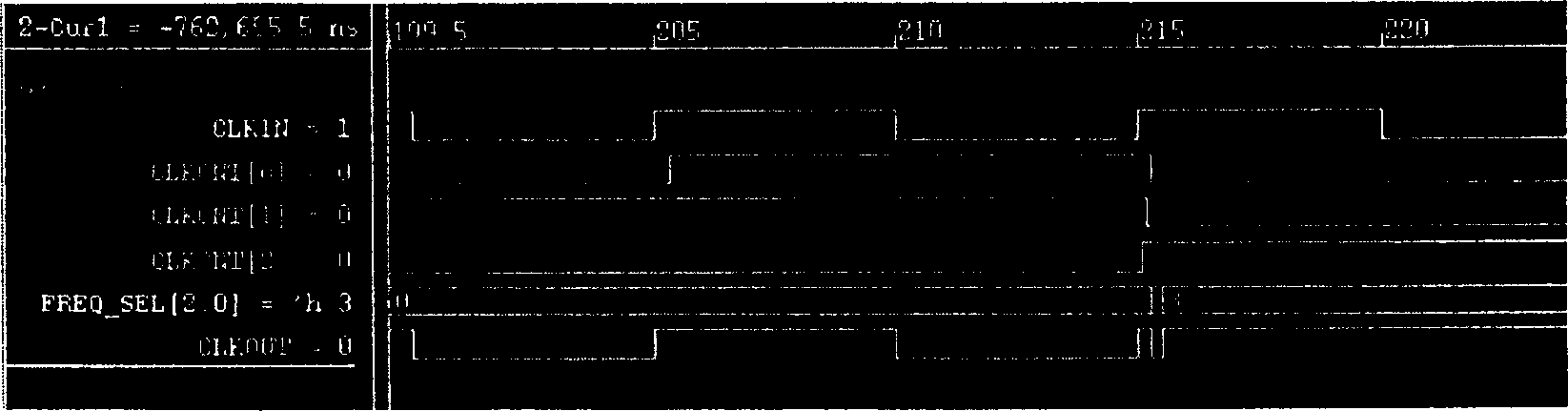

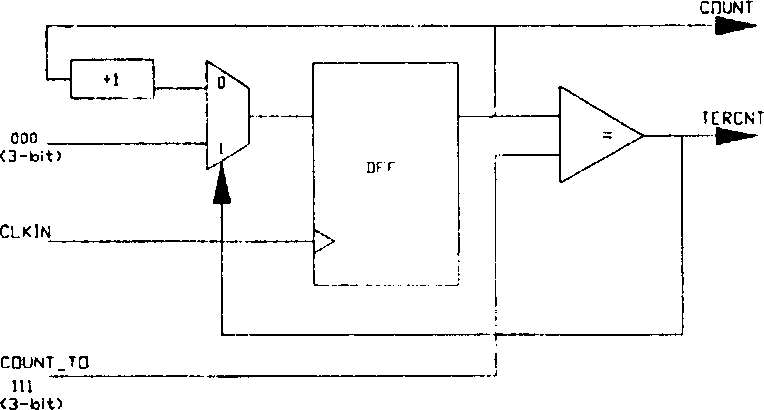

[0039] The present invention provides a programmable frequency division device for converting an input clock (which can be generated by an oscillator) into a target clock, the frequency of the input clock being 2 times the frequency of the target clock m times, where m is a positive integer greater than 0, please refer to FIG. 3A , the device includes: an n-bit adder 31 and an n-bit D-type flip-flop 32 . An adjustment parameter 301 and a feedback signal 302 are input to the adder 31, and the adder 31 adds the adjustment parameter 301 and the feedback signal 302 to generate a first output signal 303, and outputs the signal 303, wherein the adjustment parameter includes n bits , n is a positive integer greater than 0, and m≤n (for exa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More