Decapsulate method for synchronous digital series link access procedure

A link access procedure, a technology for synchronizing digital series, applied in the direction of digital transmission system, transmission system, data exchange network, etc., can solve the problems of consuming logic resources, increasing the complexity of logic programming, and reducing circuit speed.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] Hereinafter, the present invention will be further described in detail through specific embodiments in conjunction with the accompanying drawings.

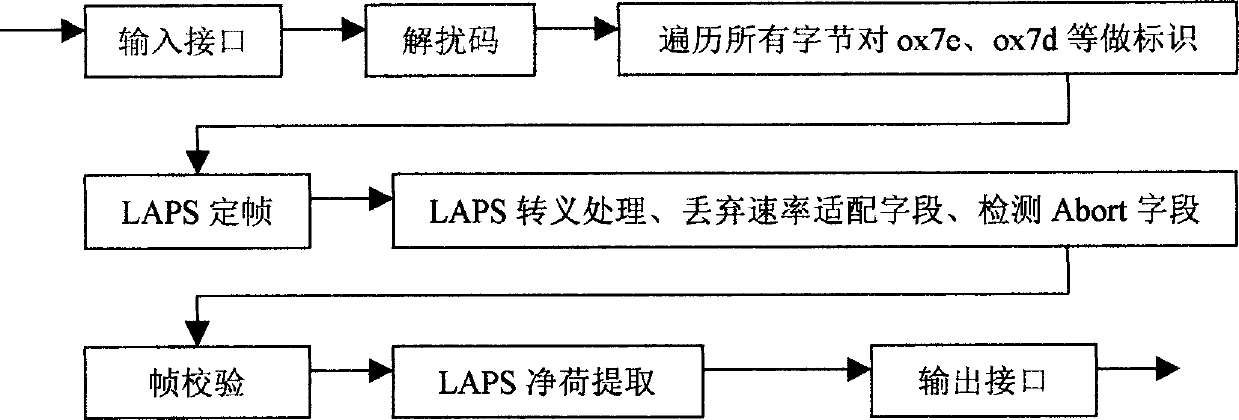

[0024] The decapsulation of LAPS needs to complete the following functions:

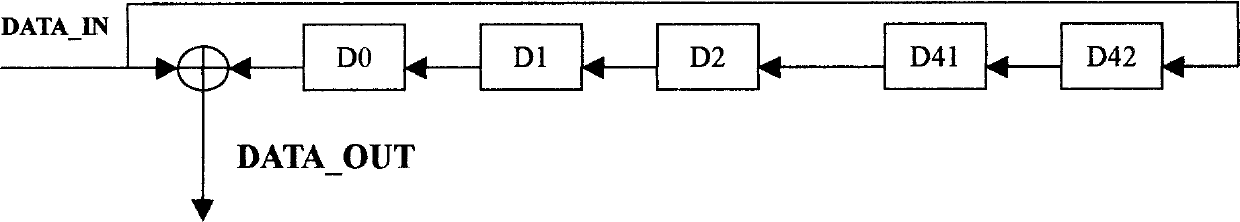

[0025] 1: X 43 +1 self-synchronizing descrambling code

[0026] 2: LAPS fixed frame

[0027] 3: Discard the rate adaptation field

[0028] 4: Discard and check the Abort field

[0029] 5: LAPS escape processing

[0030] 6: LAPS address, control, SAPI field detection

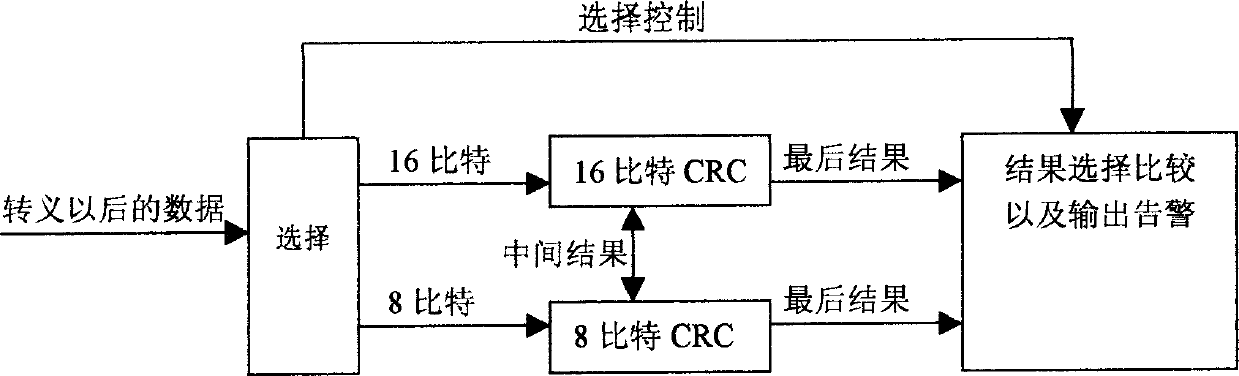

[0031] 7: CRC32 calculation

[0032] 8: Discard LAPS frame header, LAPS information payload extraction and discard frame tail

[0033] The double-byte internal data bus structure makes the processing of steps 2 to 8 more complicated. As shown in Figure 2 is a block diagram of the processing flow of the logical LAPS decapsulation method.

[0034] The function of the input interface is to receive data according to the input data valid indication signal, and the data bus width can be 16 bit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com