Processor block for forming large-scale extendible processor system

A data processing system and processor technology, applied in memory systems, electrical digital data processing, instruments, etc., can solve problems such as limiting the actual bandwidth of the chip, long memory delay, and still existing requirements.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

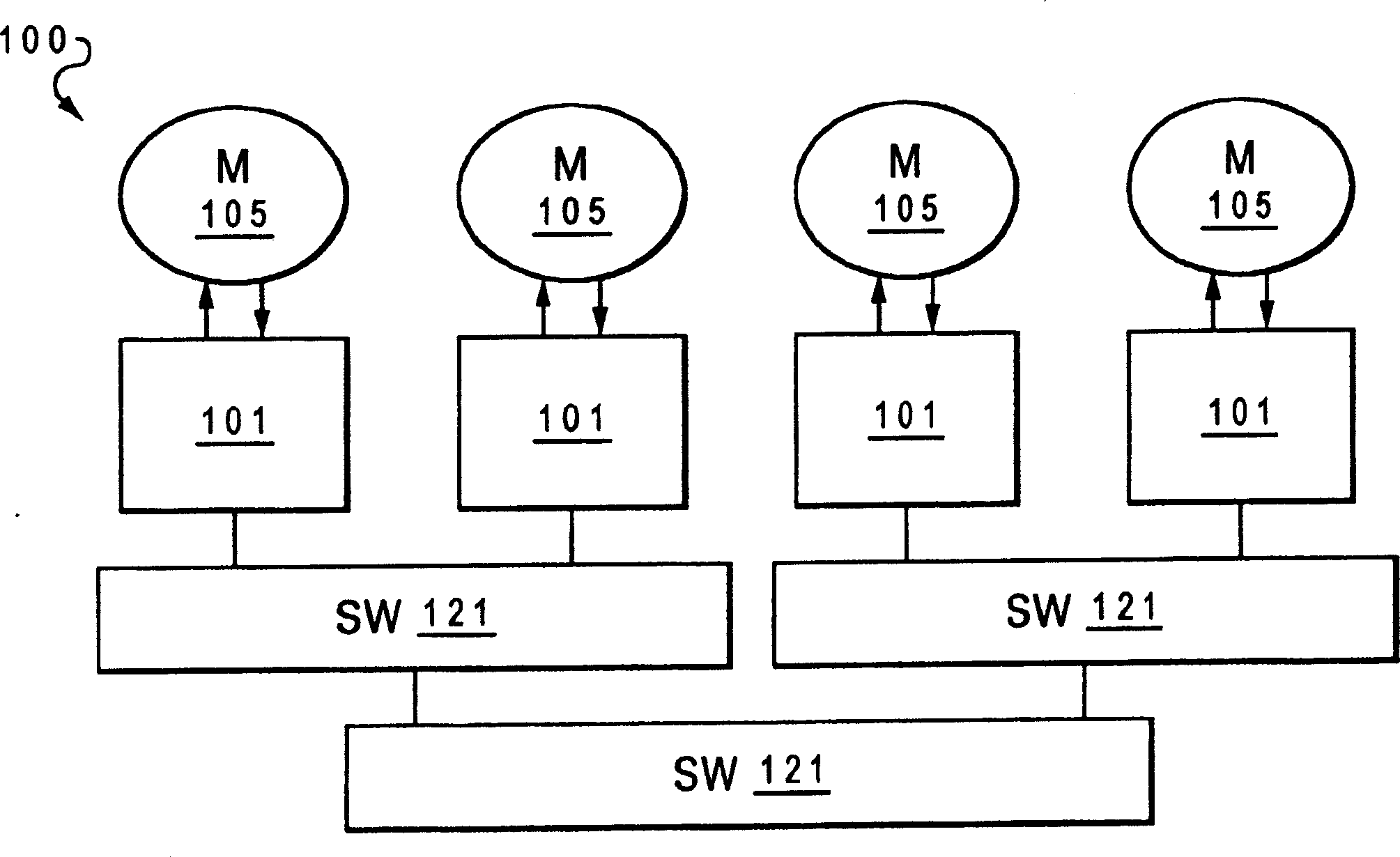

[0023] The present invention introduces a novel processor block comprising two interconnected multi-chip modules (MCMs). This processor block is in turn designed to connect to other processor blocks on the system rack to provide much larger business and technical systems. Additionally, unlike prior art multi-chip configurations, routing logic is provided within the processors of this processor block to enable the processors to expose all memory capabilities, thereby enabling more thorough use of the available memory bandwidth.

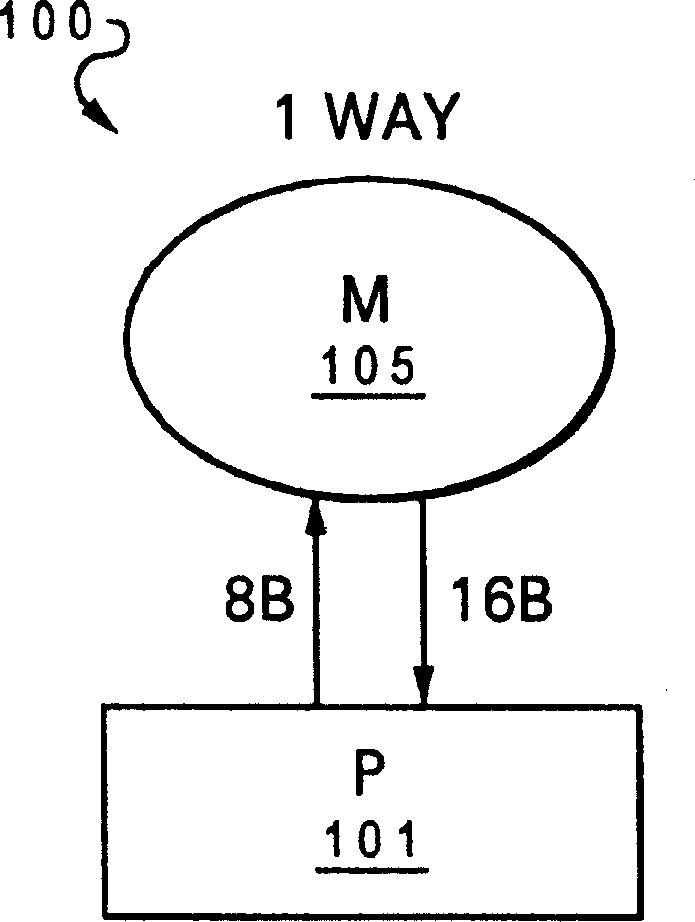

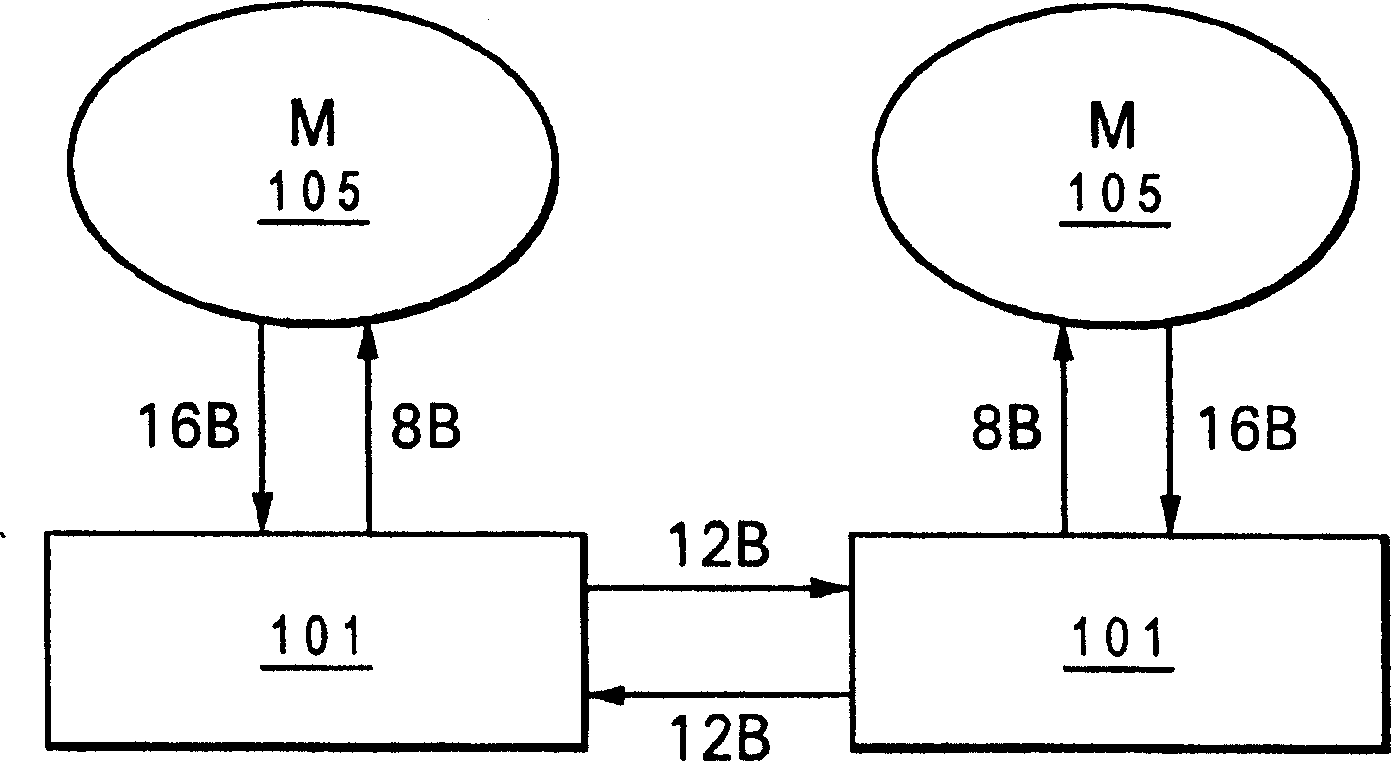

[0024] Therefore, the present invention is implemented in a processor configuration in which each processor has been able to fully use the distributed memory without any memory mapping relationship (ie fully-aggregate model). One way this can be done is to reconfigure a two-way system where the processors are connected by a 16-byte bus. With a wider bus, each processor in a two-way or larger system has full access to the block of memory coupled to any...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More