Splittable multiplier for efficient mixed-precision DSP

A multiplier and multiplication technology, which is applied to calculations using number system representation, instruments, calculations using non-contact manufacturing equipment, etc., can solve problems such as inability to generate correct products

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] Detailed Description of Preferred Embodiments

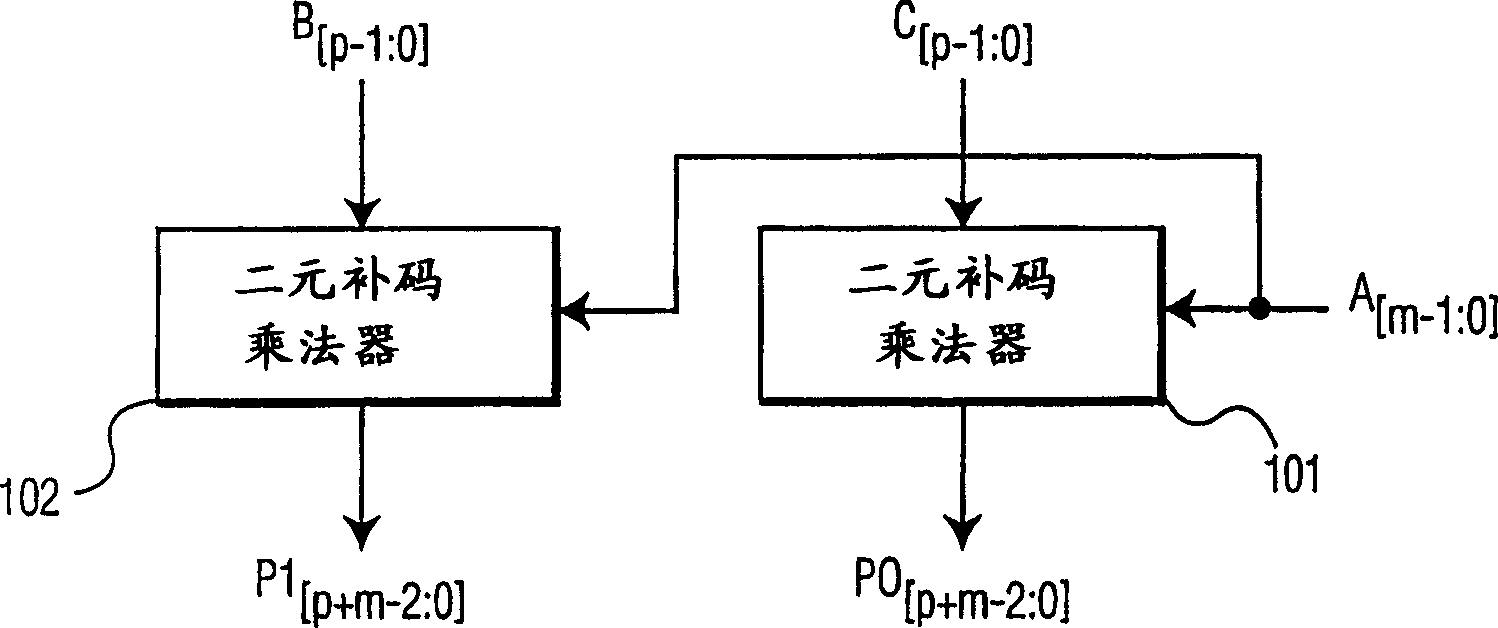

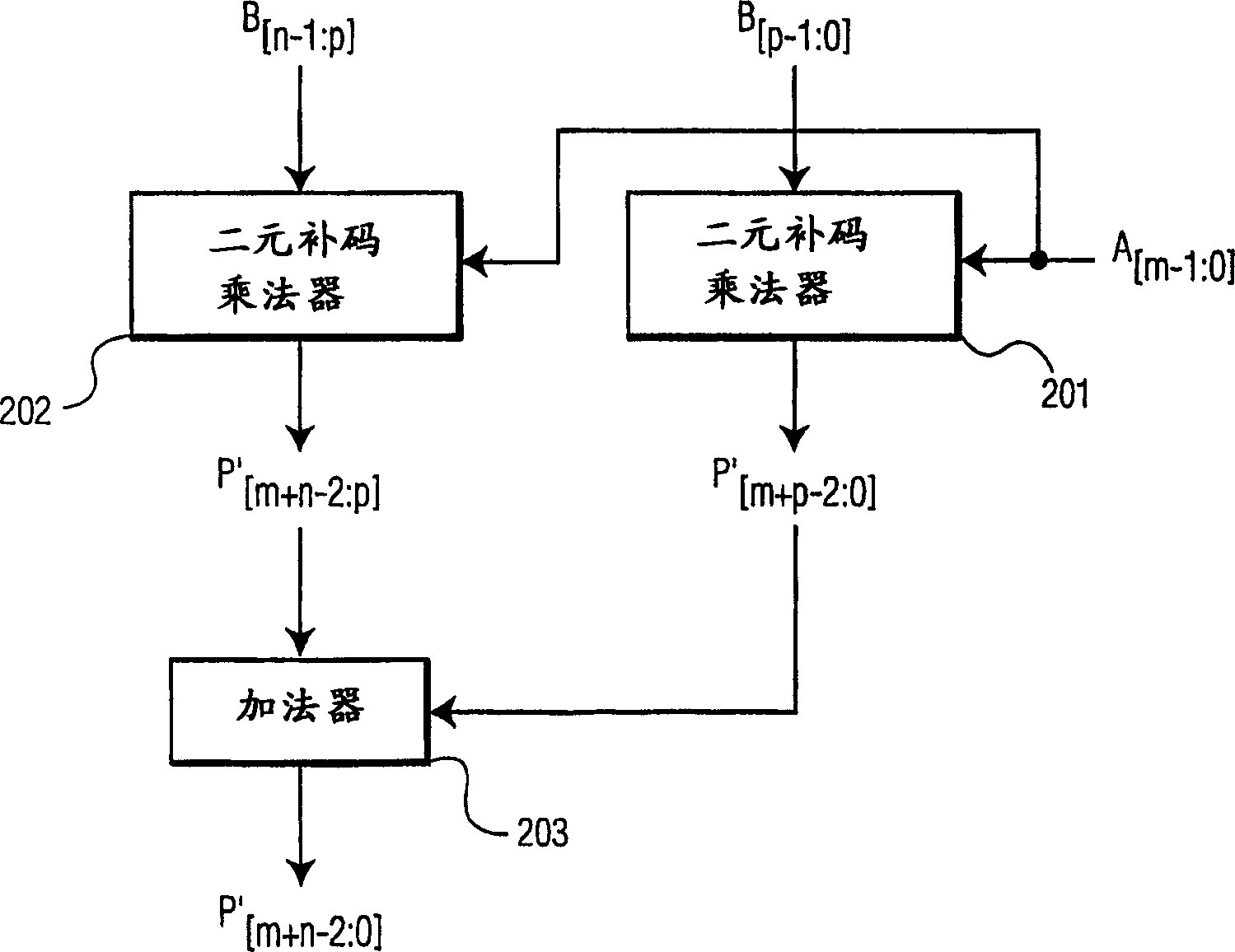

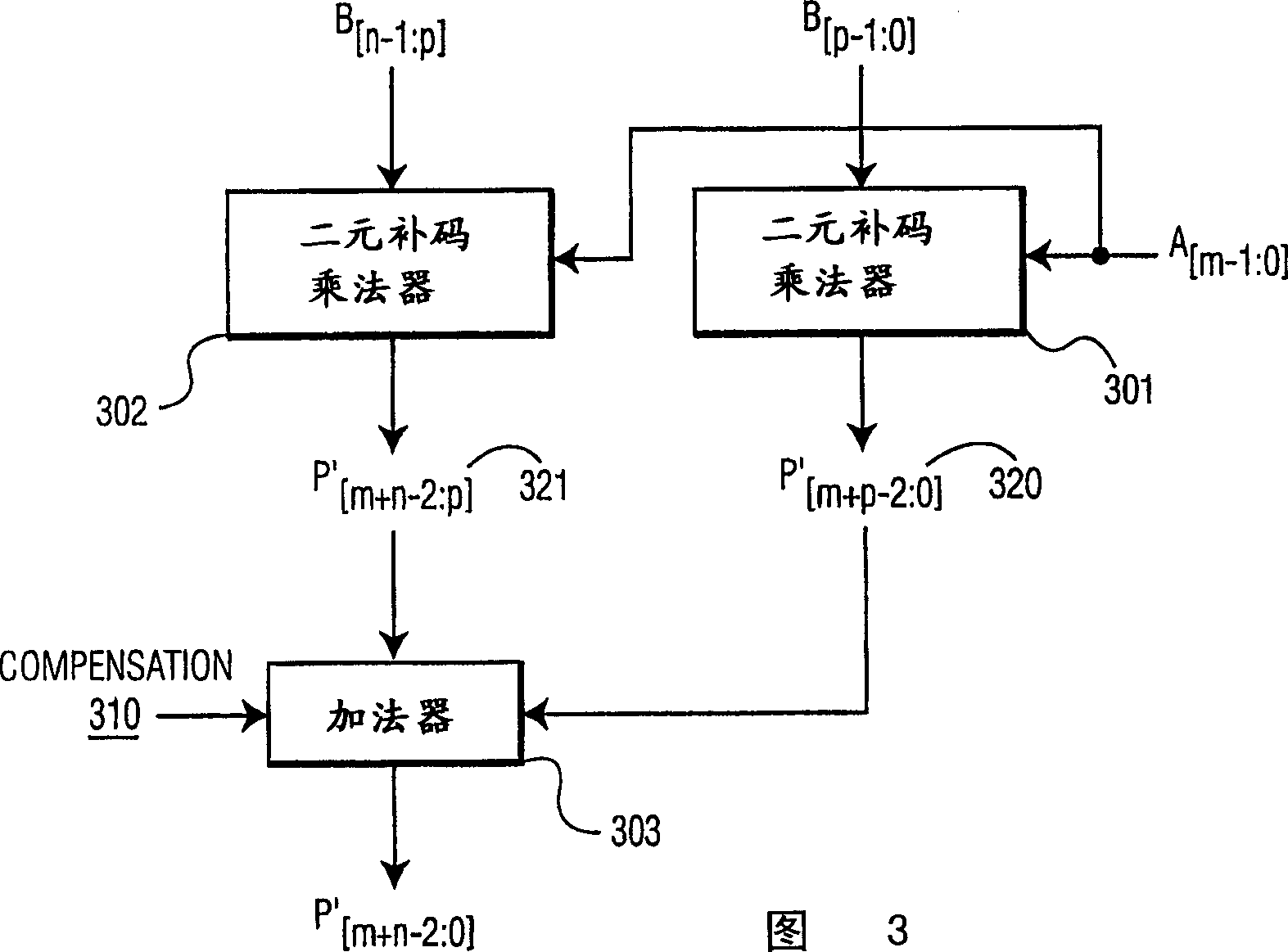

[0017] This invention discusses methods for implementing partitioned two's complement multipliers to provide an efficient degree of subword parallelism for multiplication resources. As an example, it is hoped that the configuration of the double multiplier can be realized as figure 1 Two parallel operations of lower precision shown. And hopefully those same multipliers can support a full precision operation like figure 2 shown in .

[0018] For the VSB DFE example discussed above, three 4x16 multiplier arrays can provide 3 simultaneous multiplications, or one 12x16 multiplication. Therefore, this split multiplier is an important tool for implementing resource and power efficient shared hardware programmable resources.

[0019] The split multiplier implementation will be discussed below for the case of two separate two's complement multipliers. refer to figure 1 , two m-by-p two's complement multipliers 101 and 102 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More