Method of forming narrow trenches in semiconductor substrates

A semiconductor and substrate technology, applied in the field of forming narrow trenches, can solve problems such as helping, and achieve the effect of reducing gate charges

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

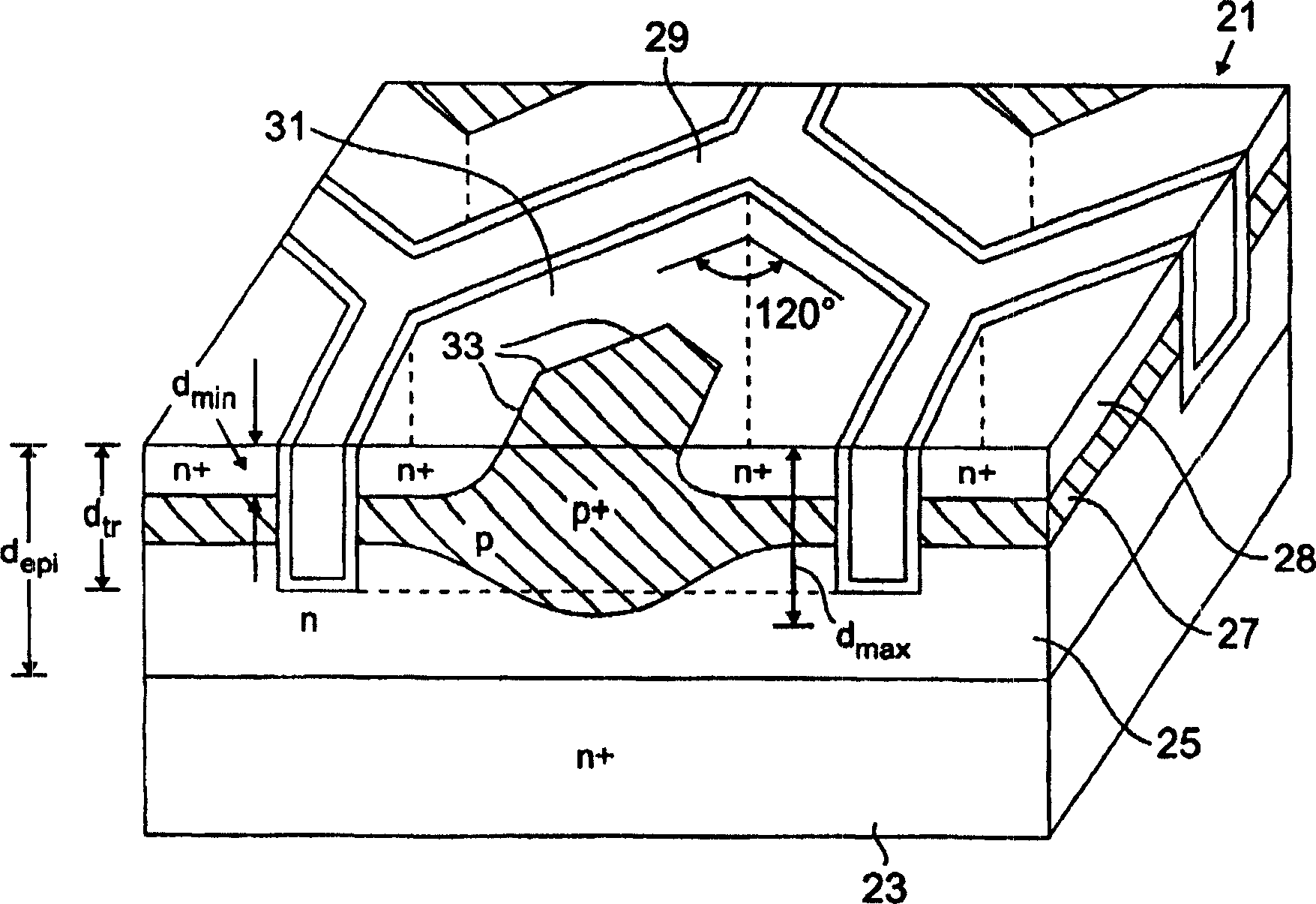

Embodiment Construction

[0022] The present invention is described more fully hereinafter with reference to the accompanying drawings, in which preferred embodiments of the invention are shown. This invention may, however, be embodied in various forms and should not be construed as limited to the embodiments set forth herein.

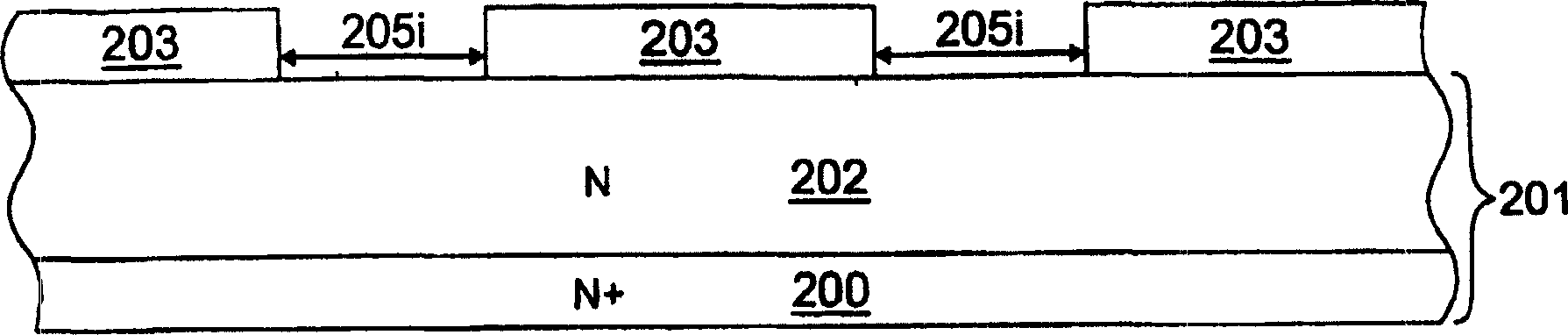

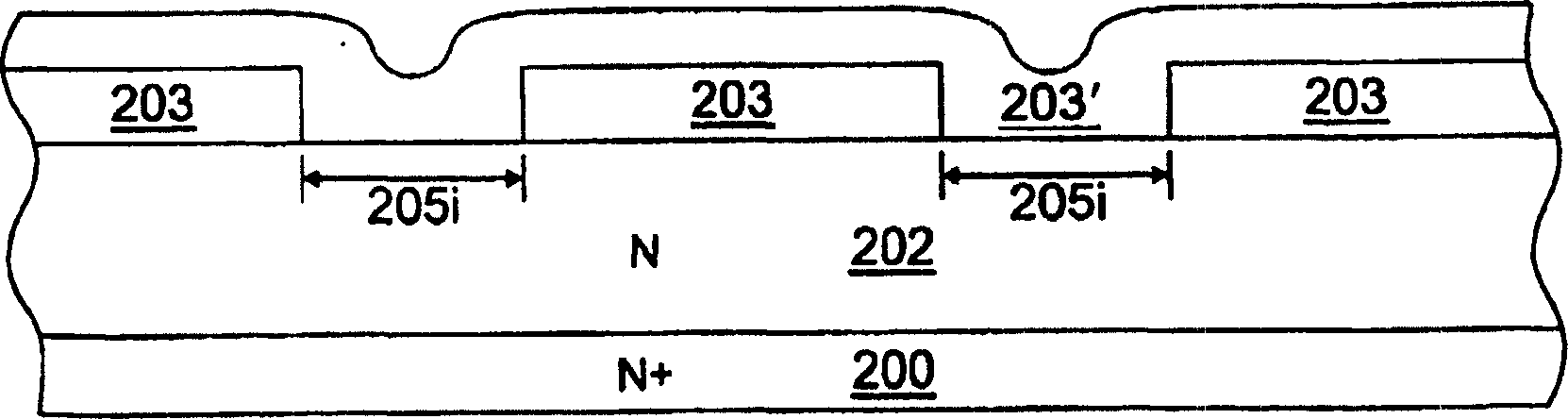

[0023] According to an embodiment of the present invention, a semiconductor substrate is a preferred substrate. The semiconductor substrate may be any substrate in the known technology, including elemental semiconductor substrates such as silicon or germanium, or compound semiconductor substrates such as GaAs, AlAs, GaP, InP, GaAlAs and the like. A semiconductor substrate can be monocrystalline, polycrystalline and / or amorphous, and it can be doped or undoped. according to Figures 2A to 2D Specific examples of semiconductor substrates are presented. refer to Figure 2A , shows a silicon semiconductor substrate 201 consisting of an N+ doped silicon wafer 200 having an N dope...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More