Power-up circuit semiconductor memory device

A memory and semiconductor technology, applied in the field of power-on circuits of semiconductor memory devices, can solve problems such as threshold voltage reduction, unstable operation of semiconductor memory devices, abnormal power-on signal pwrup and early reset

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

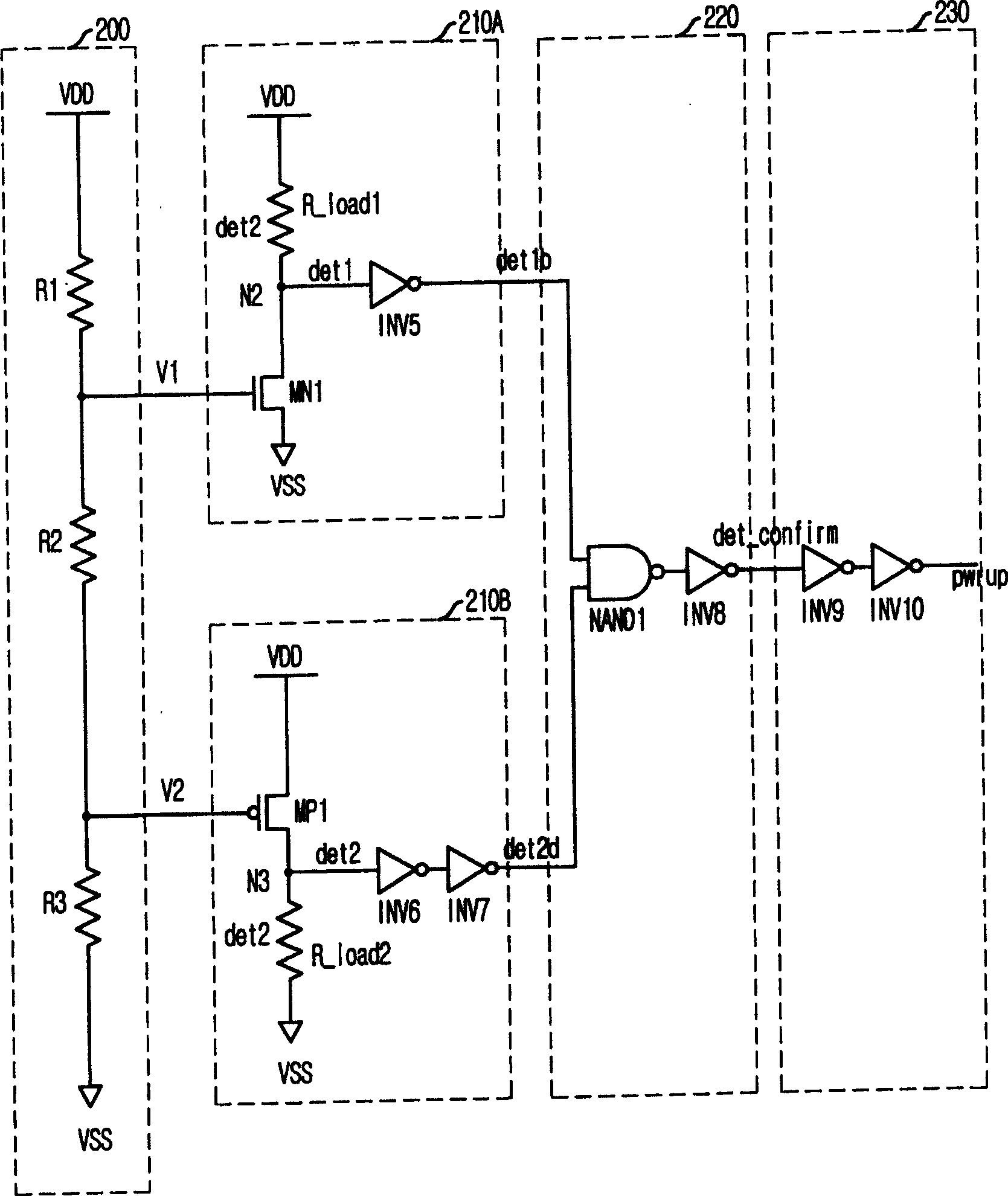

[0029] Hereinafter, a power-on circuit according to the present invention will be described in detail with reference to the accompanying drawings.

[0030] Fig. 3 is a schematic circuit diagram illustrating a power-up circuit according to a first preferred embodiment of the present invention.

[0031] As shown in the figure, the power-on circuit includes a power voltage level follower unit 200 , a first power voltage detection unit 210A, a second power voltage detection unit 210B, a summing unit 220 and a buffer unit 230 .

[0032] The supply voltage level follower unit 200 generates a first bias voltage V1 and a second bias voltage V2 which linearly increase or decrease in proportion to a voltage level of a supply voltage VDD.

[0033] The first power supply voltage detection unit 210A is used to detect that in response to the first bias voltage V1, the voltage level of the power supply voltage VDD will change to a threshold voltage corresponding to the threshold voltage of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More