Logic verification system and method

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The core of the present invention is to design a shared platform for simulation verification and hardware system verification for logic, to make it suitable for simulation verification and hardware system verification through different interface conversion, and to use the same kind of incentive data for the two stages of verification.

[0045] In order to enable those skilled in the art to better understand the solution of the present invention, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

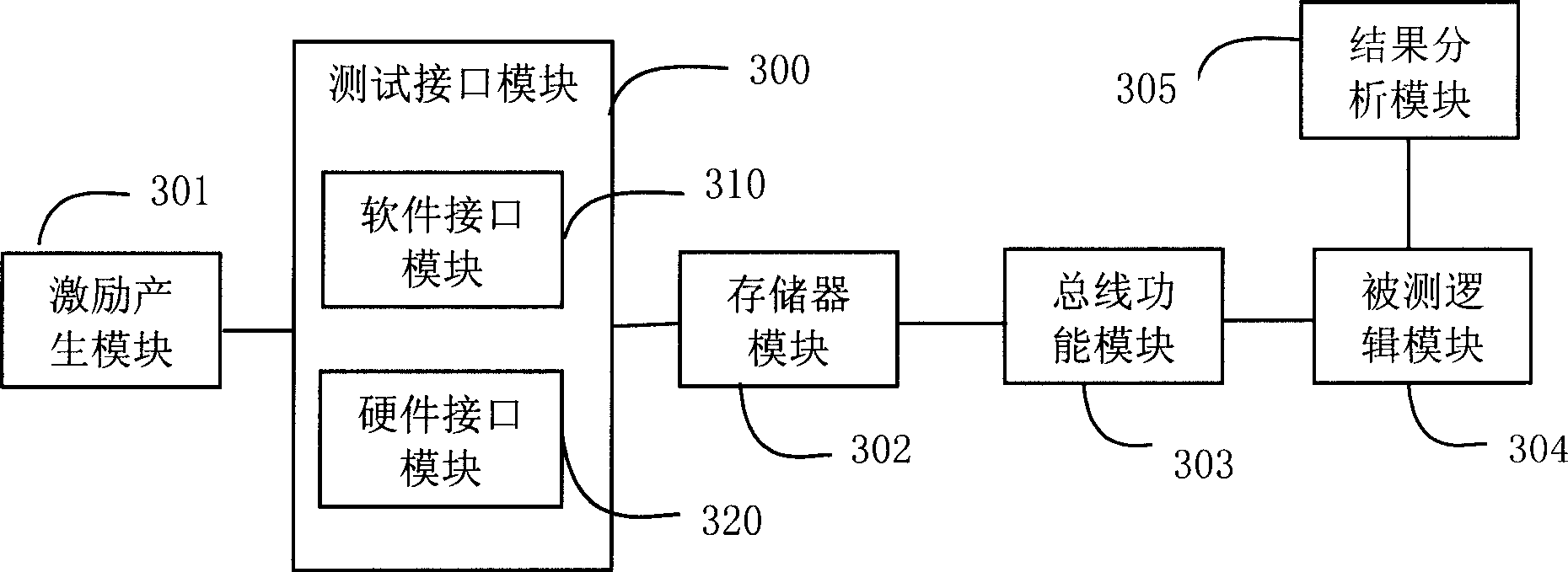

[0046] refer to image 3 , image 3 It is the system networking diagram of the present invention:

[0047] It includes: a stimulus generation module 301 , a test interface module 300 , a memory module 302 , a bus function module 103 , a tested logic module 304 and a result analysis module 305 . in,

[0048] The stimulus generation module 301 is used to generate stimulus data required for testing; it...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More