Multi-height finfets field effect trabsistor

A fin and height technology, applied in the field of fin field effect transistors, to achieve the effect of sacrificing yield and high channel width quantization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

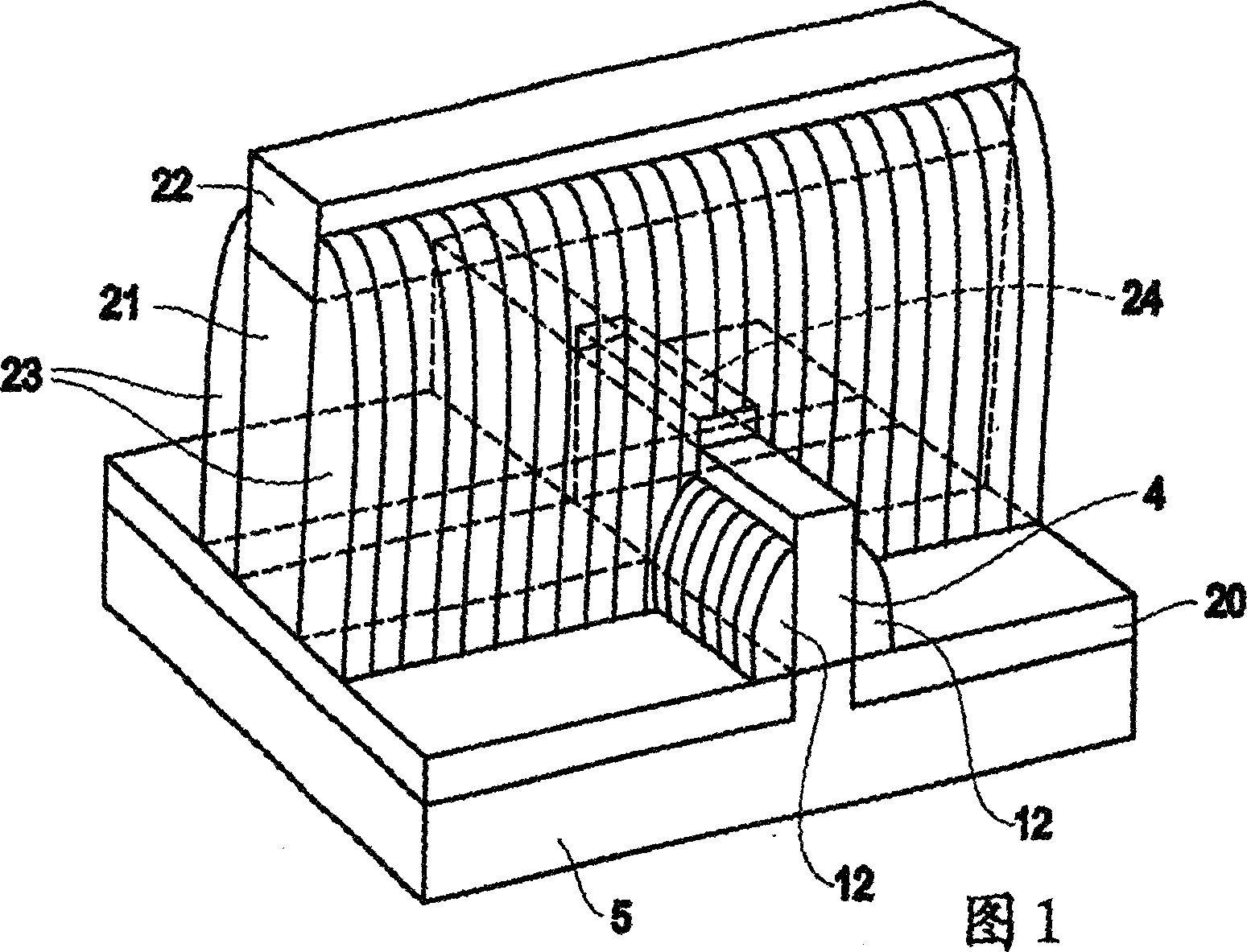

[0026] A group of analog-like circuits that are logically such as sense amplifiers, latches, etc. and SRAM cells. Therefore, the performance of different circuits within the chip can be tuned by changing the channel width of one or more FETs within the device. This allows designers to change the performance of different logic circuits where needed on the chip.

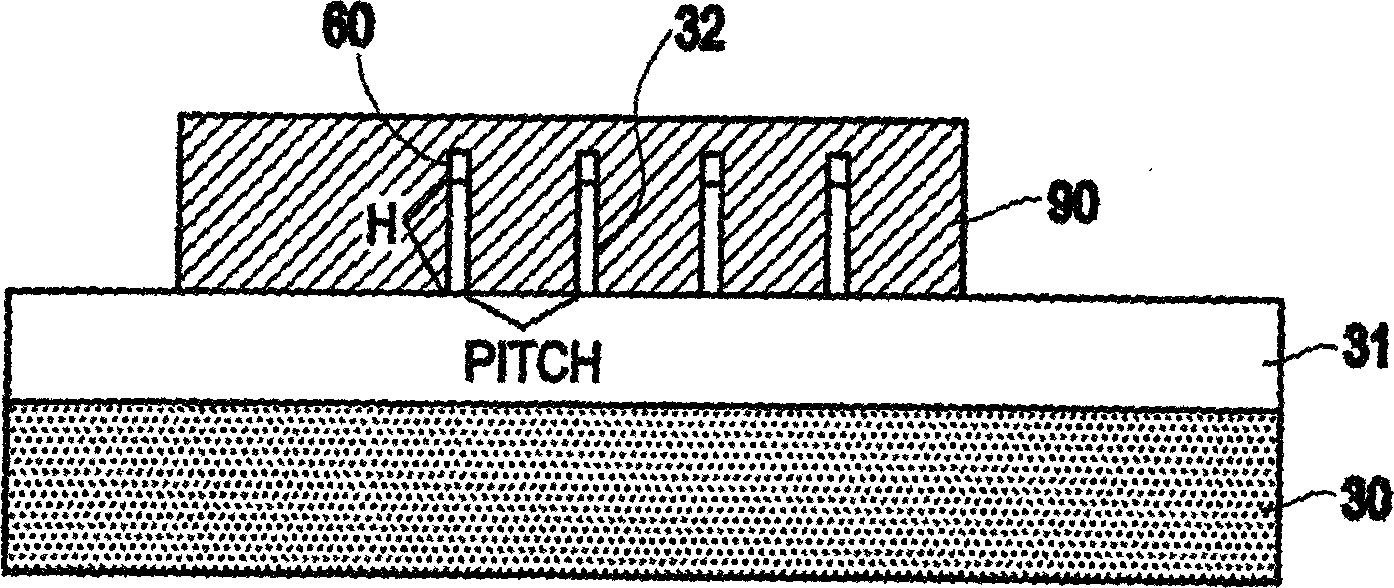

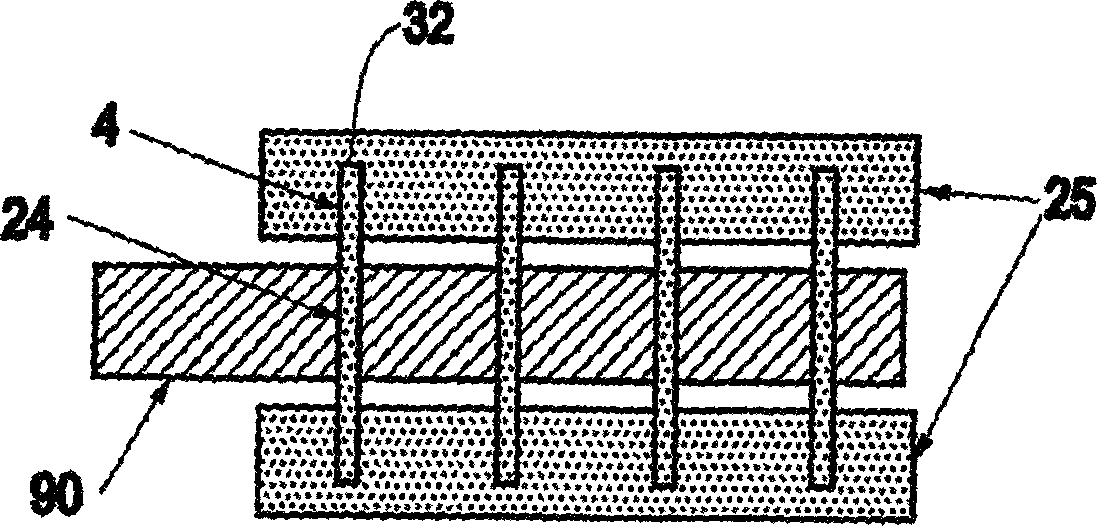

[0027] For FinFET structures, the channel width is proportional to the fin height because, in FinFET devices, the channel width is vertical. Since both sides of the fin are exposed to but insulated from the gate, the channel width is effectively twice the area created by the fin height (multiplied by the fin length). Thus, by increasing or decreasing the fin height (for a given fin length), the channel width (the channel surface area exposed but insulated from the gate) is correspondingly increased or decreased. The present invention provides a method to fabricate FinFETs with different fin heights (channel widths) ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More