Chip general detector and its structure method

A general-purpose testing and chip technology, applied in measuring devices, electronic circuit testing, single semiconductor device testing, etc., to avoid repeated development, reduce difficulty, save time and cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

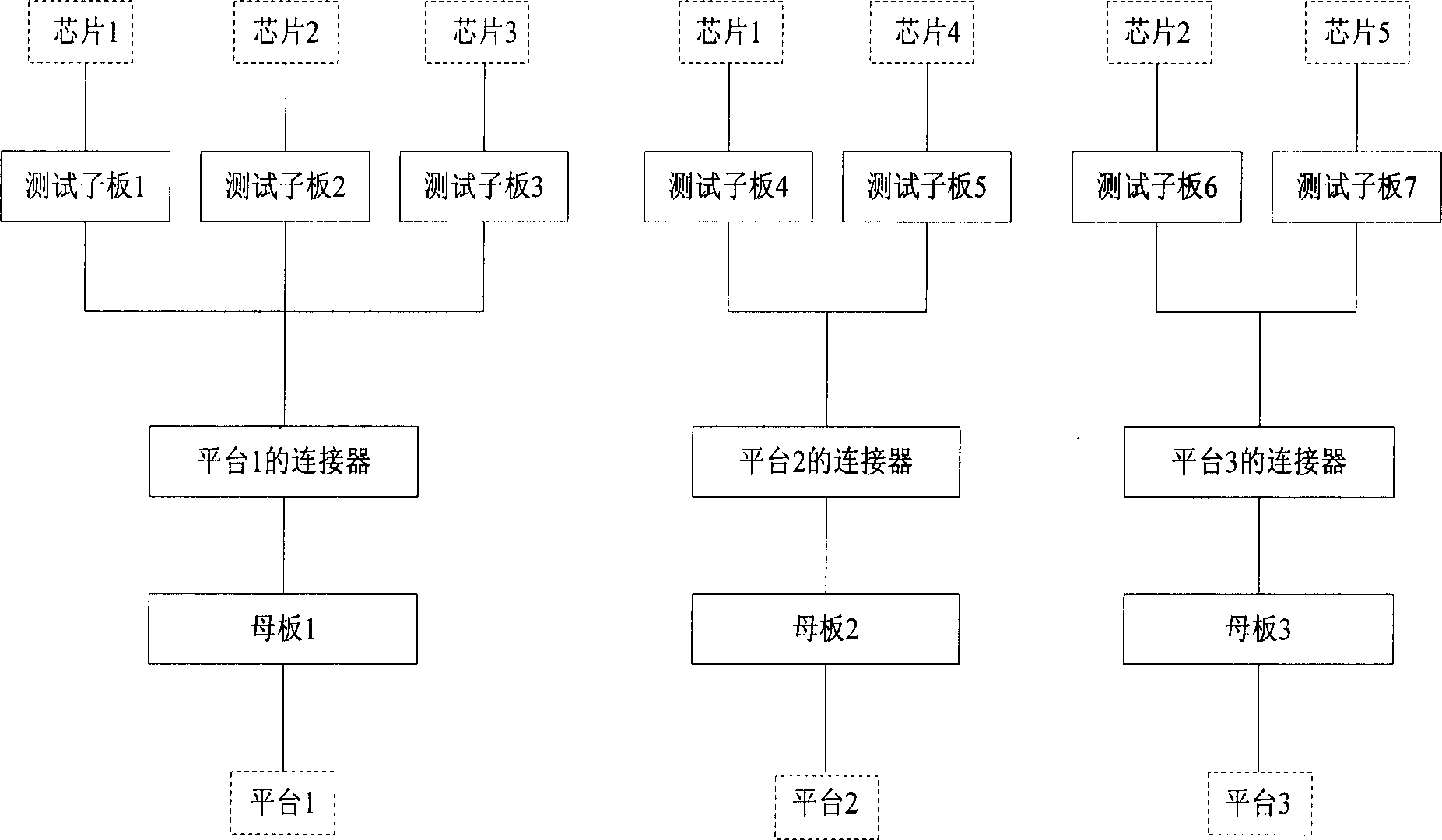

[0064] like Image 6 As shown, the universal interface connector 2 includes 16 digital interface modules 21, respectively denoted by "DIGxx", 2 analog interface modules 22, respectively denoted by "ANAxx", and 4 power interface modules 23, respectively denoted by "DPSxx" express. The digital interface module 21 , the analog interface module 22 and the power interface module 23 have fixed positions, and the fixed positions are determined by the unified interface standard defined in this embodiment. In this way, the universal interface connector 2 can connect the digital signals, analog signals and power signals on the channels of the test daughter board 3 and the test motherboard 1 respectively.

[0065] In this embodiment, the universal interface connector 2 further includes four control switch interface modules 24, which are denoted by "UTIxx". The control switch interface modules 24 have fixed positions matching the unified interface standard and are used for connecting to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More