Nonvolatile memory cell having floating gate, control gate and separate erase gate, an array of such memory cells, and method of manufacturing

a technology of floating gate and memory cell, which is applied in the direction of semiconductor devices, electrical devices, transistors, etc., can solve the problems of affecting the design of a single member

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

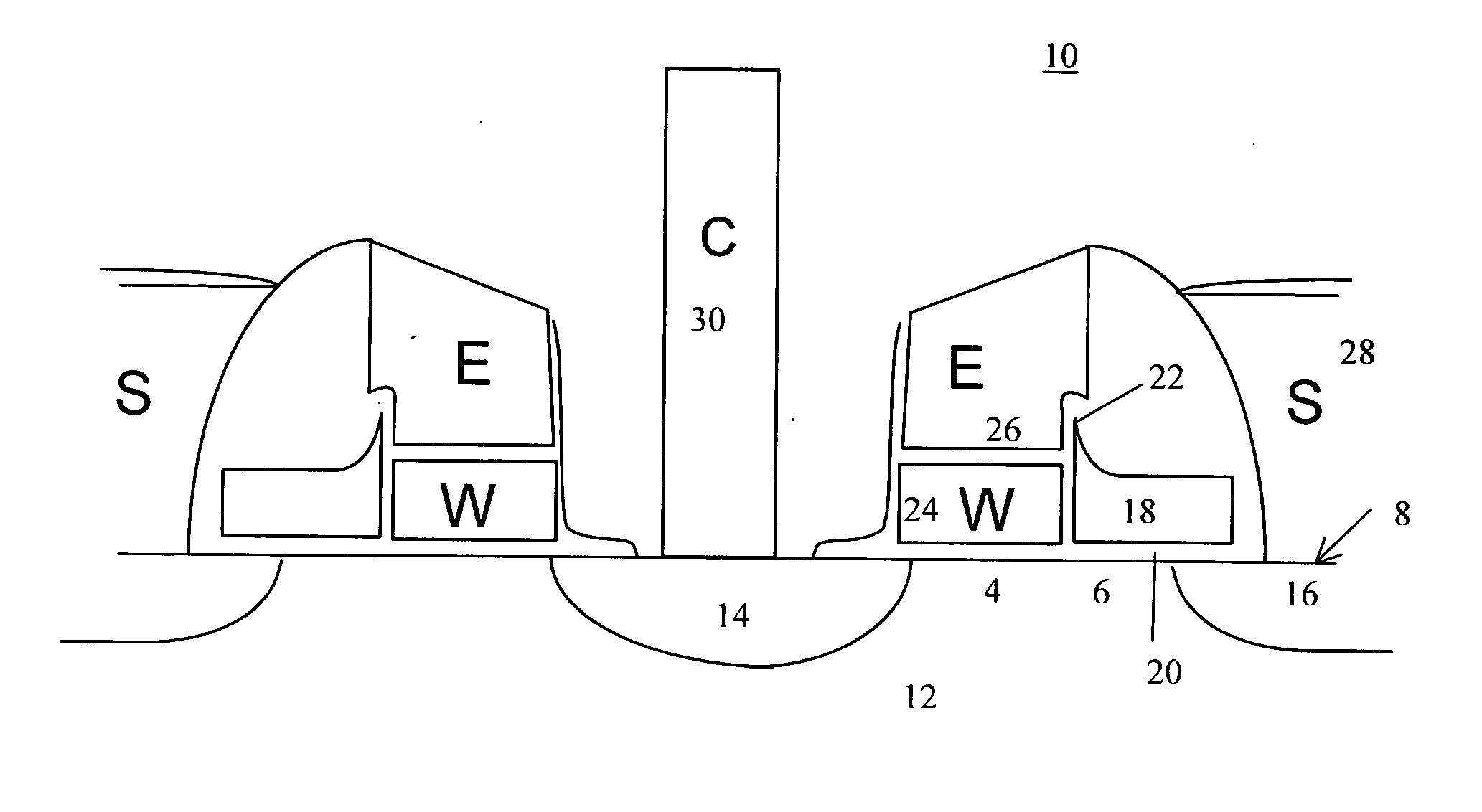

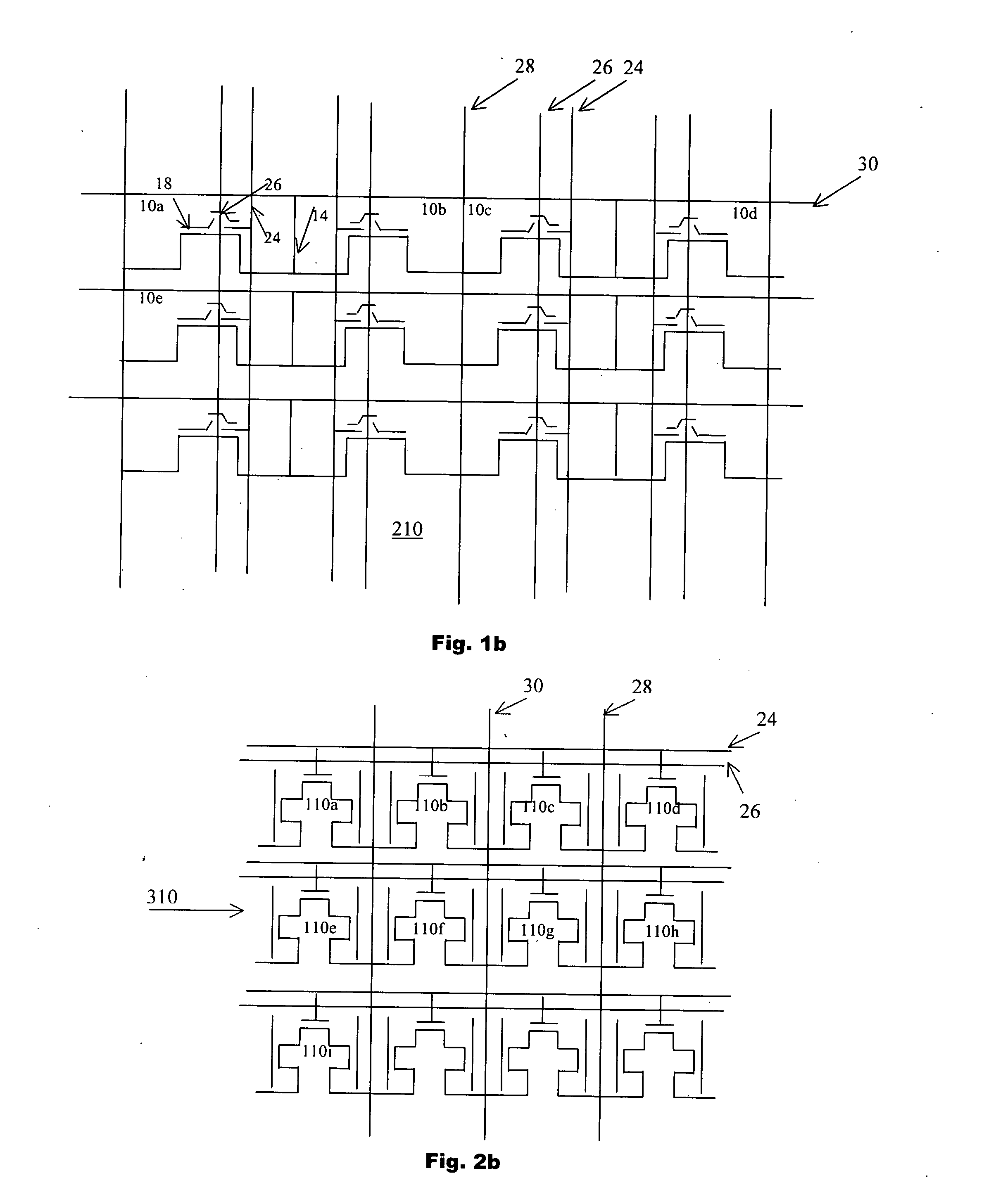

[0011] Referring to FIG. 1A, there is shown a cross-sectional view of a nonvolatile memory cell 10 of the present invention. Similar to the cell shown and described in U.S. Pat. No. 5,029,130, whose disclosure is incorporated herein in its entirety by reference, the memory cell 10 is formed in a substantially single crystalline semiconductor substrate 12, such as silicon. The substrate 12 is of a first conductivity type. The substrate 12 also has a planar surface 8. Within the substrate 12 is a first region 14 of a second conductivity type. A second region 16 of a second conductivity type is spaced apart from the first region 14. Between the first region 14 and the second region 16 is a channel region. The channel region comprises two portions: a first portion 4 which is adjacent to the first region 14 and a second portion 6 which is adjacent to the second region 16. Spaced apart from the substrate 12 is a floating gate 18 which is on a insulating layer 20. The floating gate 18 is p...

second embodiment

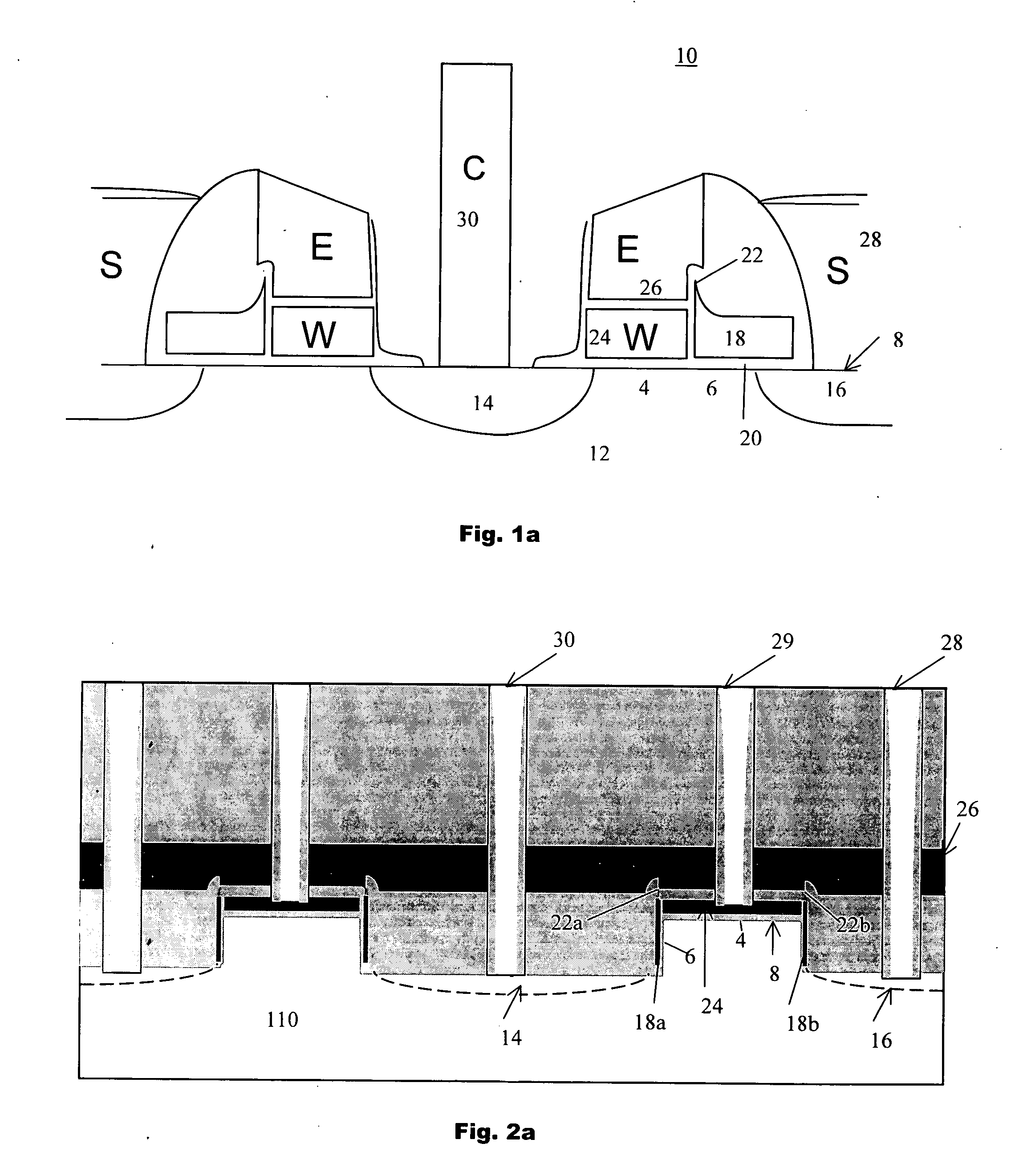

[0025] Referring to FIG. 2A, there is shown a nonvolatile memory cell 110 of the present invention. The cell 110 is similar to the cell 10 shown in FIG. 1A, with the exception that each cell 110 has two floating gates and operates bidirectionally. In addition, the cell 110 has a control gate 24 and a separate erase gate 26 for each cell 110. More specifically, each cell 110 has a first region 14 and a second region 16 spaced apart from one another with a channel region therebetween, in a substrate 12. Each of the first region 14 and a second region 16, however, lies in a trench in the substrate 12 with a portion of the channel region being a planar surface 8. Each of the trenches has a bottom and a side wall with the first region 14 and the second region 16 being at the bottom of the trench. A first floating gate 18A and a second floating gate 18B are along the side of the sidewalls, spaced apart therefrom and insulated therefrom. Thus, each of the floating gate 18A and 18B controls...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More