High polarization ferroelectric capacitors for integrated circuits

a high-polarization, ferroelectric capacitor technology, applied in the direction of capacitors, semiconductor devices, electrical apparatus, etc., can solve the problems of destructive read operation, achieve high switching polarization, facilitate ferroelectric switching properties, and avoid read operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

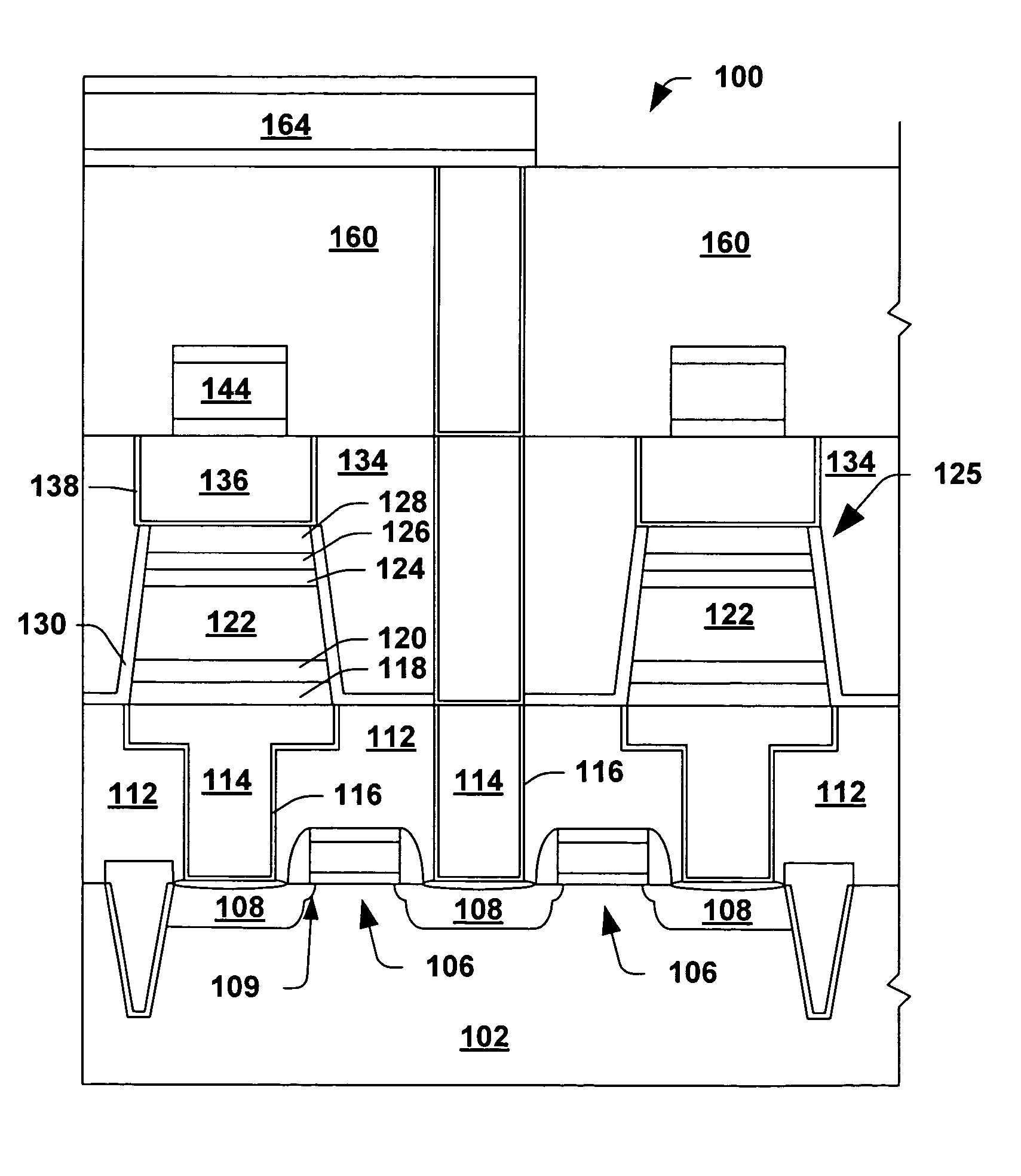

[0021] The present invention will now be described with reference to the accompanying drawings in which like numbered elements represent like parts. The present invention can be used to fabricate stand-alone FeRAM devices or FeRAM devices integrated into a semiconductor chip that has many other device types.

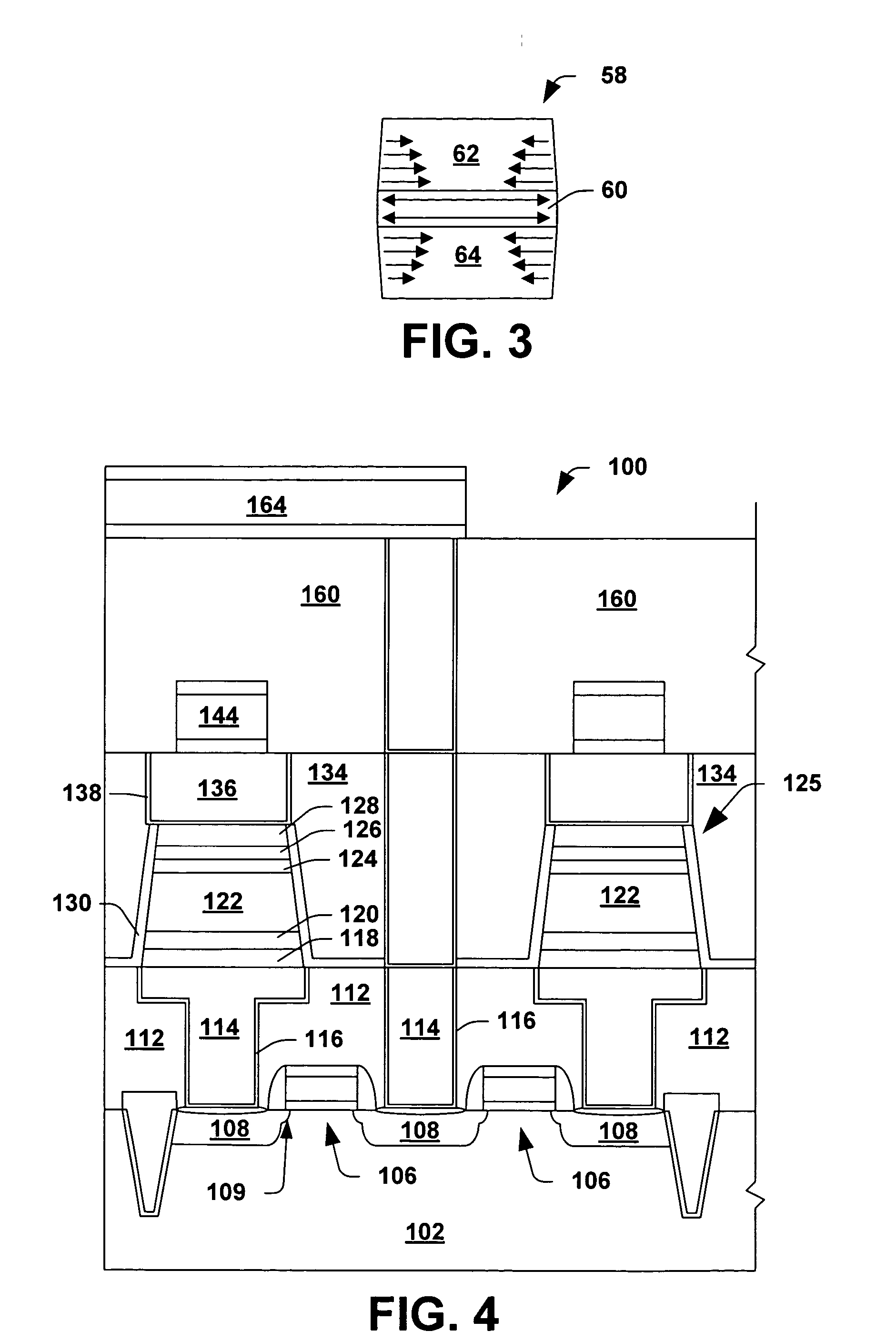

[0022]FIG. 3 provides a schematic illustrating how stresses are applied according to the present invention to reorient the domains of a ferroelectric core 60. A stack 58 comprising the ferroelectric core 60, a material 62 above the ferroelectric core 60 and a material 64 below the ferroelectric core 60. The materials are stacked in the z-direction. One of, and preferably both of, the materials 62 and 64, have a larger coefficient of thermal expansion (CTE) than the ferroelectric core 60. As the materials are cooled below the temperatures at which they were formed, the materials 62 and 64 shrink faster than the ferroelectric core 60 and, through shear stresses, exert a compressiv...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| Curie temperature | aaaaa | aaaaa |

| Curie temperature | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com