Methods for making nearly planar dielectric films in integrated circuits

a dielectric film, integrated circuit technology, applied in the direction of electrical apparatus, semiconductor devices, semiconductor/solid-state device details, etc., can solve the problems of not only relatively expensive but also quite time-consuming chemical-mechanical planarization process, add undesirable features, such as notches, to desired features, and achieve the effect of improving the effective dielectric constant, facilitating the formation of intermetal dielectric layers, and improving the ability to prevent shorting and crosstalk

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The following detailed description, which references and incorporates the above-identified Figures, describes and illustrates specific embodiments of the invention. These embodiments, offered not to limit but only to exemplify and teach the invention, are shown and described in sufficient detail to enable those skilled in the art to implement or practice the invention. Thus, where appropriate to avoid obscuring the invention, the description may omit certain information known to those of skill in the art.

First Exemplary Method of Forming Nearly Planar Dielectric Films

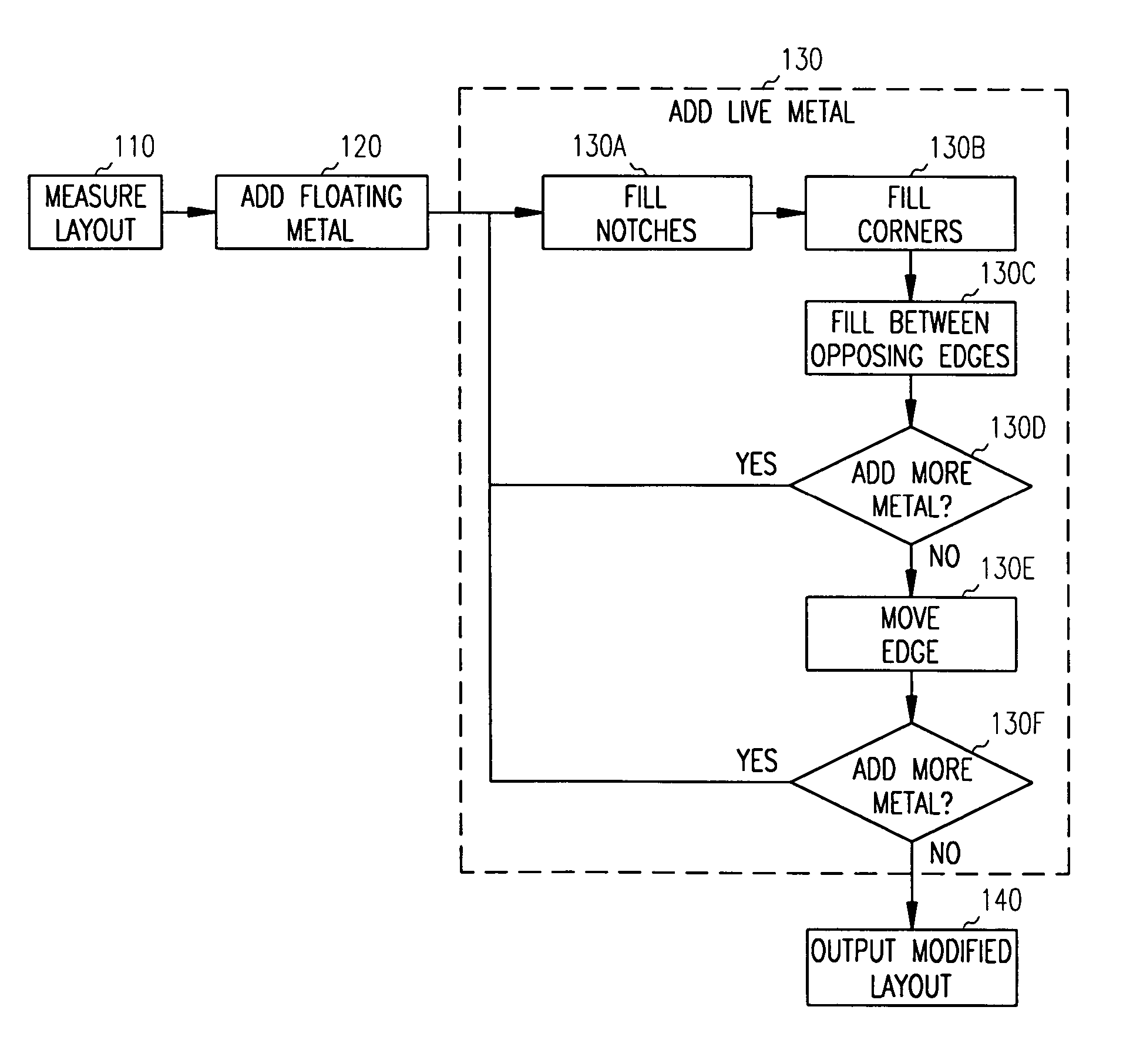

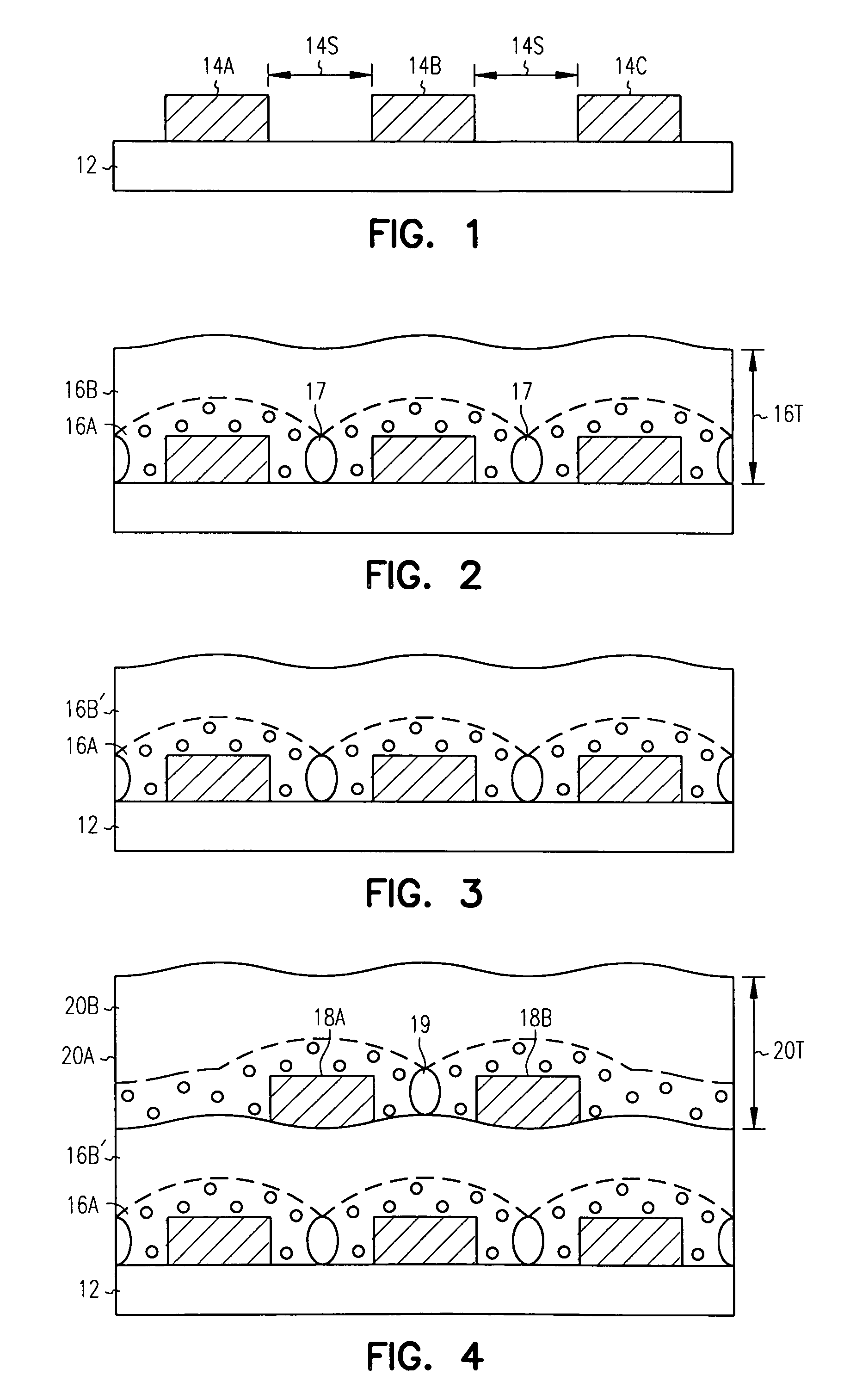

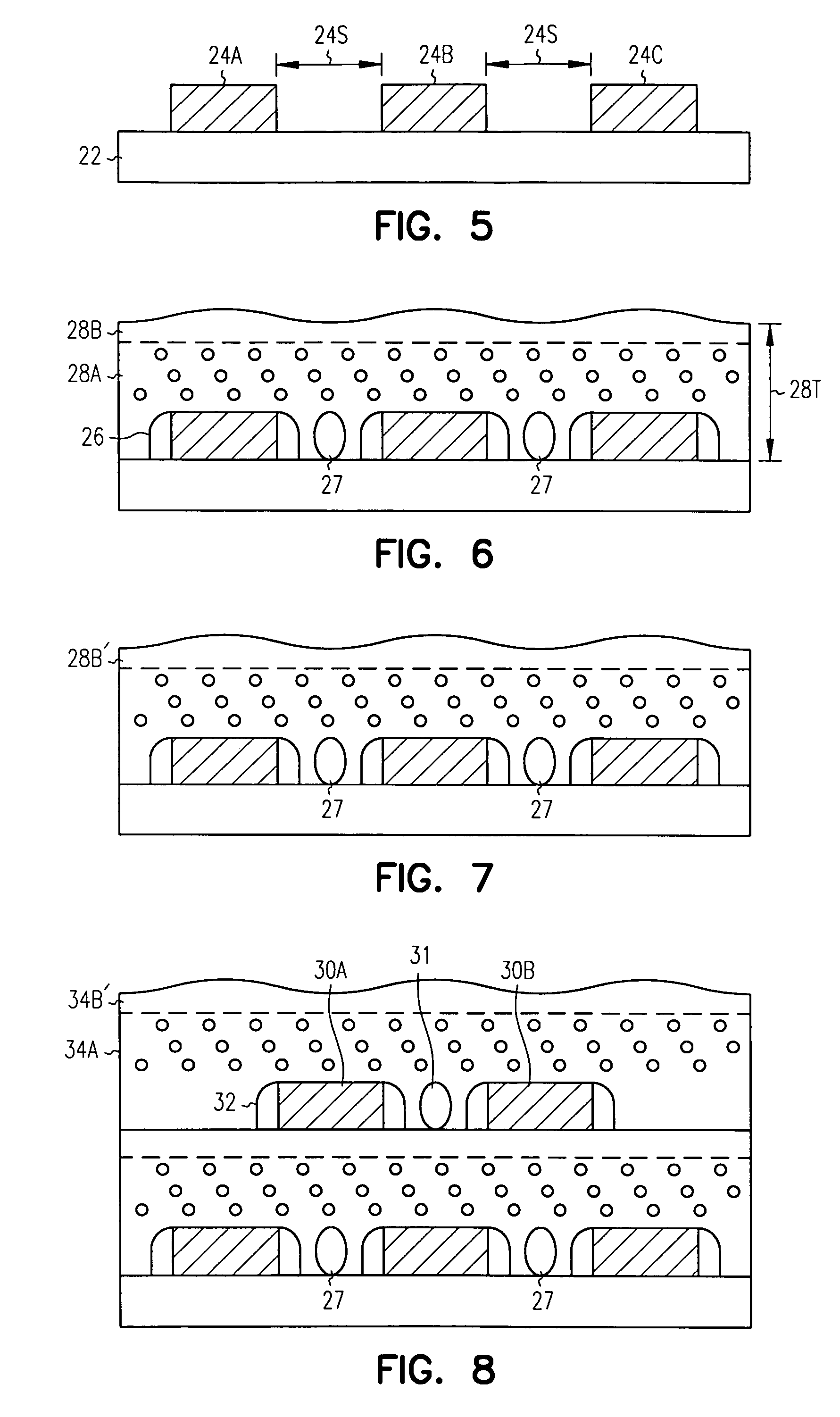

[0030]FIGS. 1-4 show a number of exemplary integrated-circuit assemblies, which taken collectively and sequentially, illustrate an exemplary method of making nearly planar or quasi planar dielectric films, or layers, within the scope of the present invention. As used herein, a quasi planar film is globally planar with local nonplanarities having slopes less than or equal to 45 degrees and depths less than the t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com