Semiconductor storage device and method of controlling semiconductor storage device

a semiconductor storage device and storage device technology, applied in the direction of memory address/allocation/relocation, instruments, computing, etc., can solve the problems of inefficient parallel processing of the chips, etc., to prevent deterioration in write/read performance of the device, reduce the time each chip is in an idle state, and prevent performance deterioration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033]An embodiment of the present invention will be described with reference to the accompanying drawings.

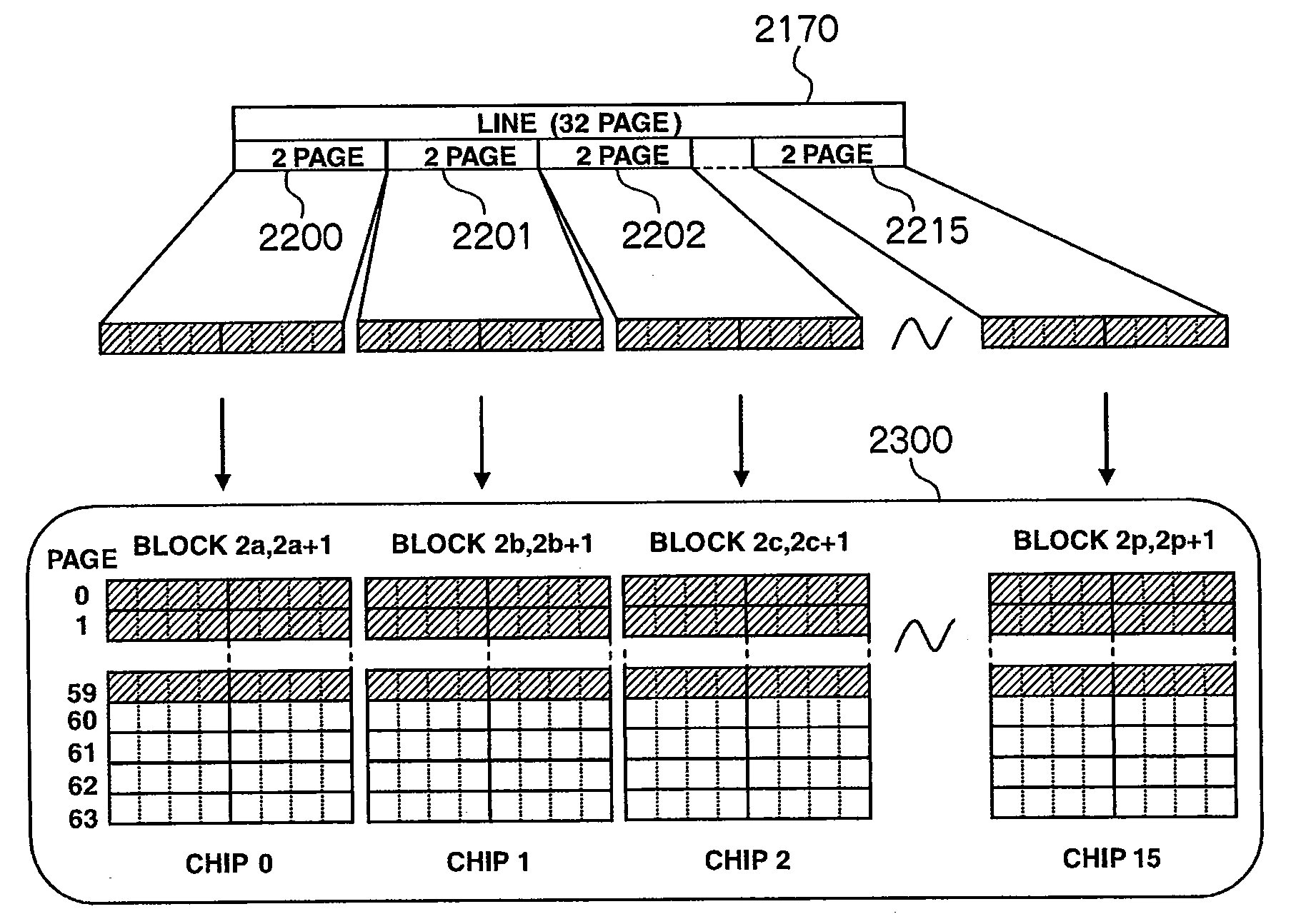

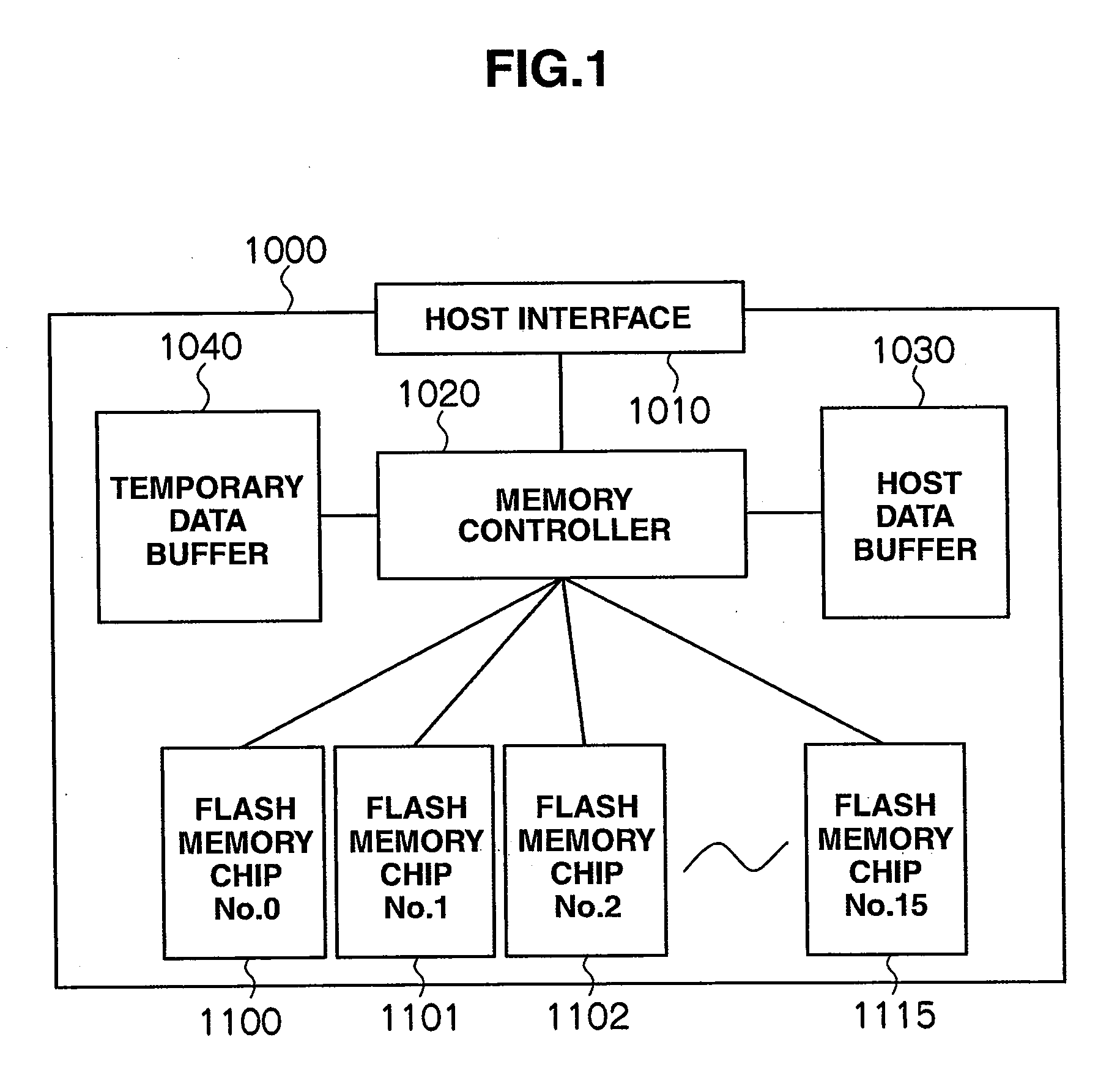

[0034]FIG. 1 is a diagram briefly showing an internal configuration for a semiconductor storage device 1000 that utilizes the invention. The semiconductor storage device 1000 is composed of a host interface 1010, a memory controller 1020, a host data buffer 1030, a temporary data buffer 1040, and plural (e.g., 16) flash memory chips 1100 to 1115.

[0035]The host interface 1010 is an interface mechanism connected to an external host(s) (not shown in the drawing), and transmits data stored in the flash memory chips 1100 to 1115 to the host and receives write data to be stored in the flash memory chips 1100 to 1115 from the host in response to read / write request commands from the host.

[0036]Incidentally, the host specifies a logical storage position for the data requested to be subject to read / write by using a logical address (hereinafter referred to as “LBA (Logical Block Address)”...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More