Out-of-order execution microprocessor with reduced store collision load replay reduction

a microprocessor and store technology, applied in the field of out-of-order execution microprocessors, can solve the problems of large penalty for processing load instruction, large replay cost, and load instruction to receive incorrect data, so as to reduce the likelihood, reduce the likelihood, and reduce the likelihood

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

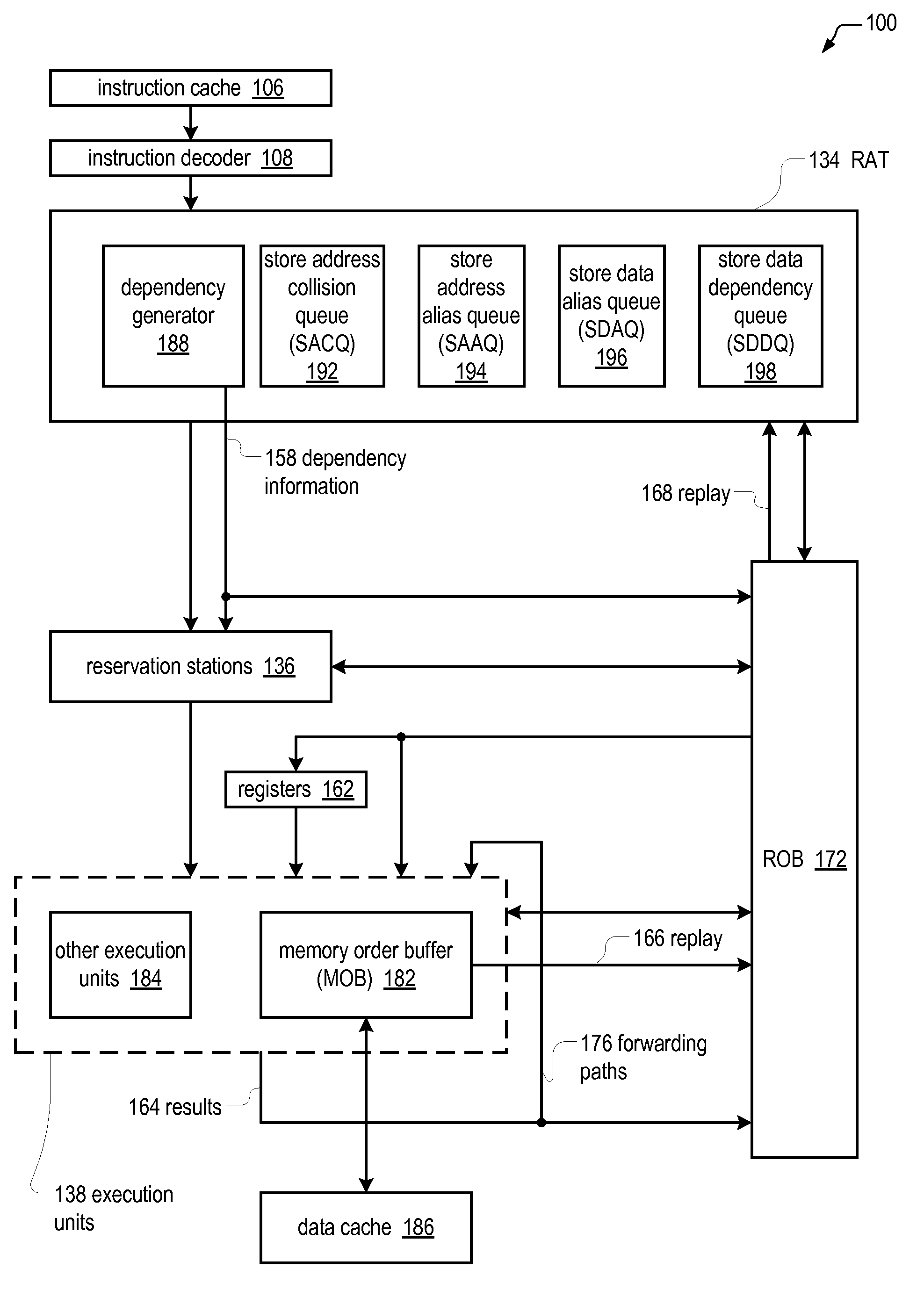

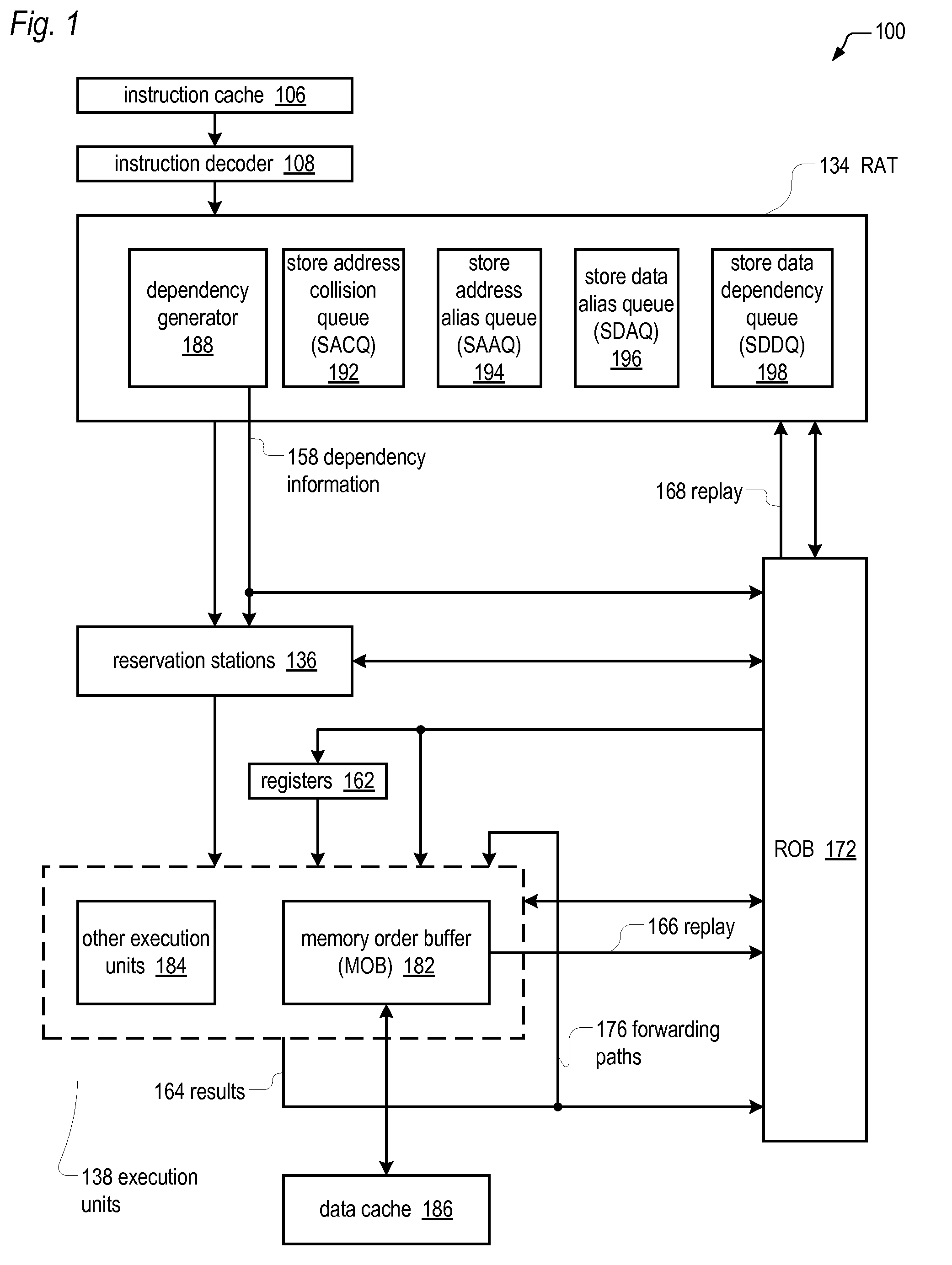

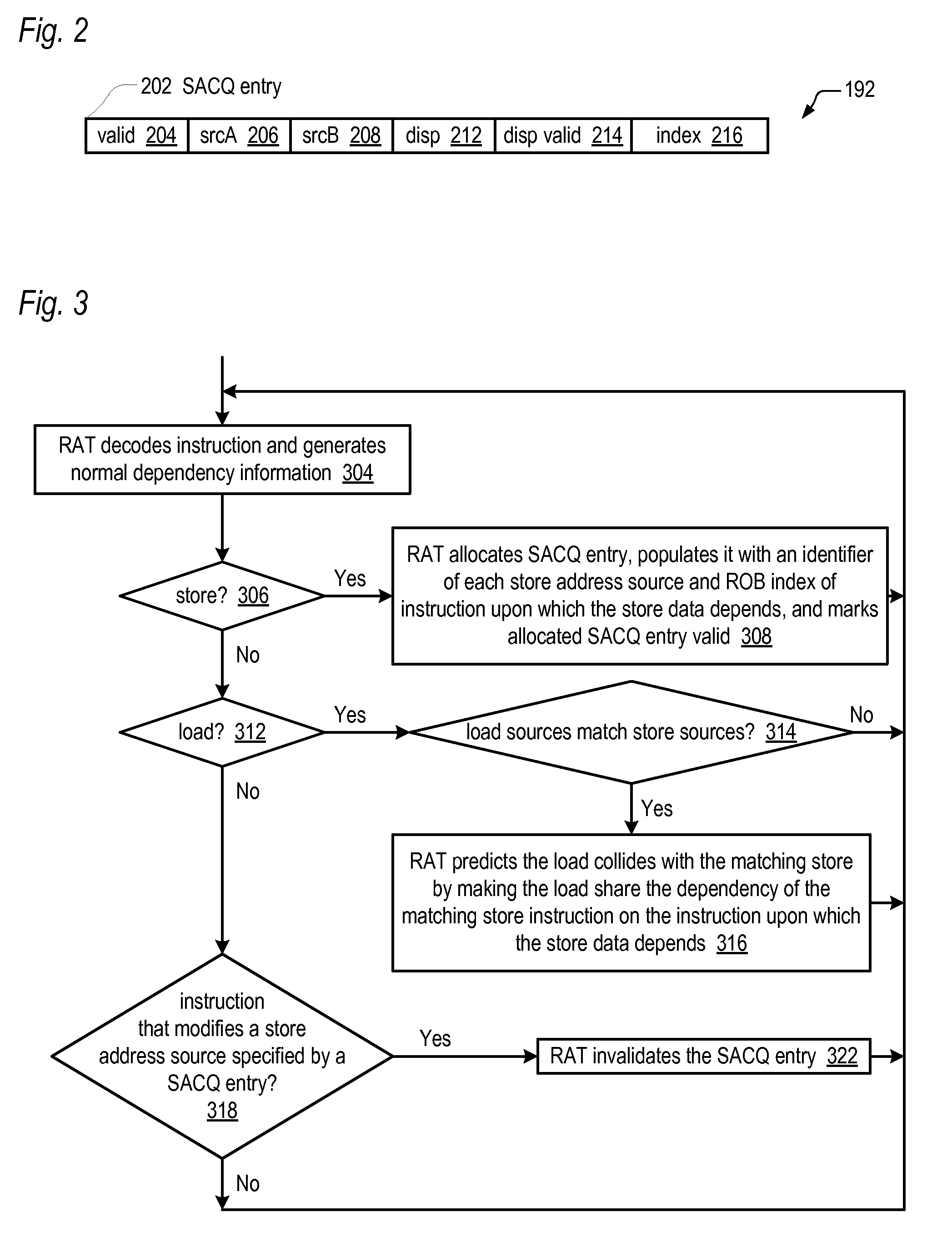

[0025]Described herein are embodiments of a pipelined out-of-order execution microprocessor that reduces the number of load instruction replays in the presence of store collisions. The microprocessor includes an enhanced register alias table (RAT) that predicts when a load instruction is involved in a store collision and causes the load instruction to be dependent upon an additional instruction that the load instruction would not normally be dependent upon. The additional instruction upon which the RAT makes the load instruction dependent is referred to herein as the dependee instruction. The additional, or enhanced, dependency causes the issue logic of the microprocessor to wait to issue the load instruction until the dependee instruction has executed, i.e., has produced its result, so that the dependee instruction result can be forwarded to the load instruction or read from the data cache. Consequently, when the issue logic does issue the load instruction for execution, the load i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More