Methods for quantitatively evaluating the quality of double patterning technology-compliant layouts

a technology of double patterning and quantitative evaluation, applied in the field of methods for fabricating integrated circuits, can solve the problems of significant handicaps such as lack of evaluation methodologies, and achieve the effect of improving the score of metri

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024]The following detailed description is merely exemplary in nature and is not intended to limit the invention or the application and uses of the invention. Furthermore, there is no intention to be bound by any expressed or implied theory presented in the preceding technical field, background, brief summary or the following detailed description.

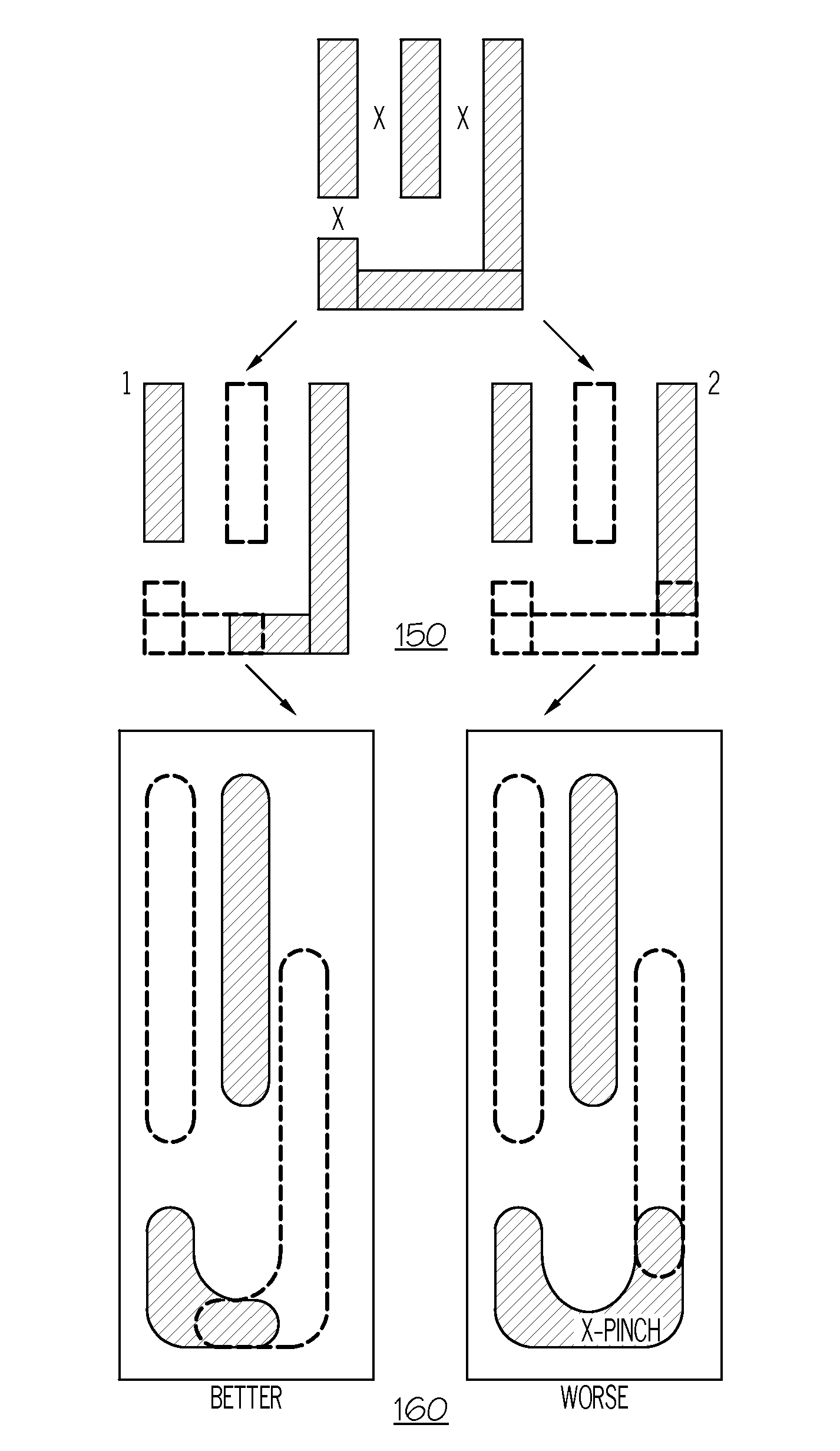

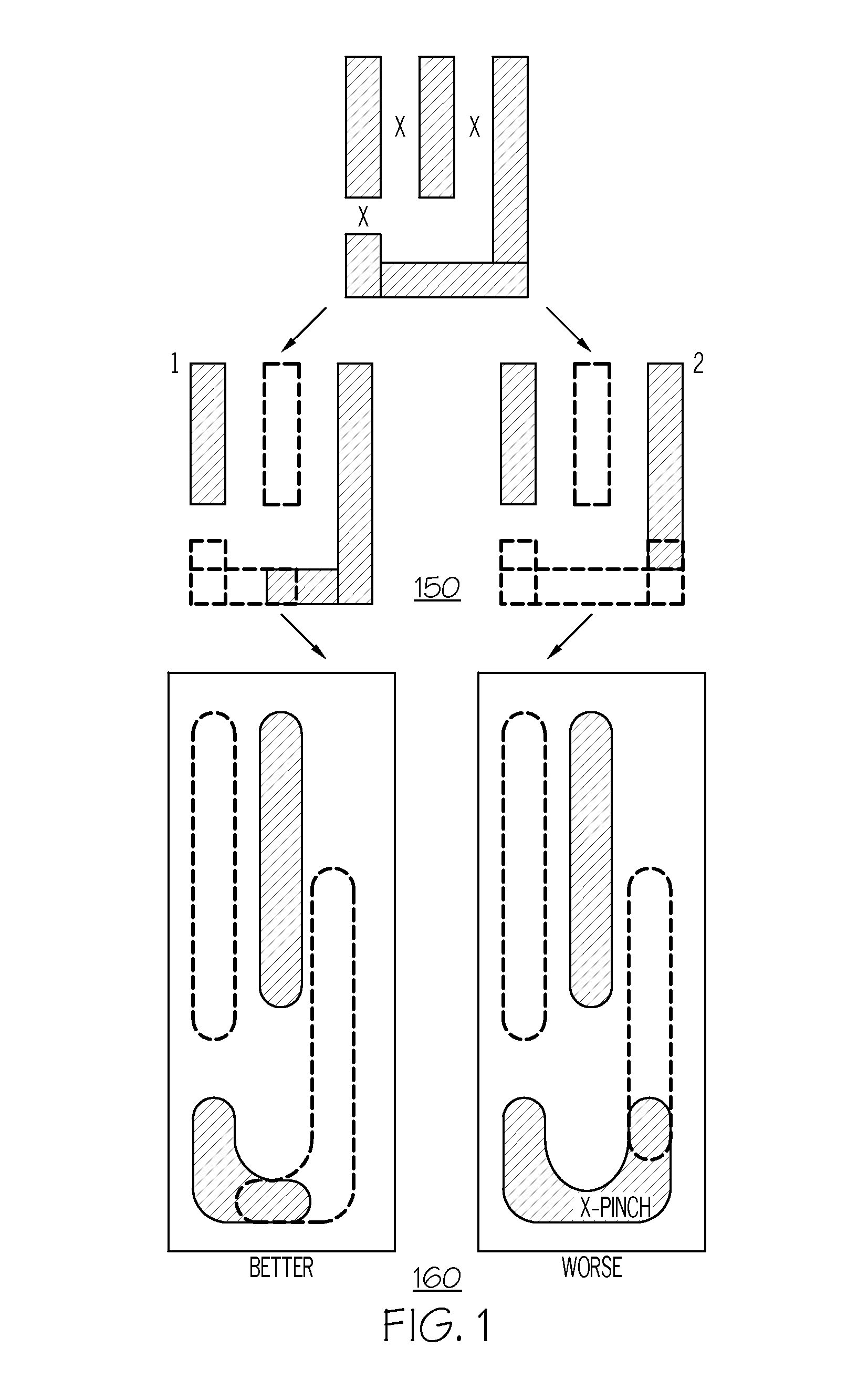

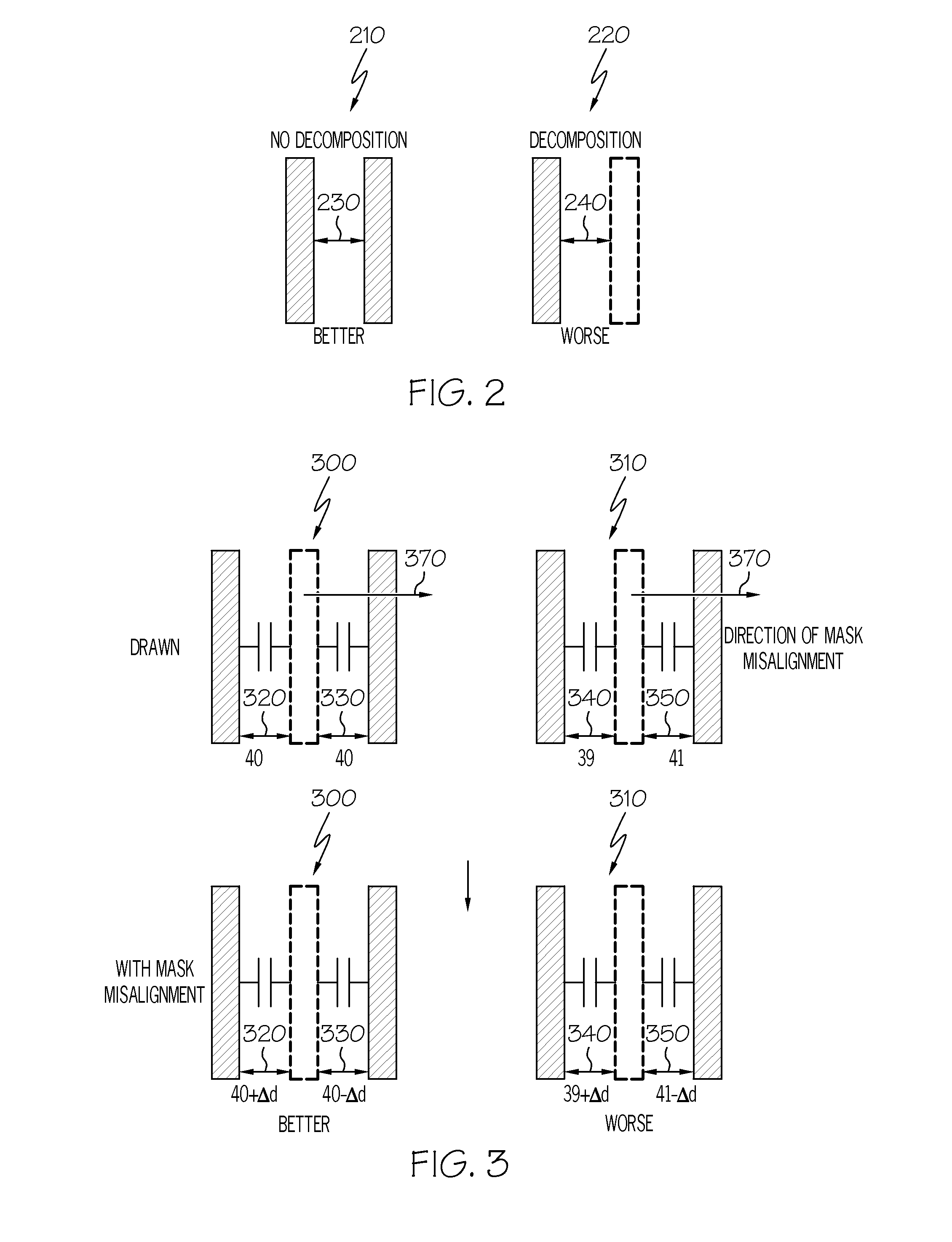

[0025]This invention establishes methods for fabricating an integrated circuit wherein a methodology to systematically quantify the quality of double patterning technology (DPT)-compliant layout designs for an integrated circuit in order to, for example, evaluate and provide guidance for any opportunistic layout modifications such that manufacturability- and yield-related issues can be improved. A DPT-optimized scoring methodology is provided to systematically, automatically, and quickly quantify the quality of DPT-compliant layouts. The score is assigned based on the layout design's robustness to a set of DPT-specific metrics.

[0026]Table ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More