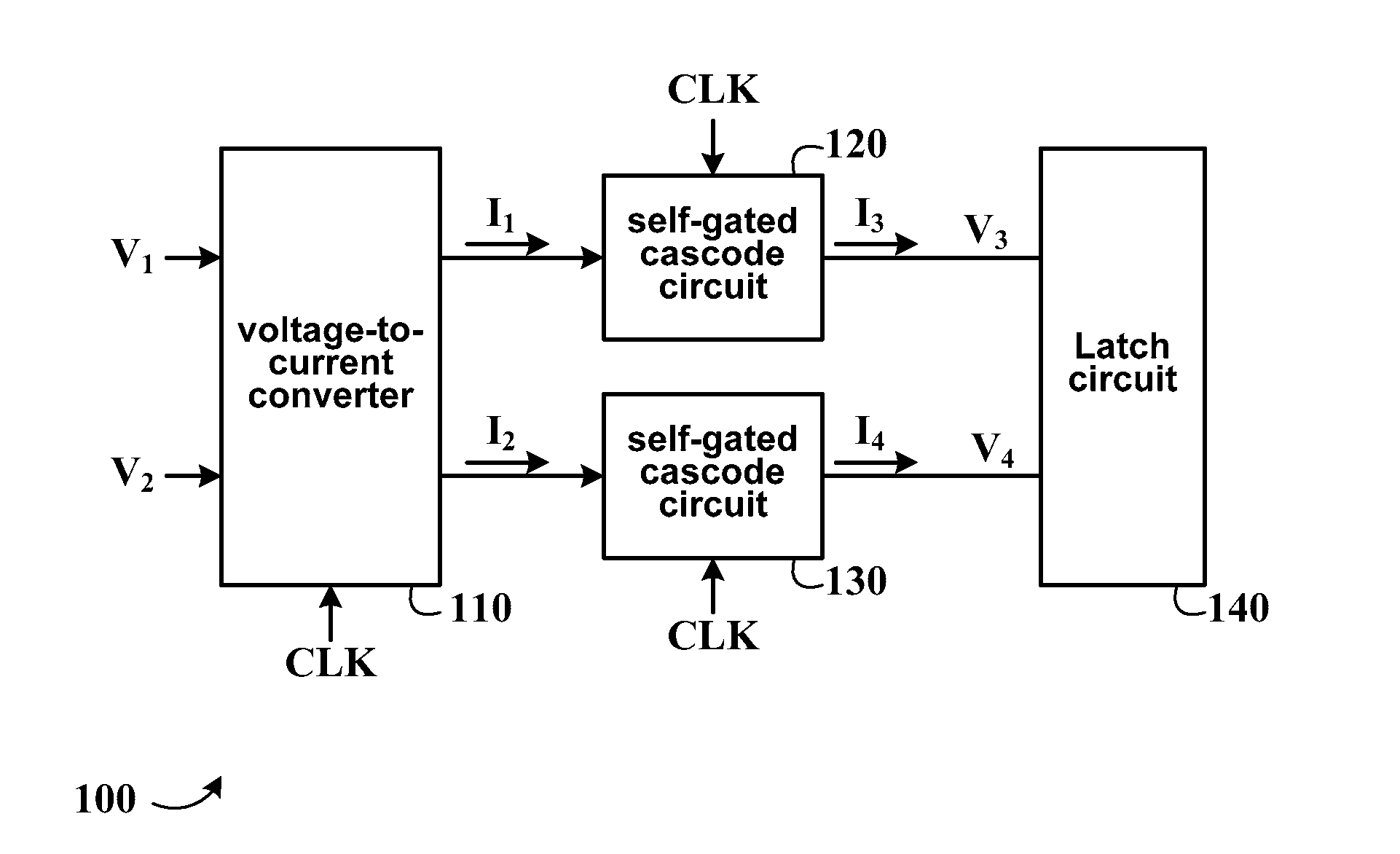

High-speed clocked comparator and method thereof

a comparator and clock technology, applied in the field of comparators, can solve problems such as increasing power consumption, and achieve the effect of high speed and low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

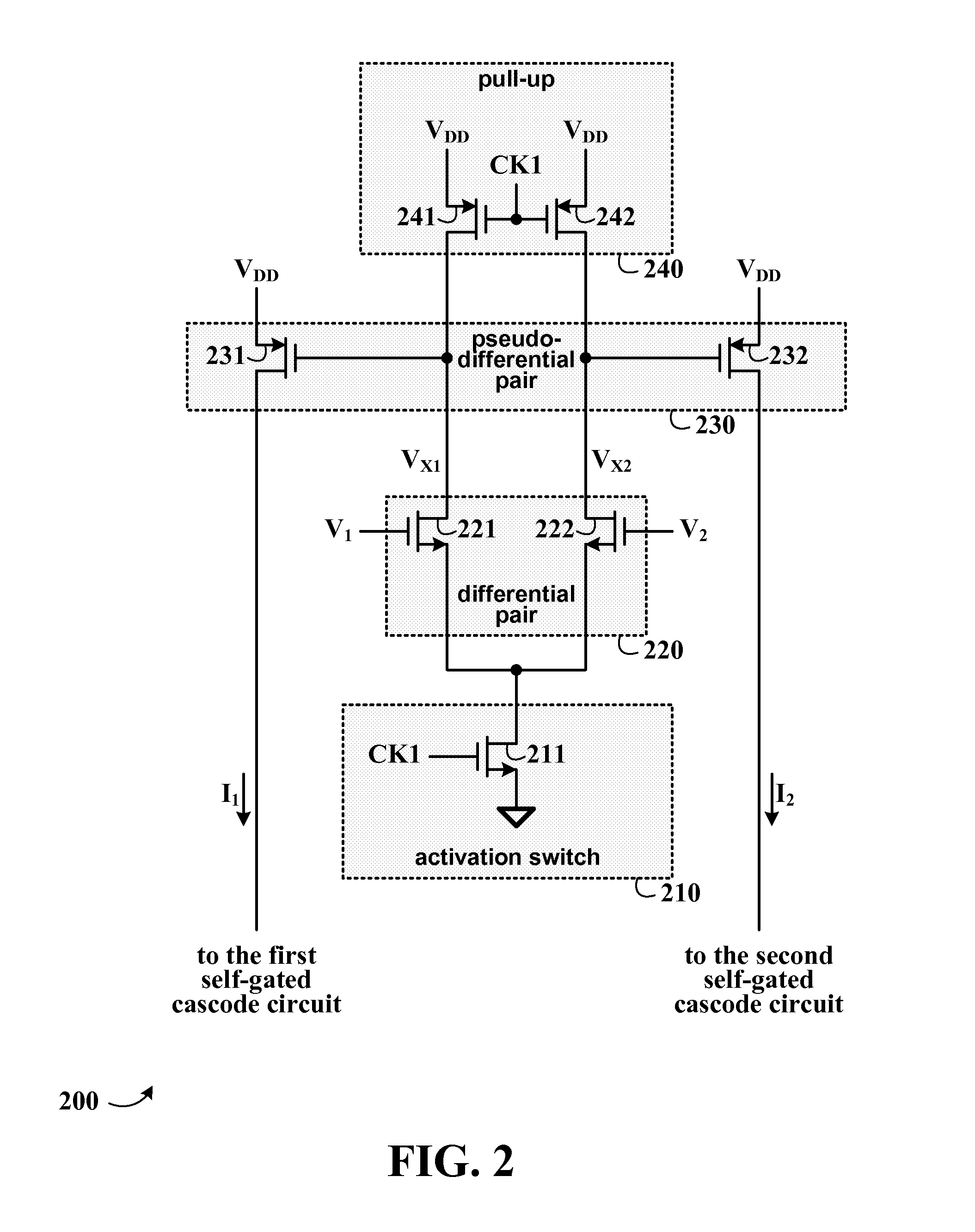

[0015]The present invention relates to comparator. While the specification describes several example embodiments of the invention considered favorable modes of practicing the invention, it should be understood that the invention can be implemented in many ways and is not limited to the particular examples described below or to the particular manner in which any features of such examples are implemented. In other instances, well-known details are not shown or described to avoid obscuring aspects of the invention.

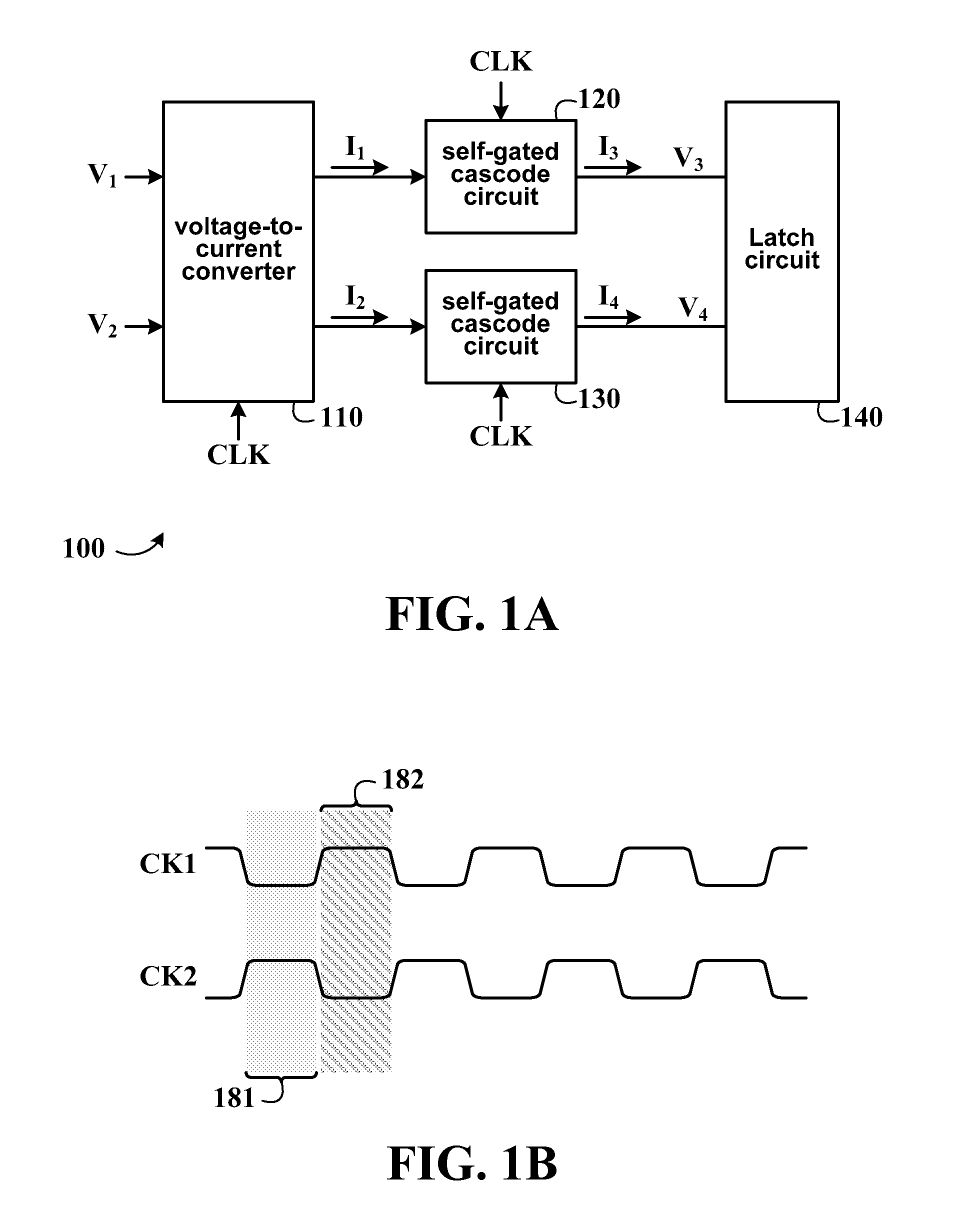

[0016]Throughout this disclosure: “VDD” denotes a power supply circuit node (or simply power supply node); a logical signal is a signal that is either “high” or “low”; it is said to be “high” when the logical signal is of a high voltage level that is equal to a voltage level of a power supply node (which is denoted by VDD in this disclosure); and it is said to be “low” when the logical signal is of a low voltage level that is equal to a voltage level of a ground node. It shou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More