Patents

Literature

32 results about "Self gating" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

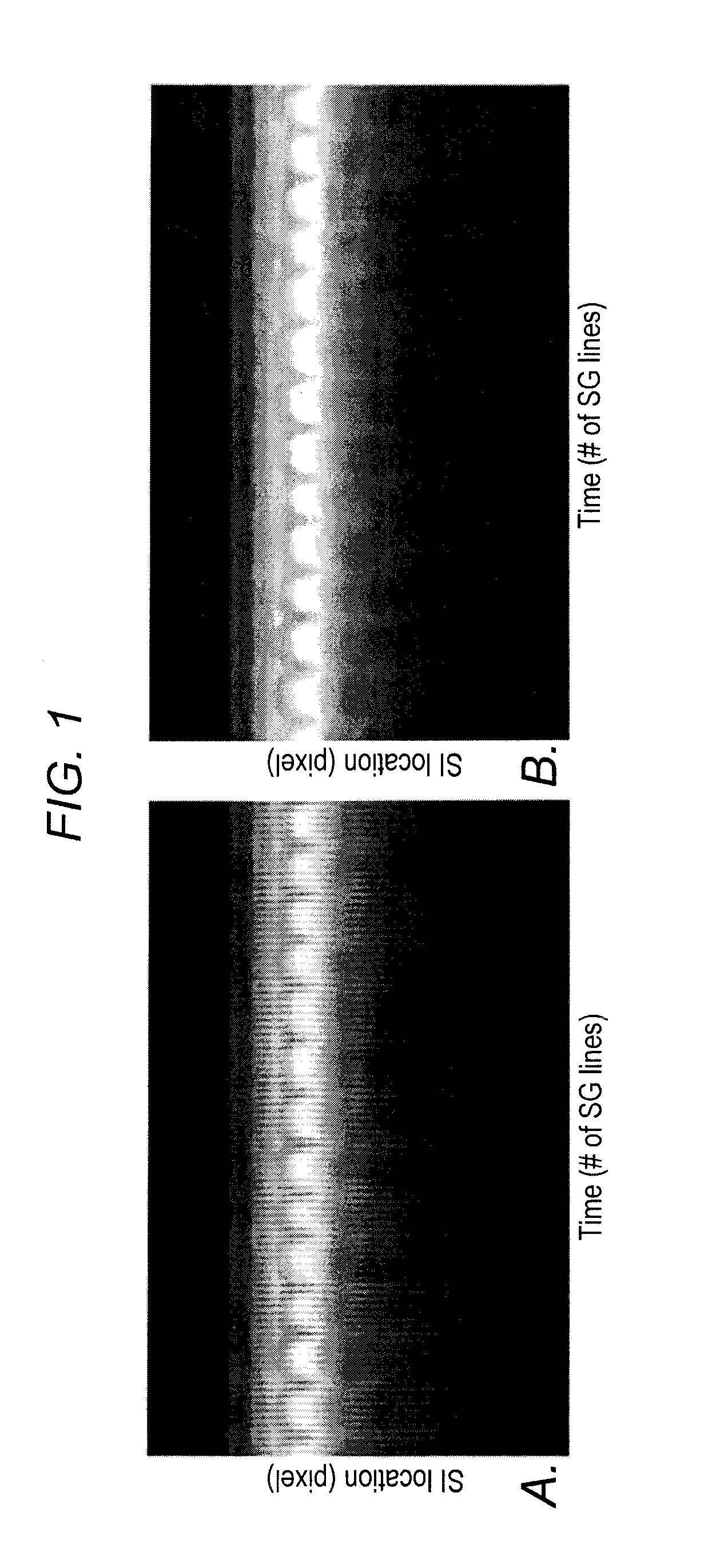

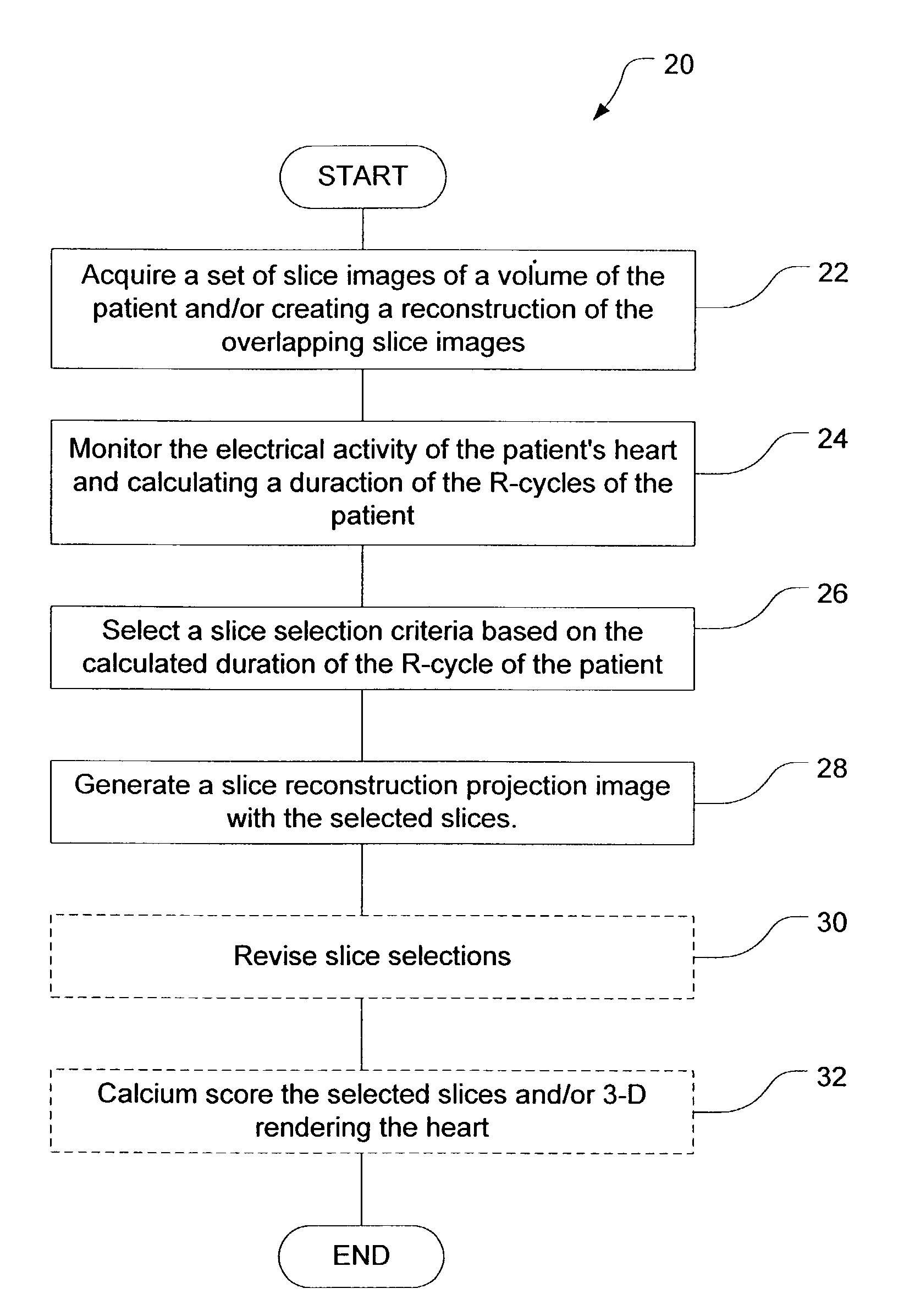

Methods and software for self-gating a set of images

InactiveUS20060257012A1Enhance the imageImproves calcium scoringUltrasonic/sonic/infrasonic diagnosticsElectrocardiographyEcg signalProjection image

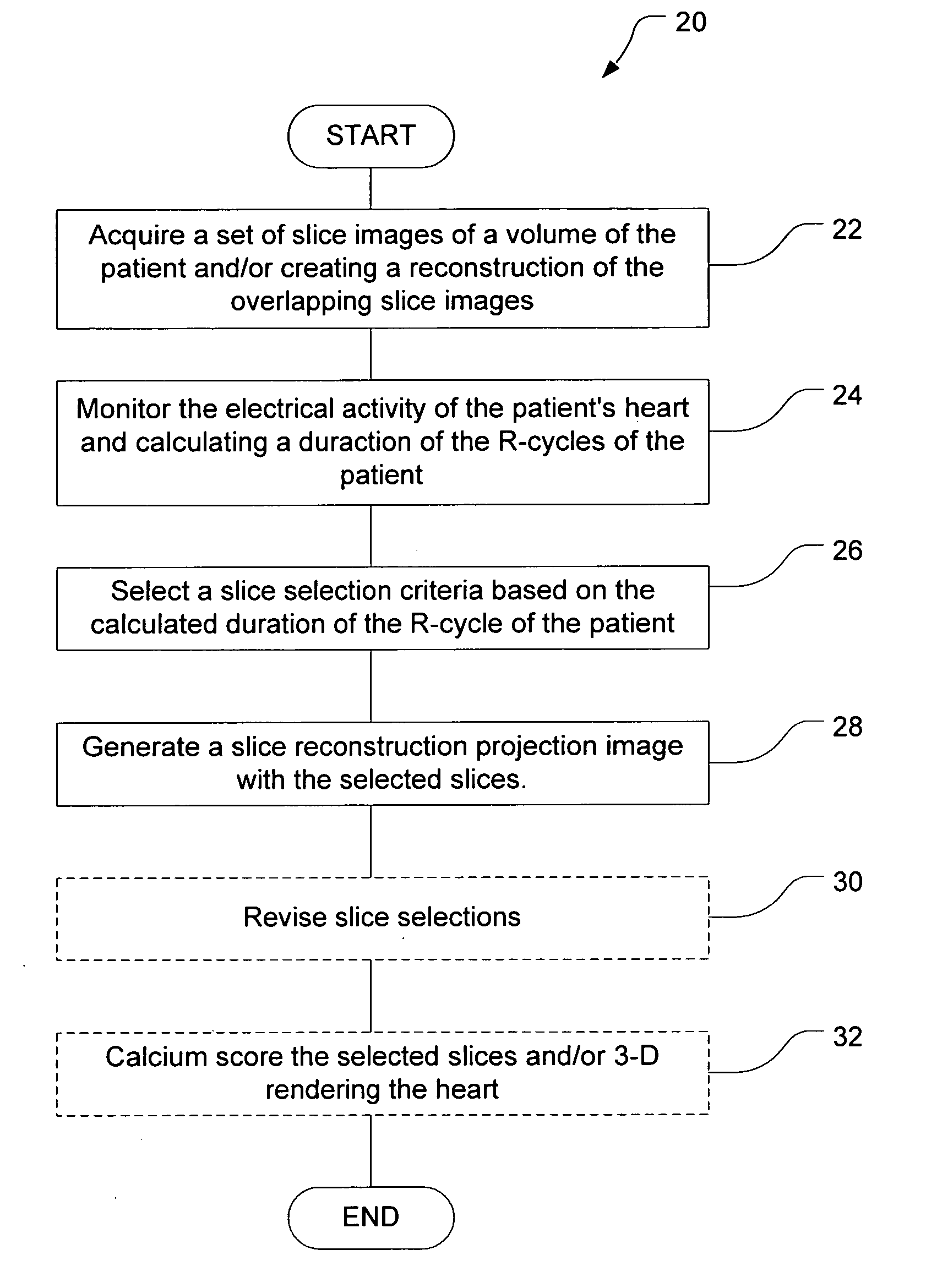

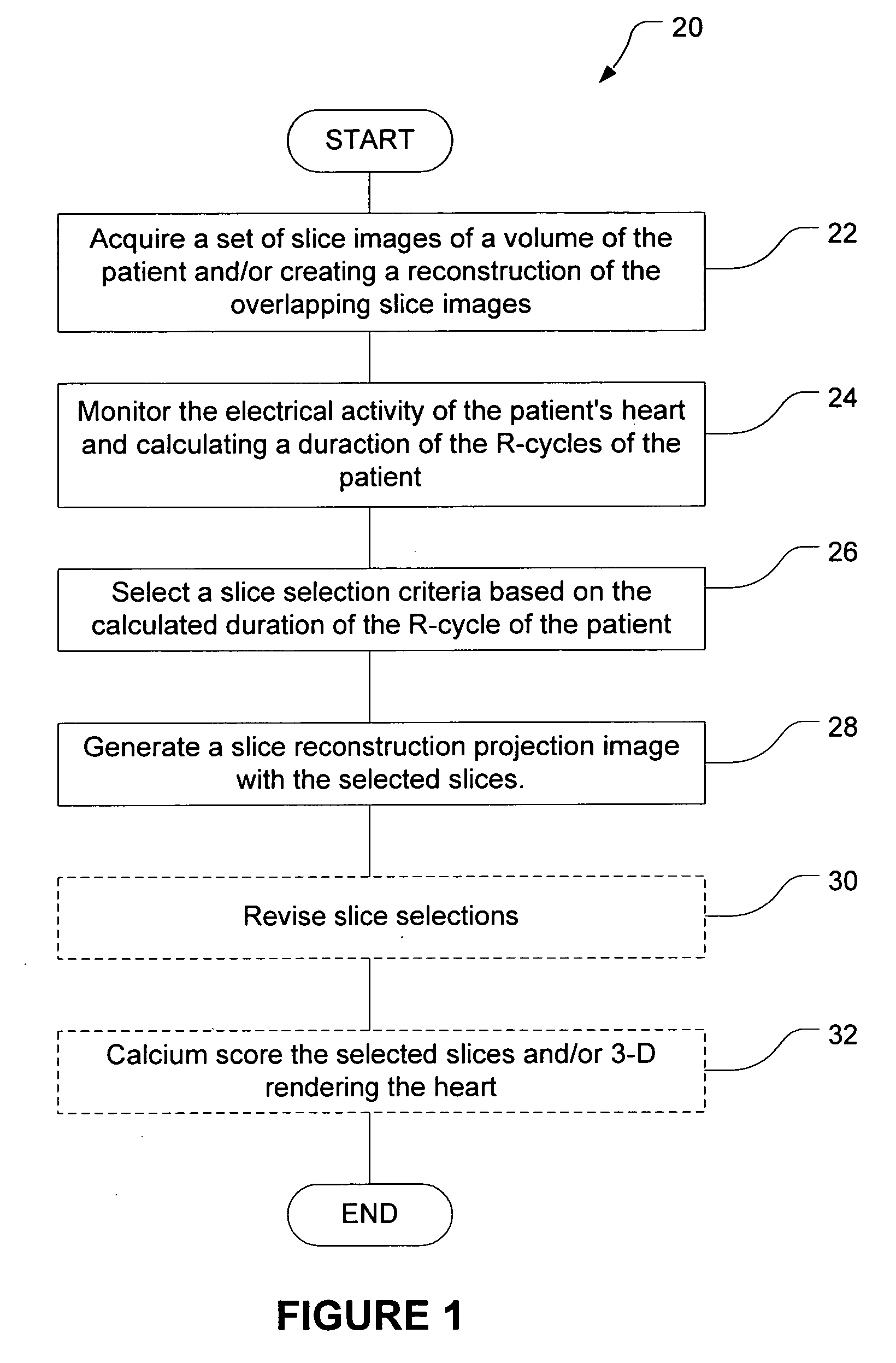

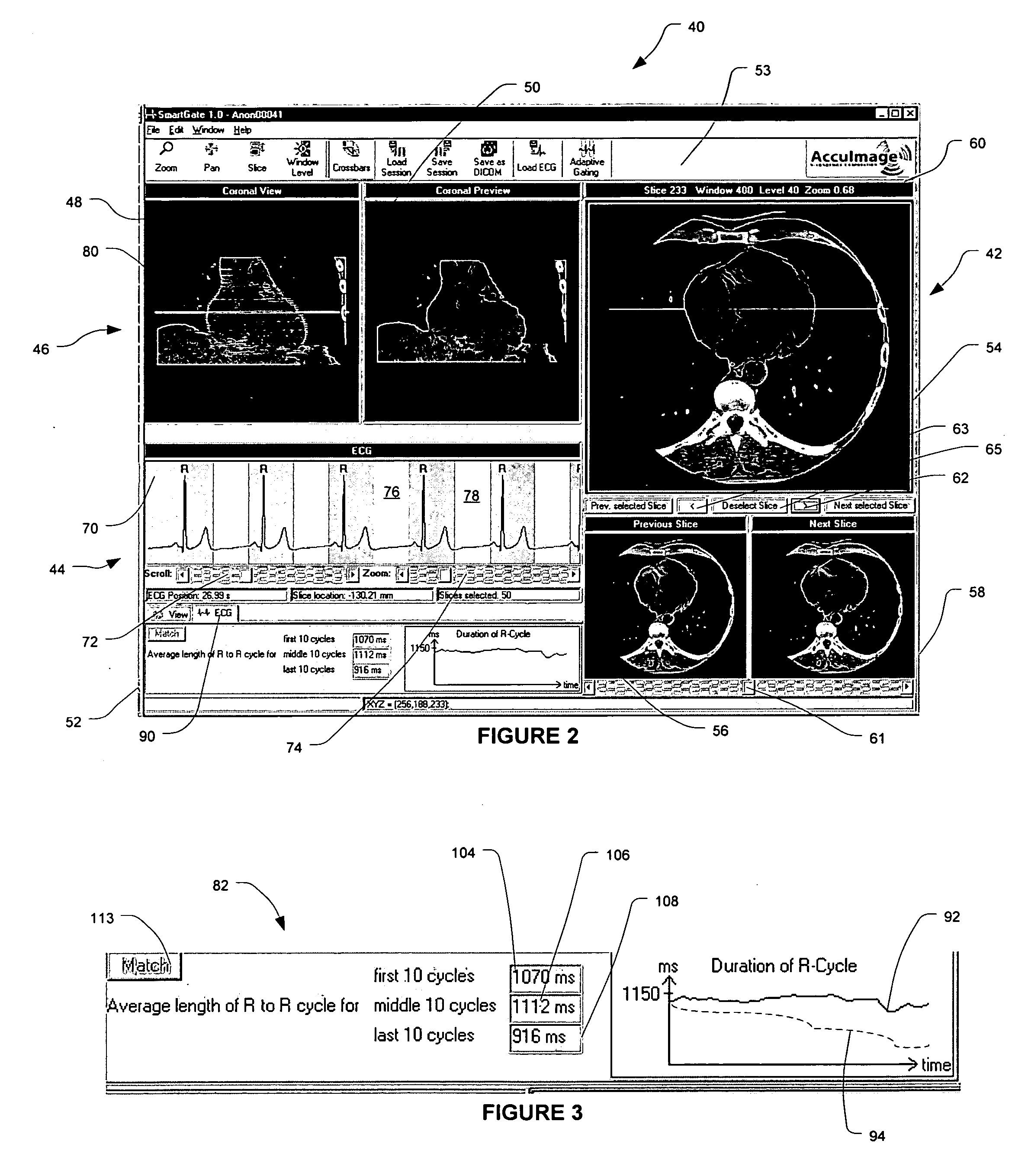

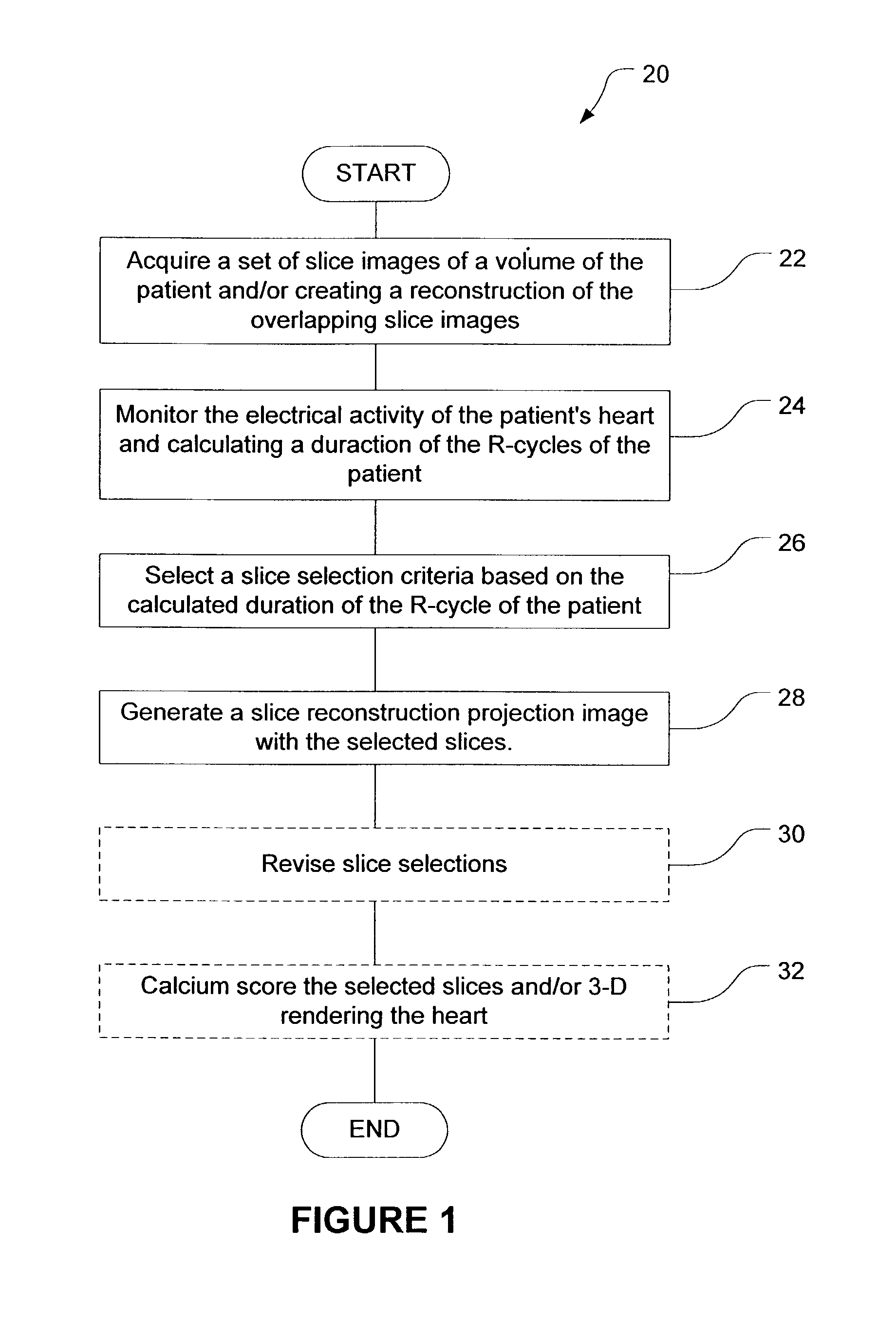

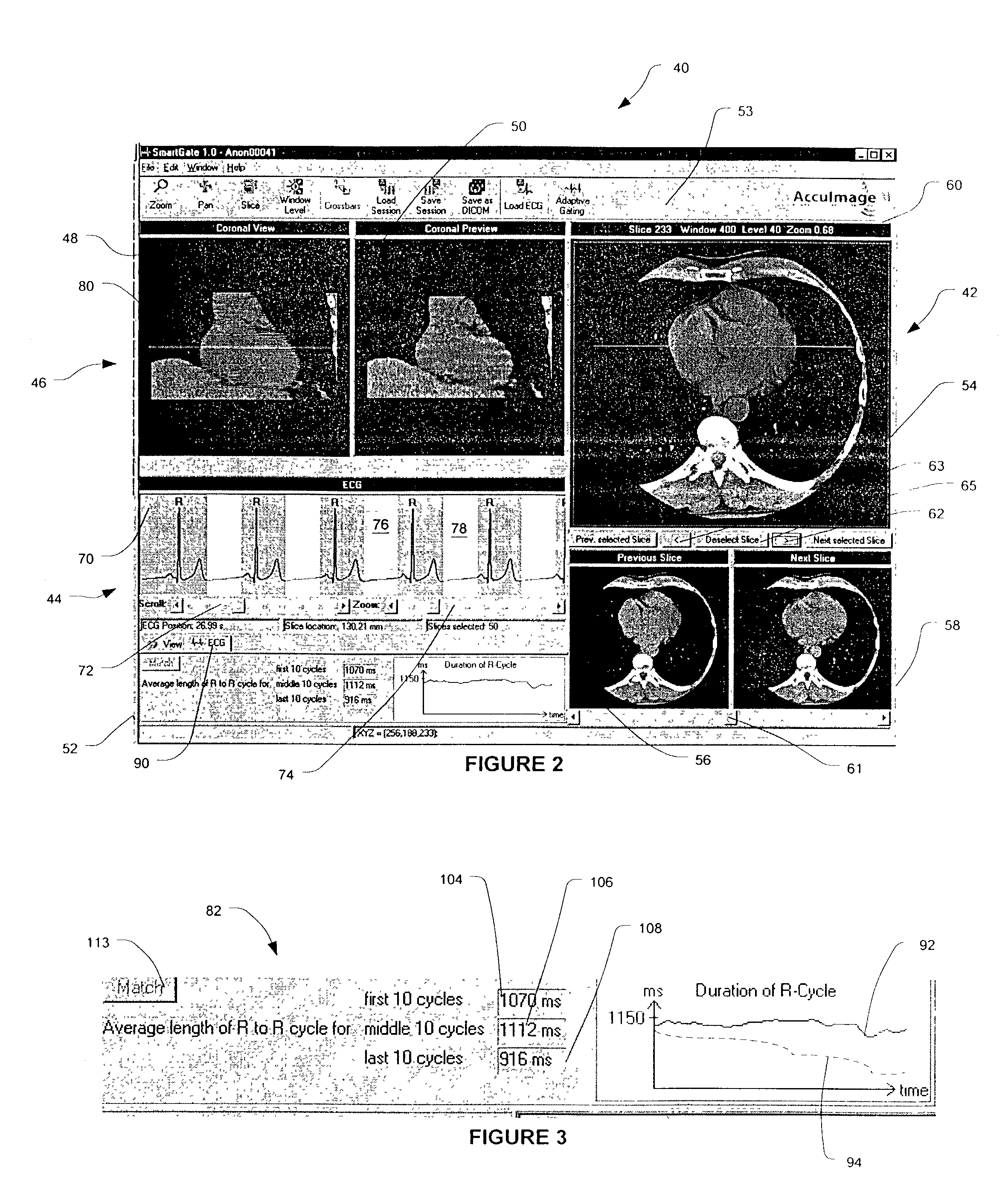

Methods and software for self-gating a set of images. In exemplary embodiments, a fundamental heart frequency of the patient can be measured without the use of an ECG signal. In one method, the fundamental heart frequency can be determined by analyzing the size of the heart in the images. In another method, the fundamental heart frequency can be determined by applying a Fourier Transform. The measured fundamental heart frequency can thereafter be used to select slice images from the image scan for creation of a sagittal or coronal projection image. In exemplary embodiments, the resultant projection image can be used for coronary calcium detection and scoring.

Owner:MERATIVE US LP

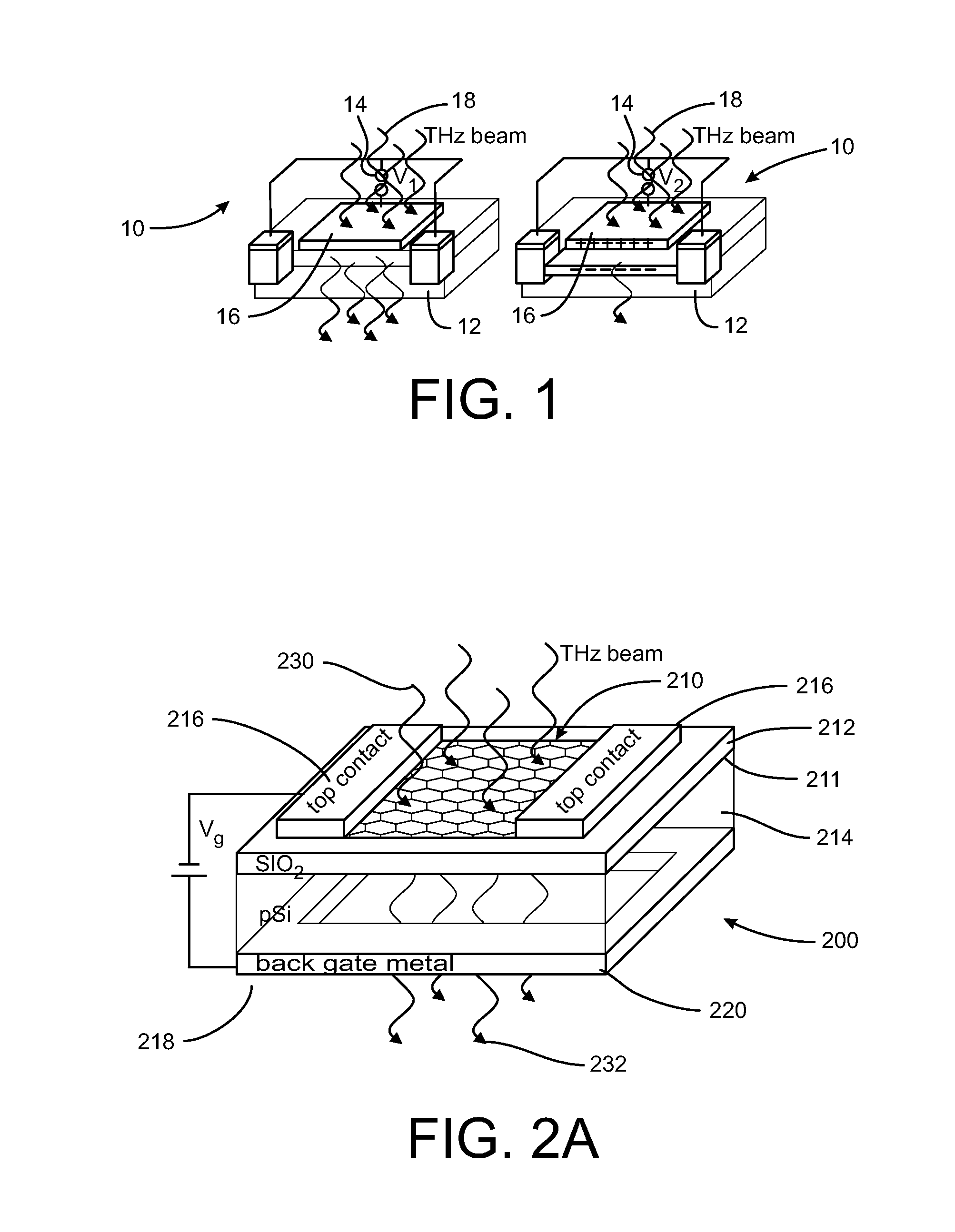

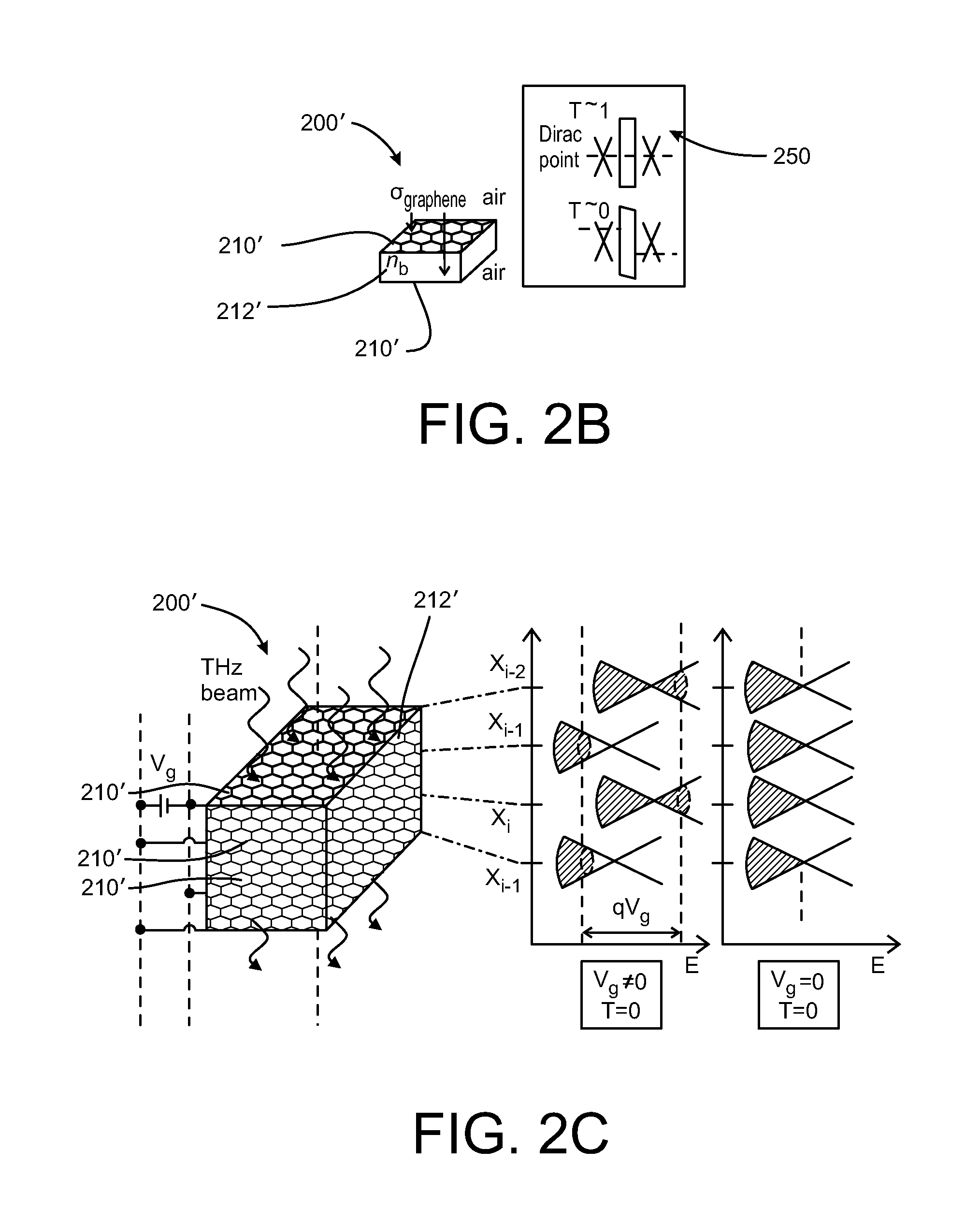

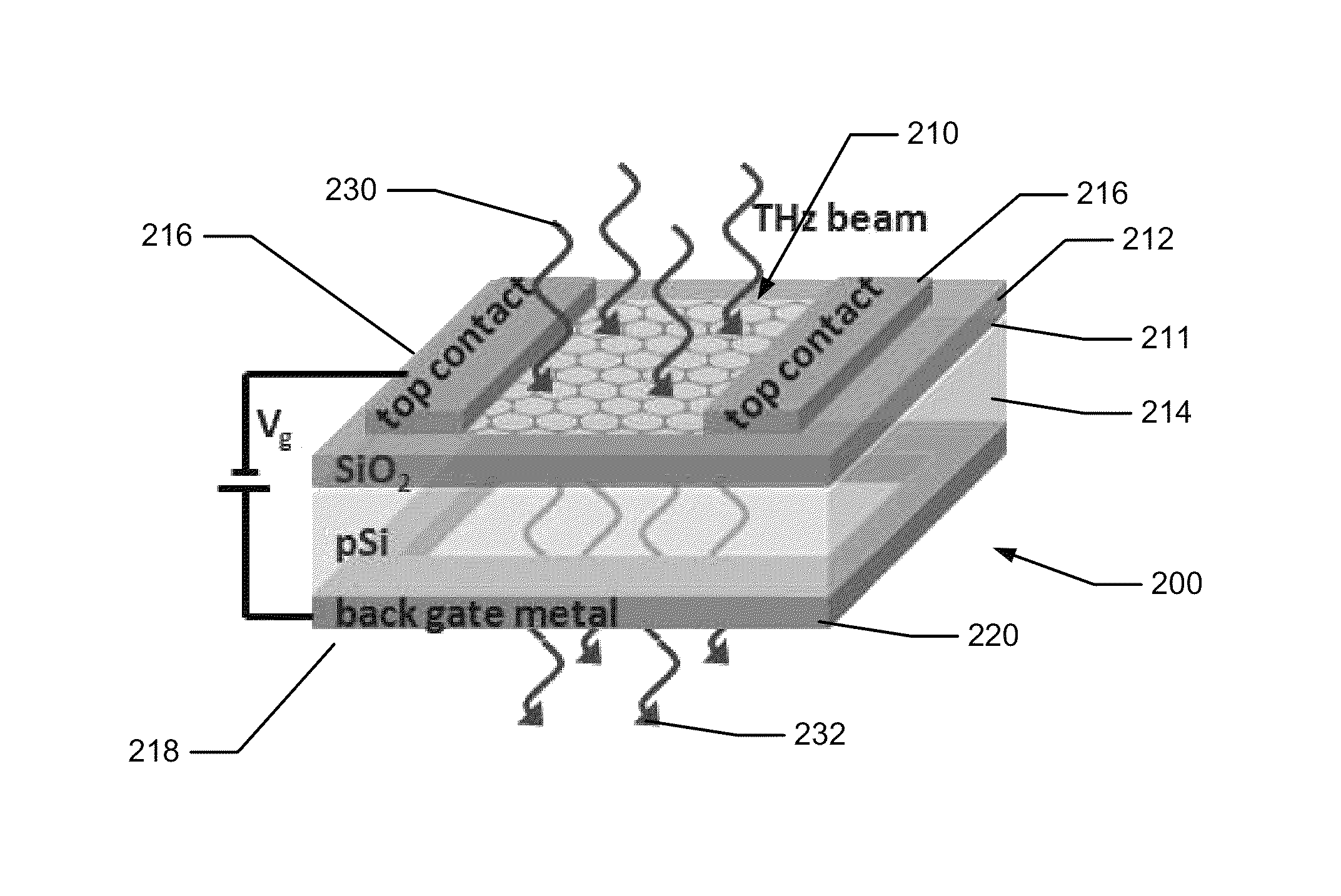

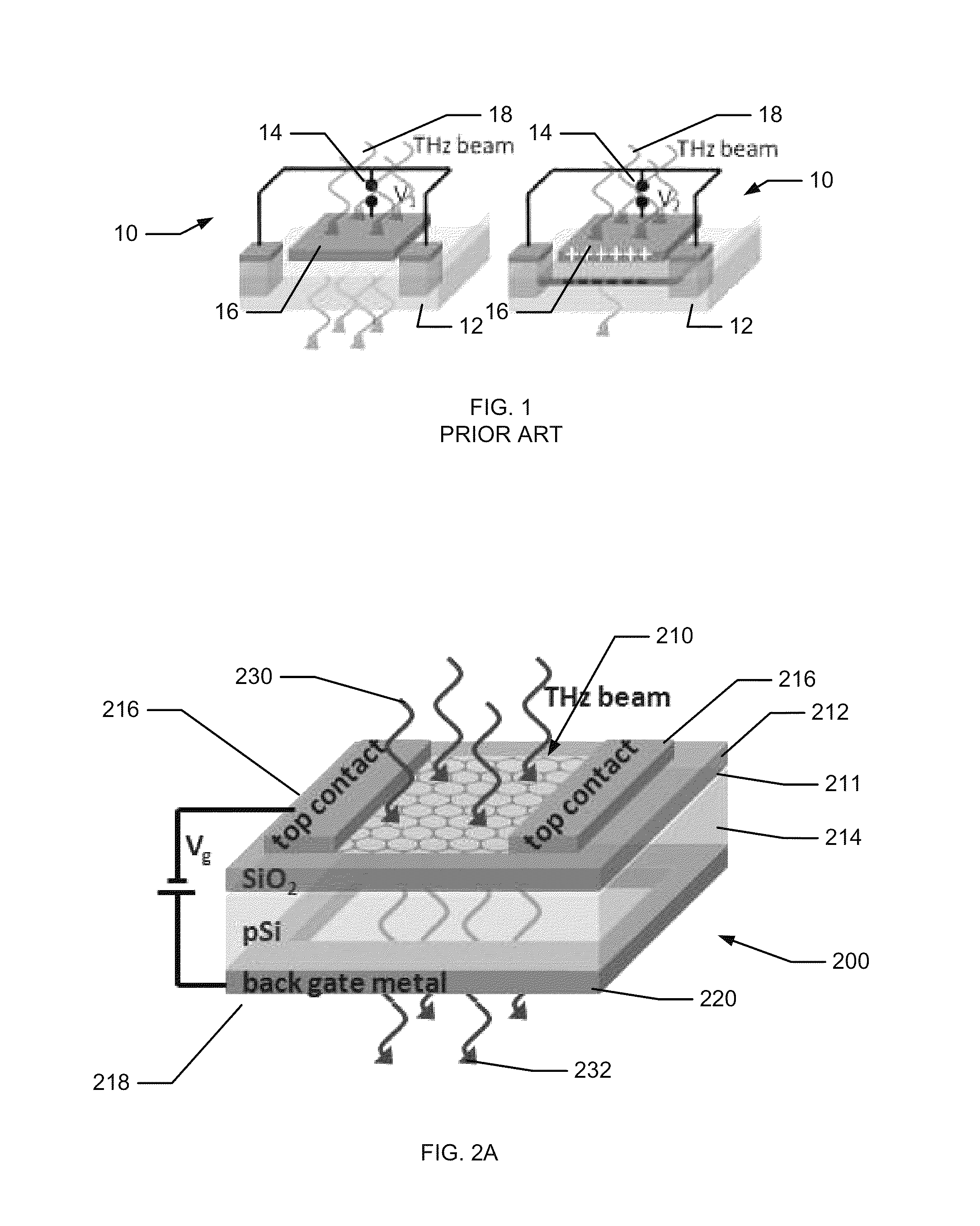

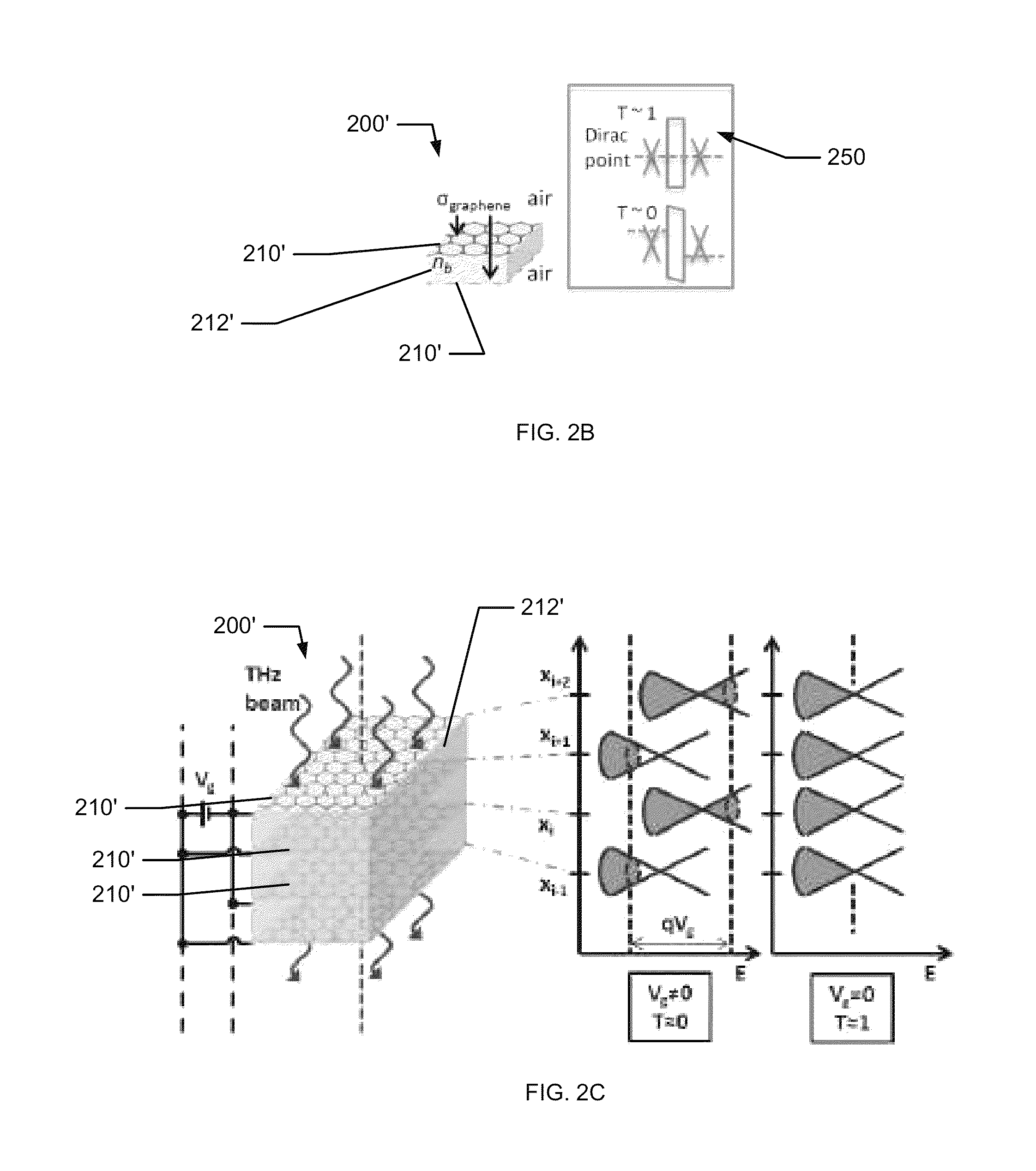

Methods and apparatus for terahertz wave amplitude modulation

InactiveUS20130342279A1Amplitude modulation detailsElectromagnetic wave modulationCapacitanceA wave amplitude

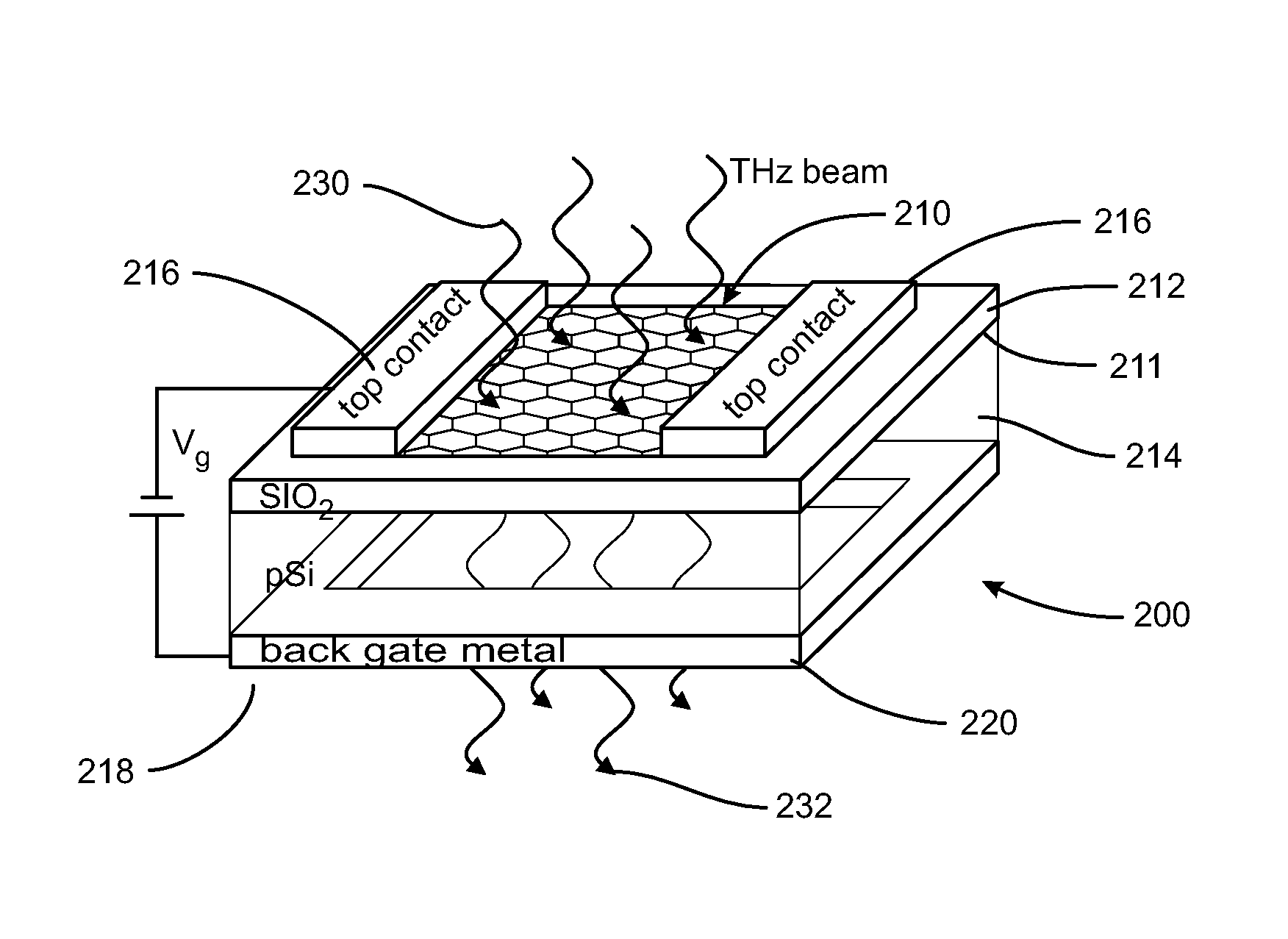

A wave amplitude modulator for modulating a transmitted electromagnetic wave includes one or multiple self-gated capacitively coupled pair(s) of electron layers such as semiconductor or semimetal layers. Two electrical contacts are placed to each layer of electrons of the self-gated pair(s), and a power source is electrically connected to them. The power source, by varying the voltage applied between layers of electrons, tunes the electron density thereof, thereby adjusting the optical conductivity thereof, and the change in the optical conductivity of the layers of electrons causes an amplitude modulation of the transmitted electromagnetic wave passing through the capacitively coupled layers of electrons.

Owner:UNIV OF NOTRE DAME DU LAC

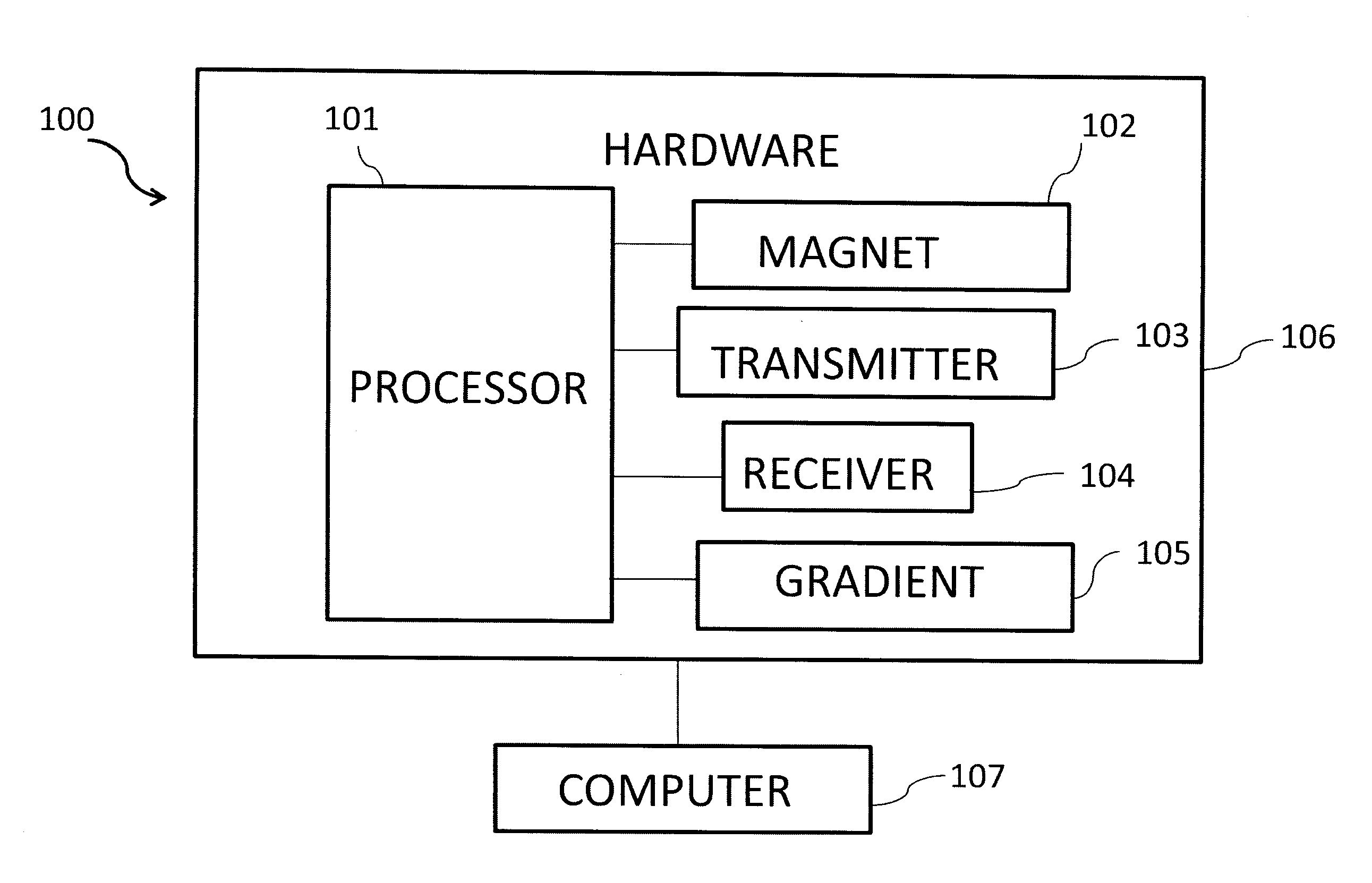

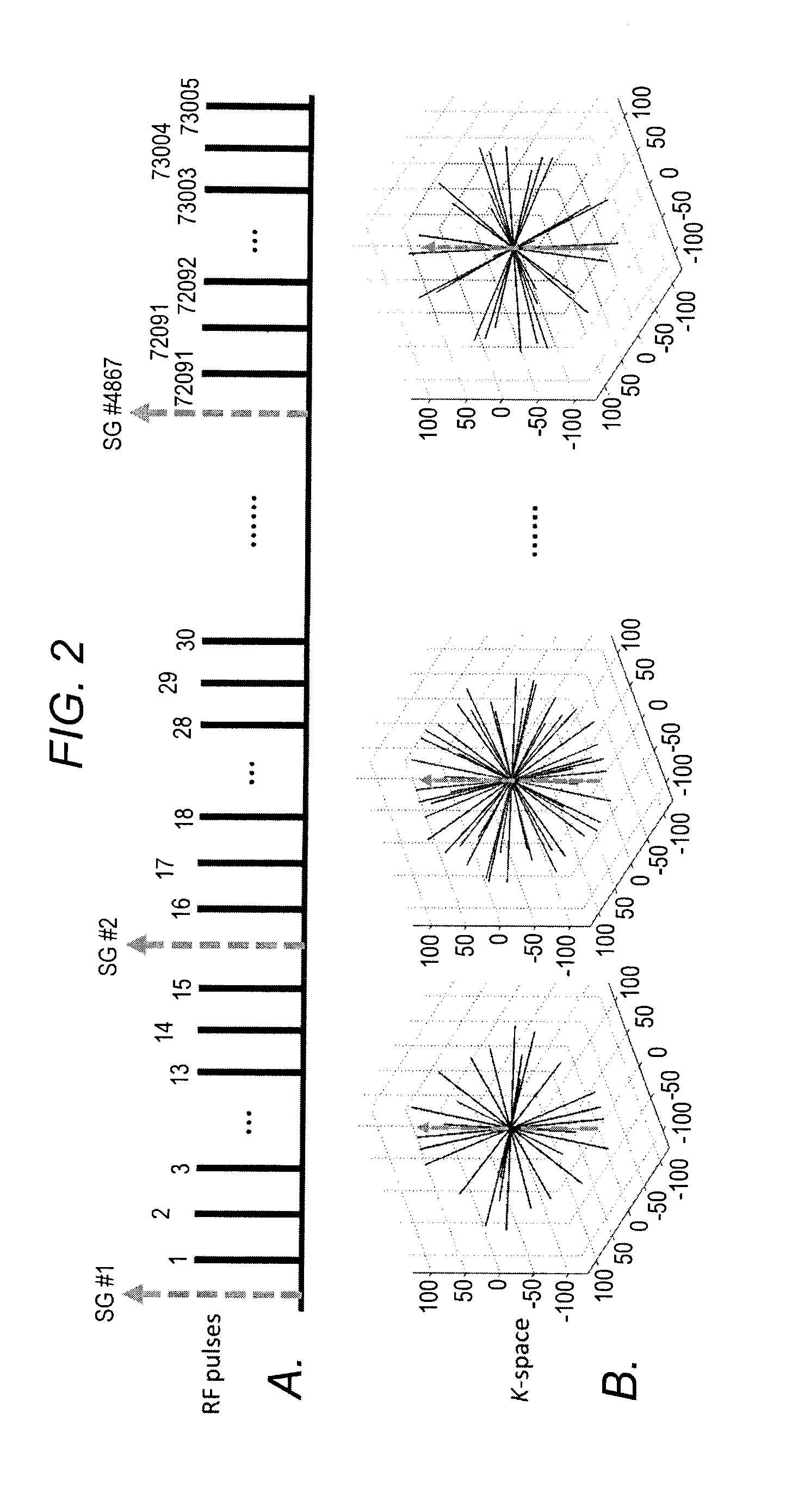

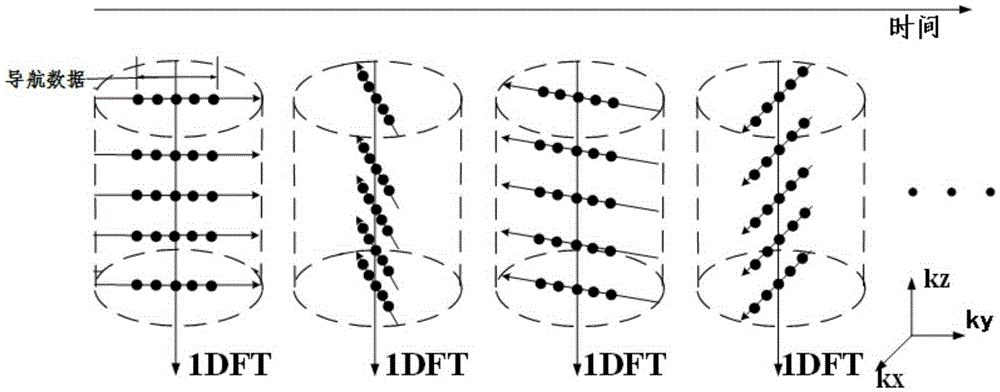

Characterization of respiratory motion in the abdomen using a 4d MRI technique with 3D radial sampling and respiratory self-gating

ActiveUS20160324500A1Magnetic measurementsOrgan movement/changes detectionRespiratory phaseAnesthesia

In some embodiments, the present application discloses utilizing a continuous spoiled gradient echo sequence with 3D radial trajectory and 1D self-gating for respiratory motion detection. In certain embodiments, data acquired are retrospectively sorted into different respiratory phases based on their temporal locations within a respiratory cycle, and each phase is reconstructed via a self-calibrating CG-SENSE program.

Owner:CEDARS SINAI MEDICAL CENT

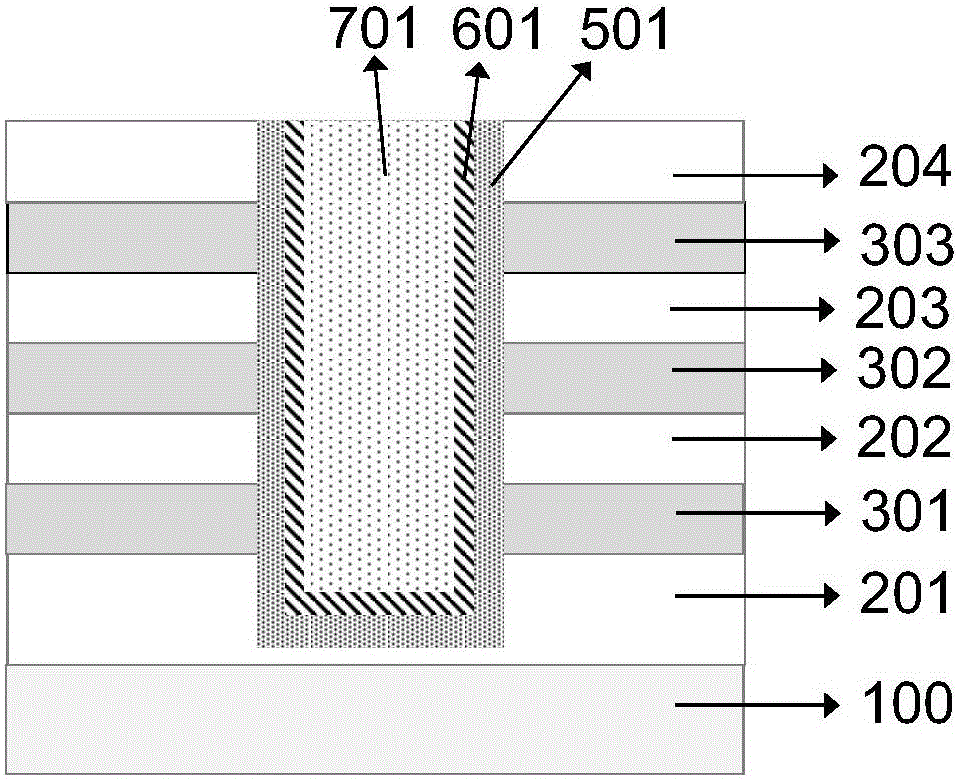

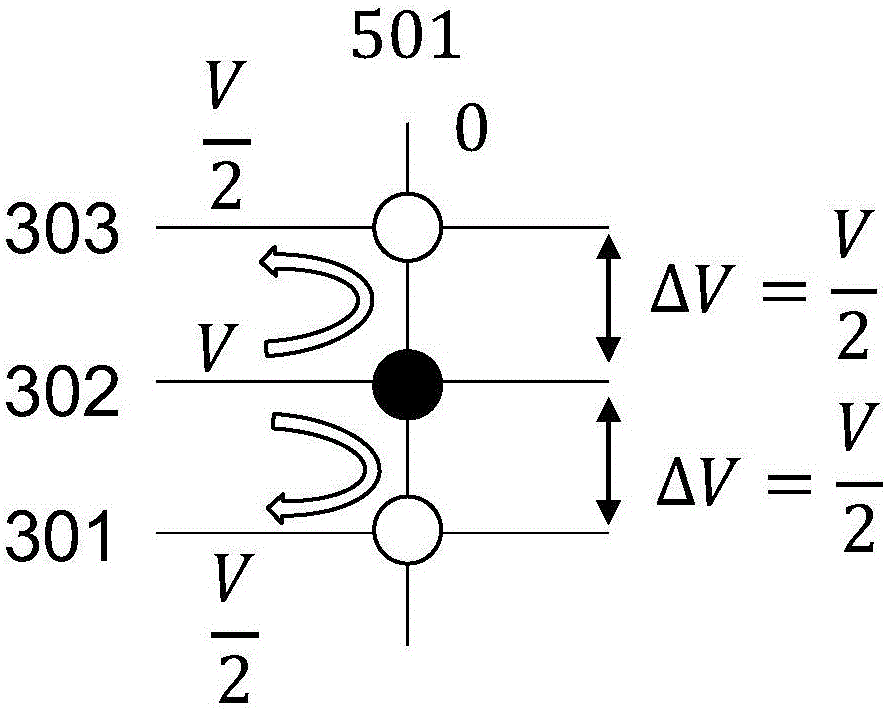

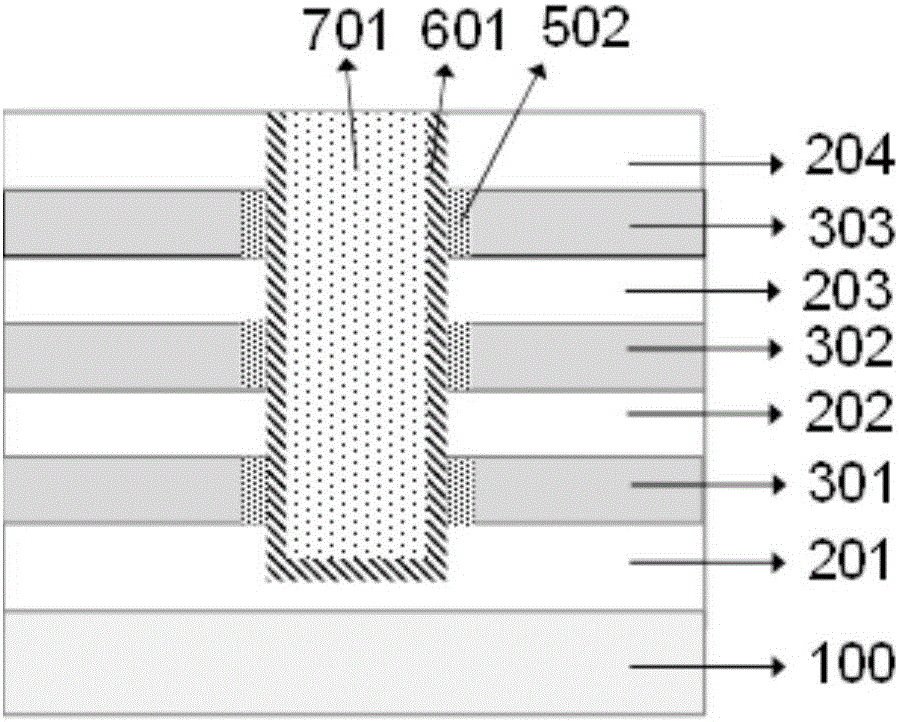

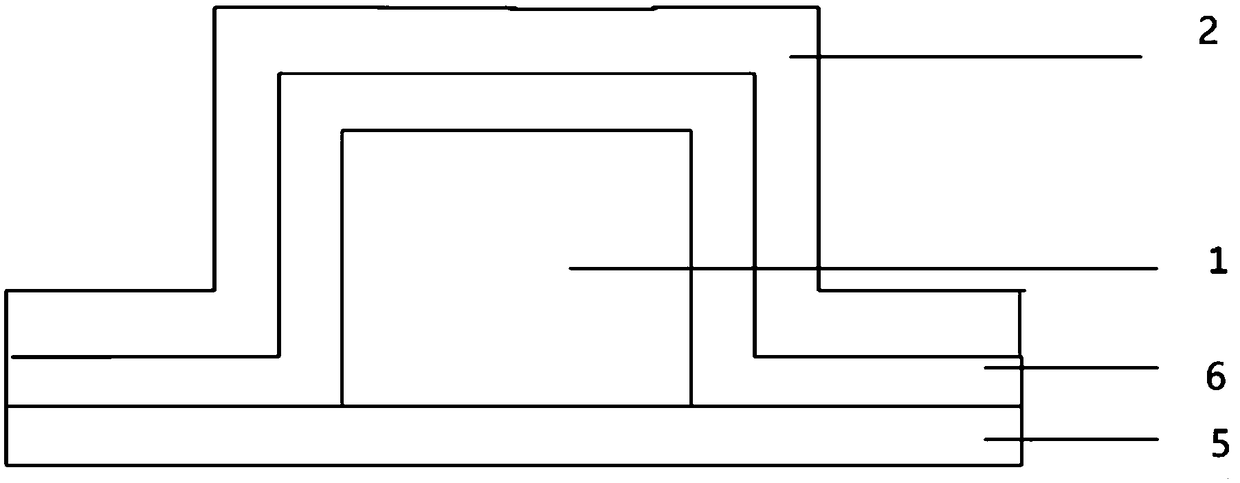

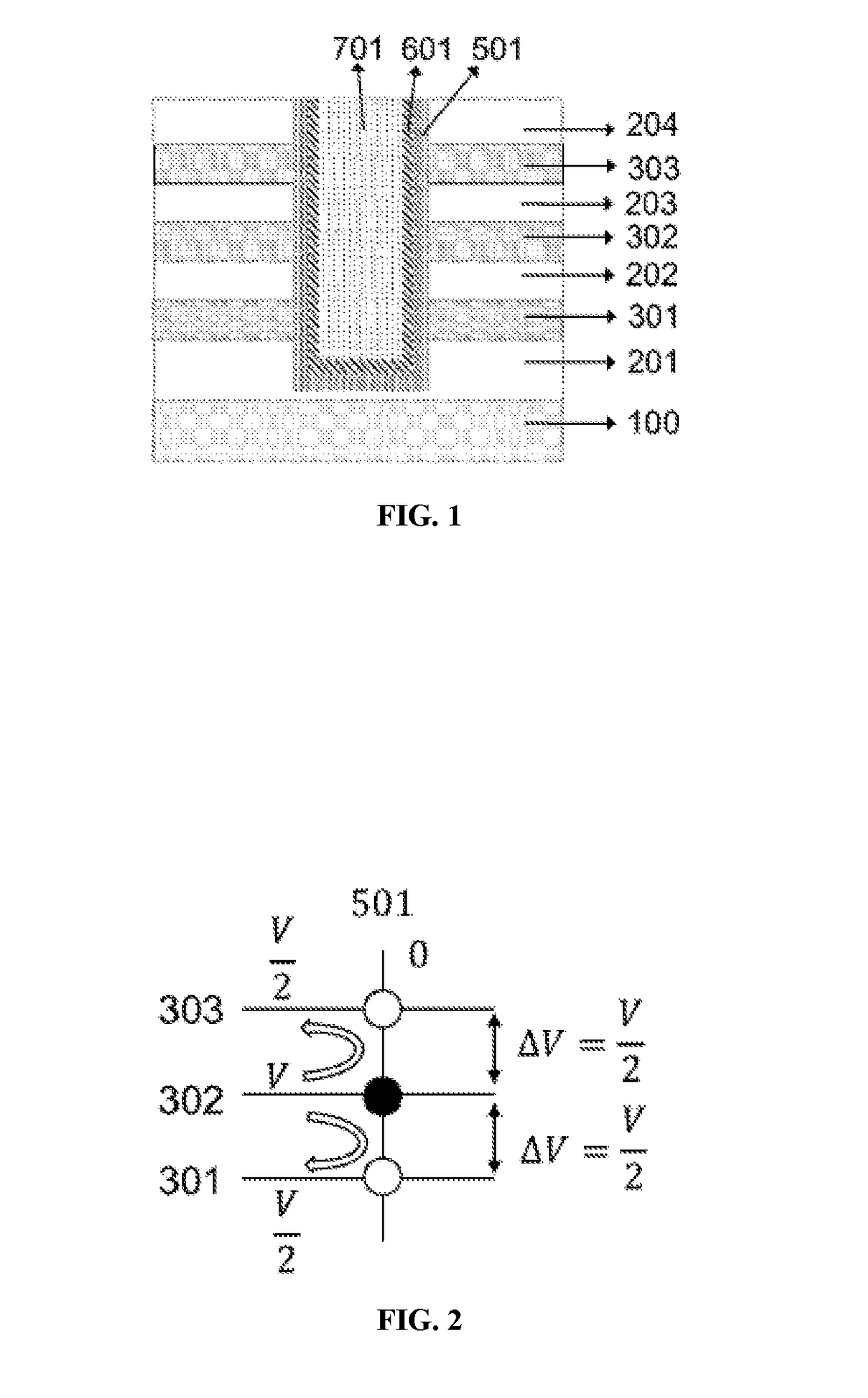

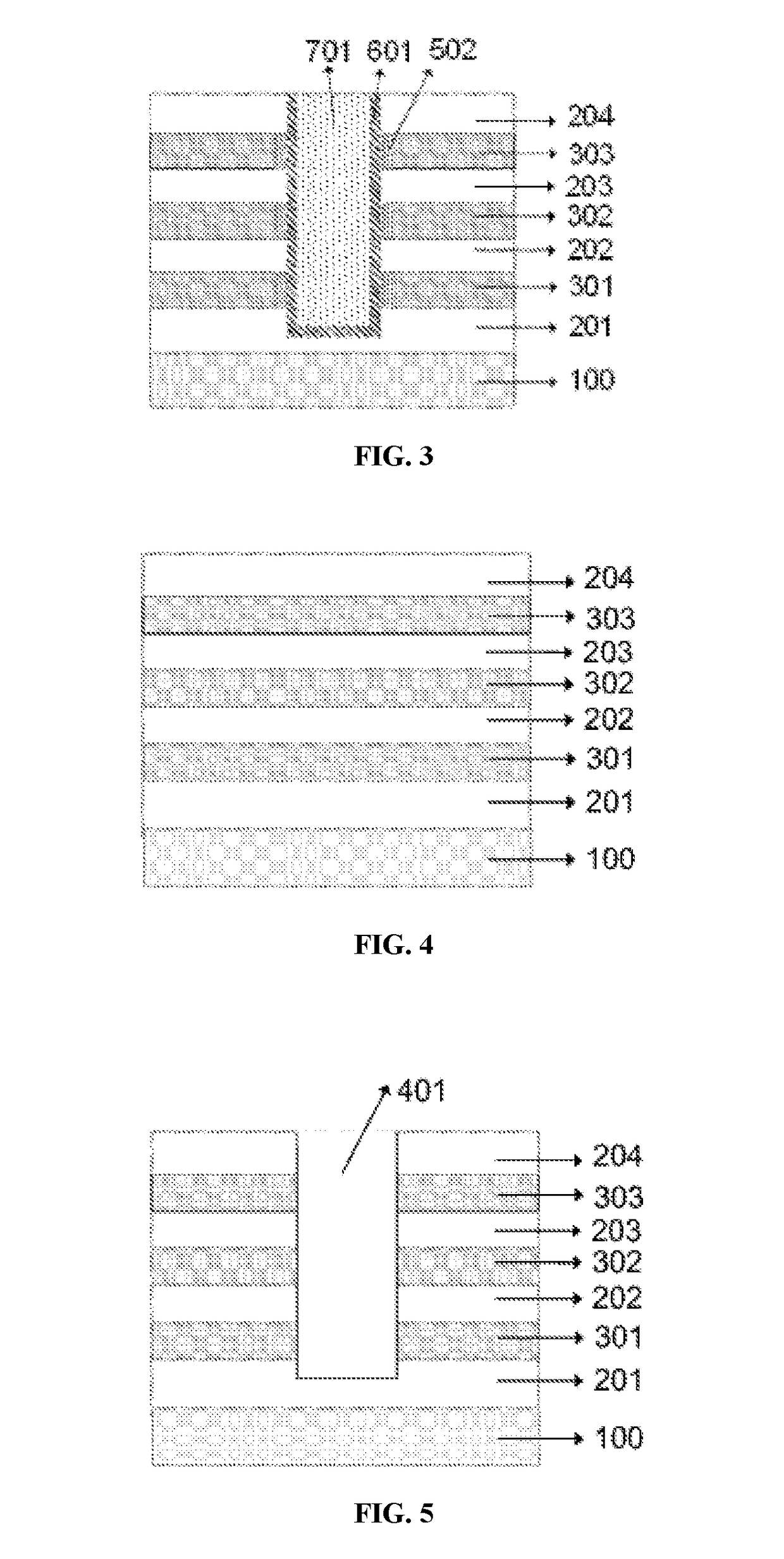

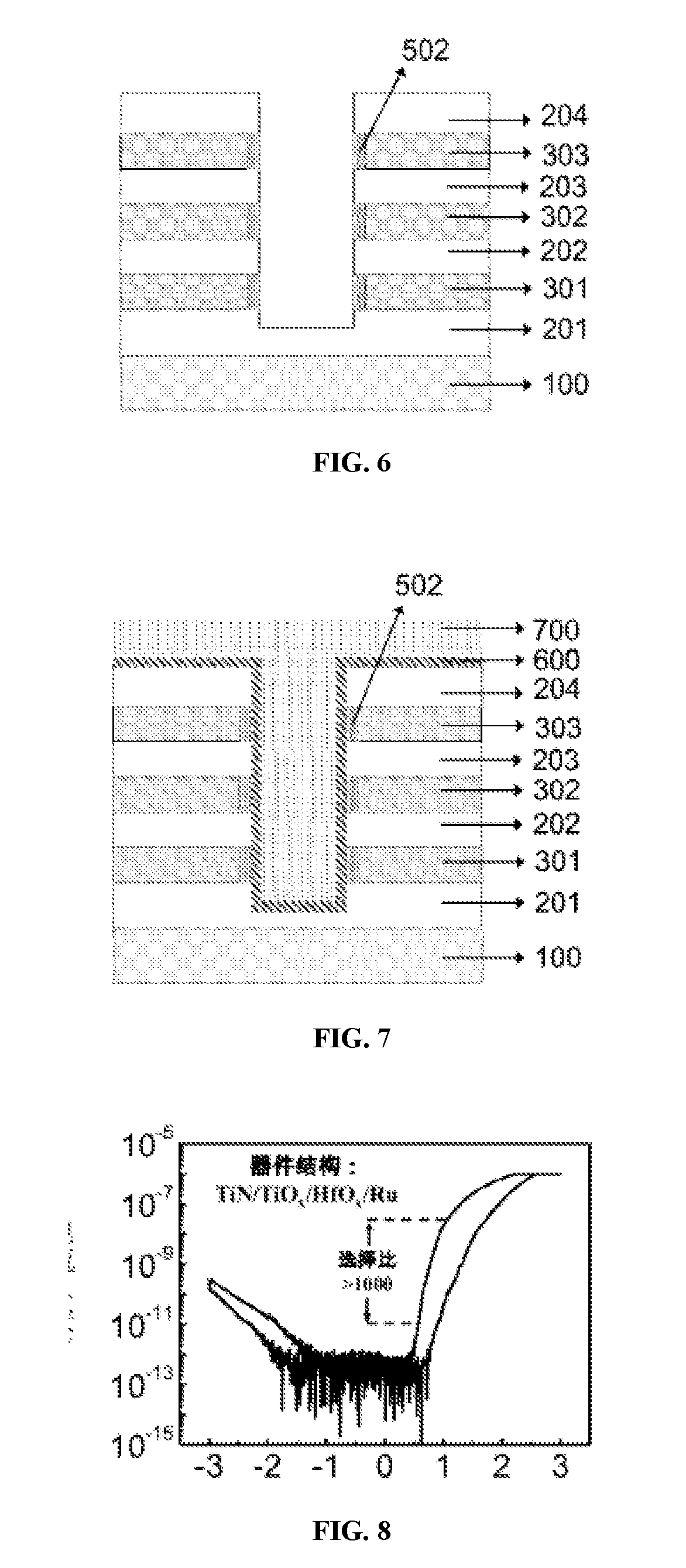

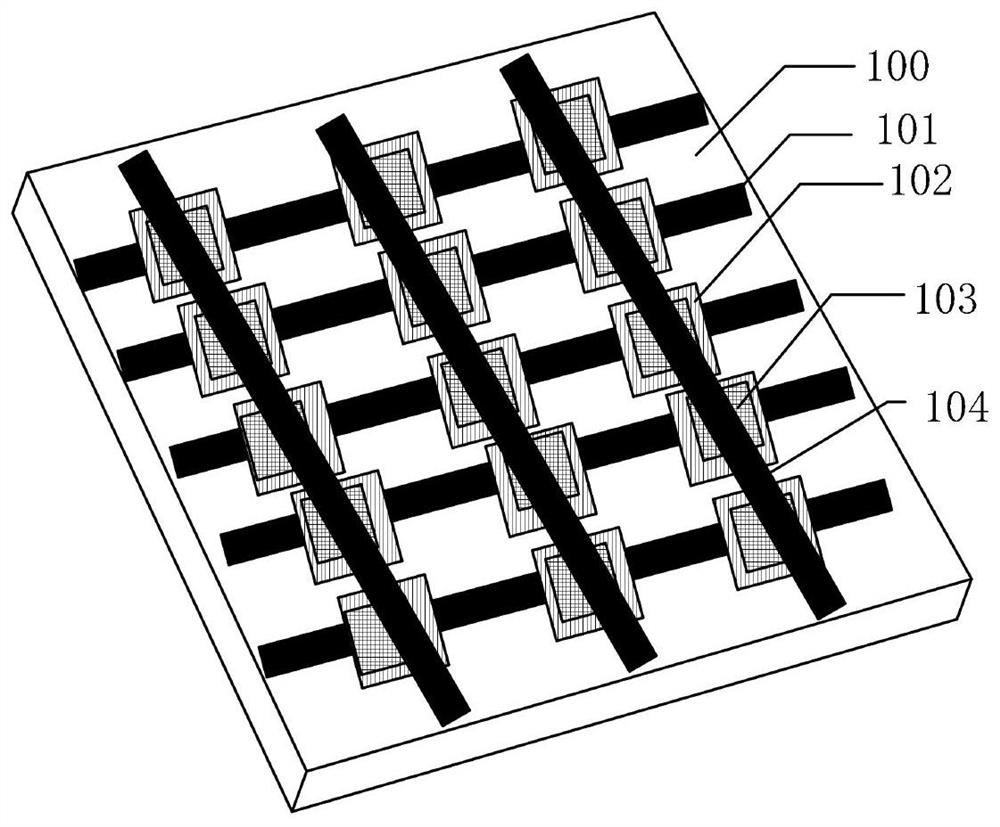

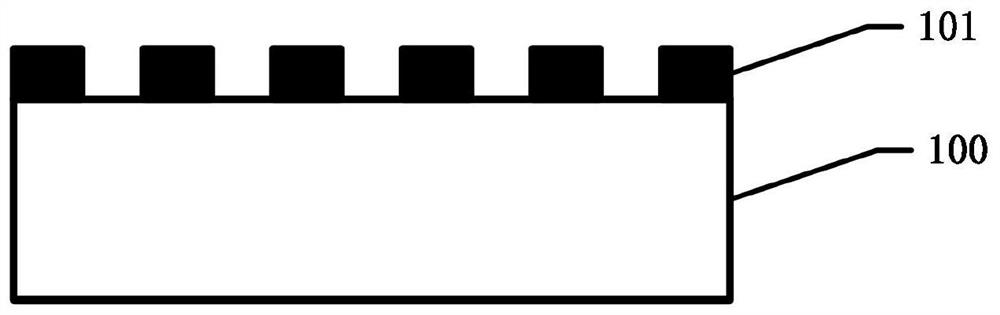

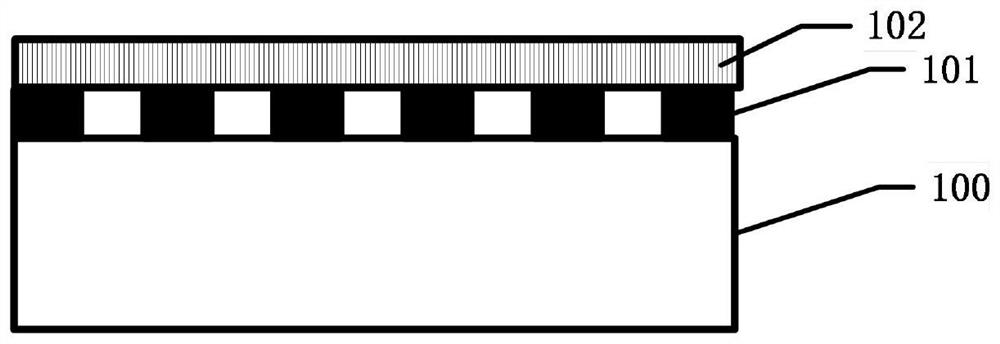

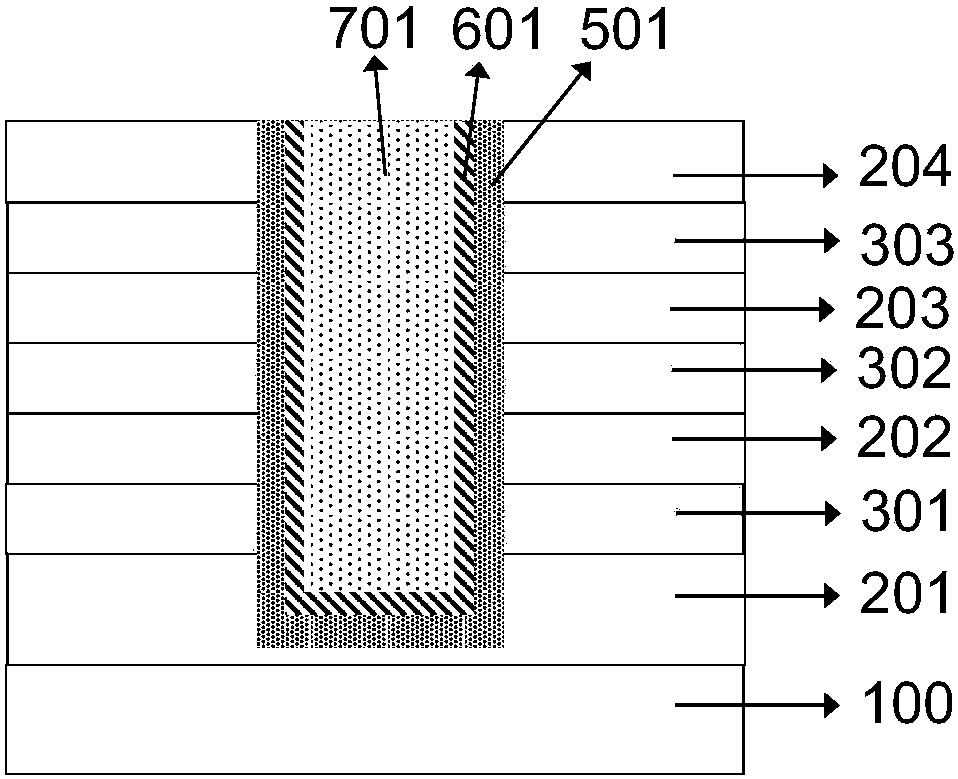

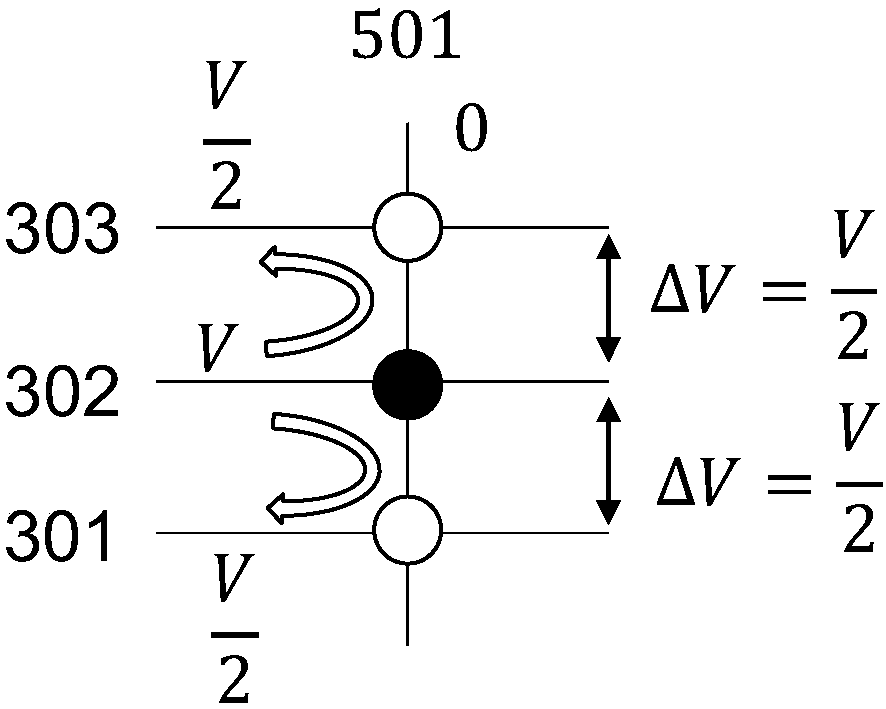

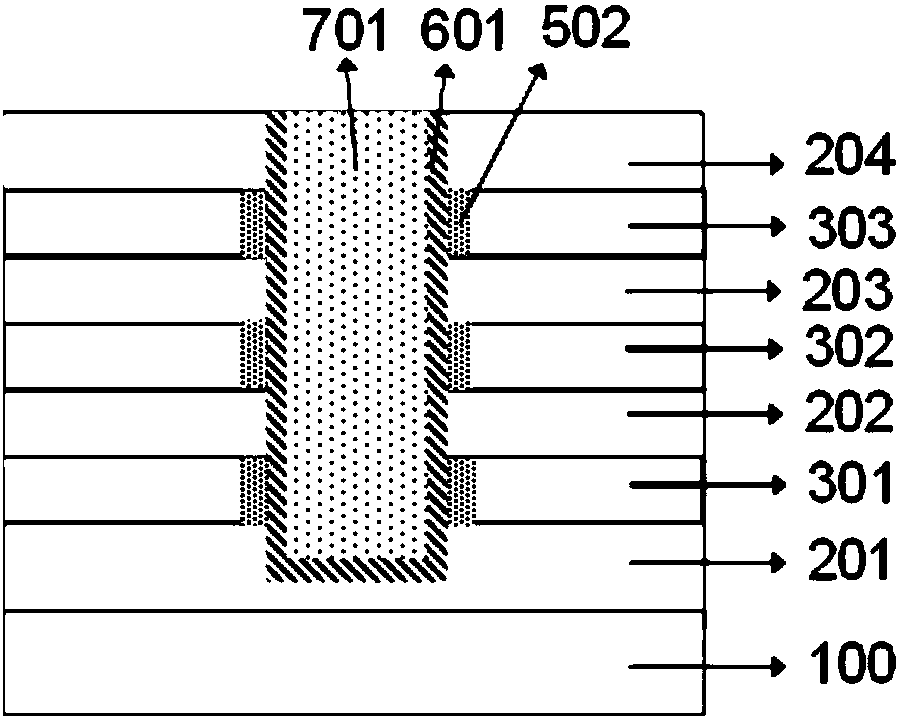

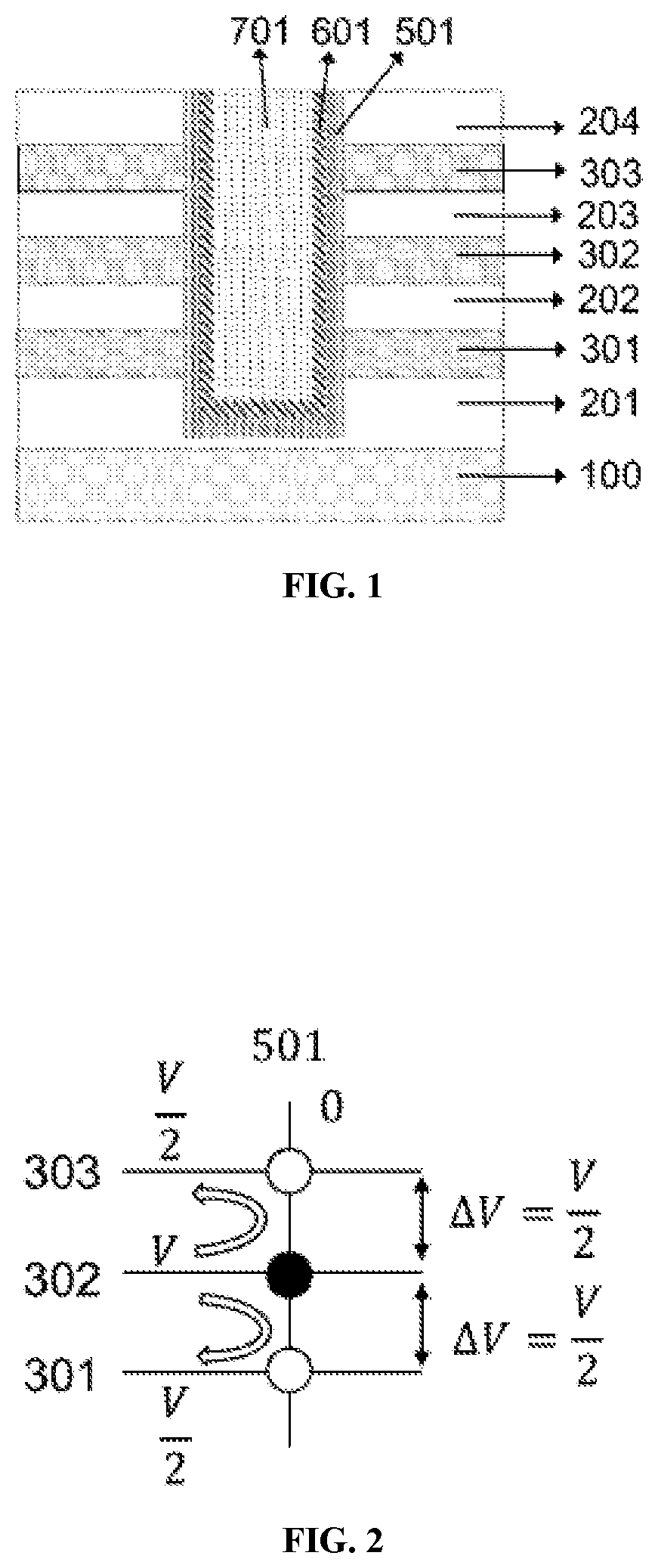

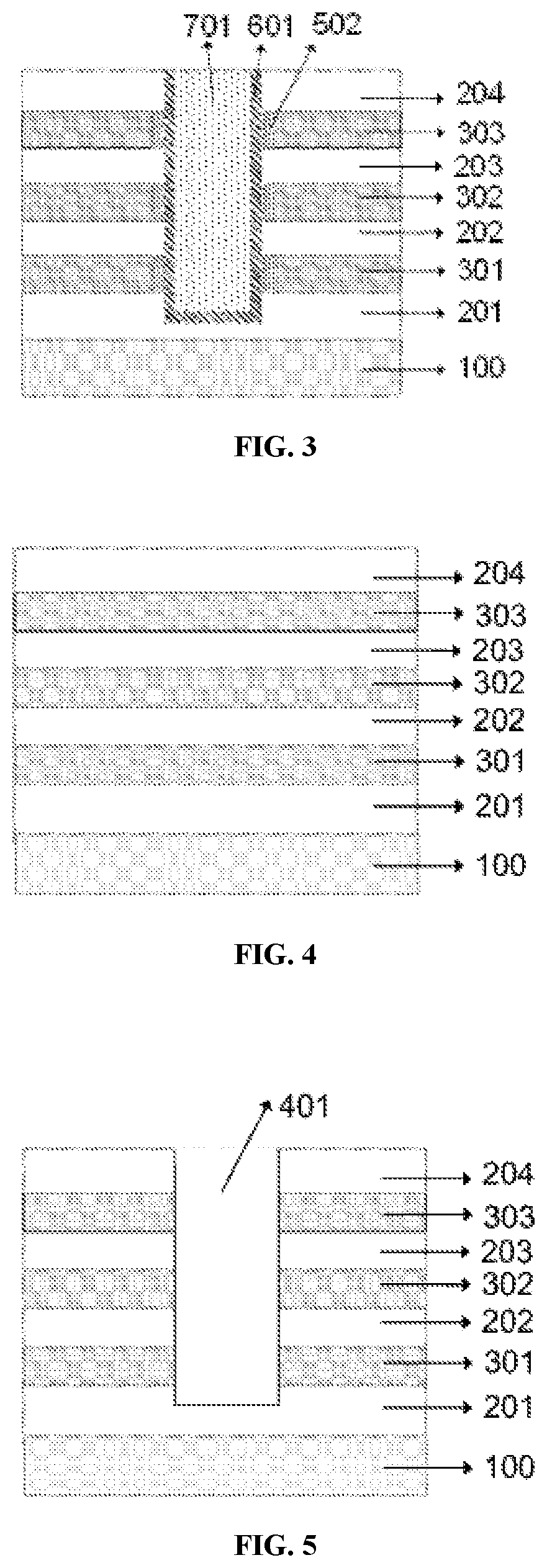

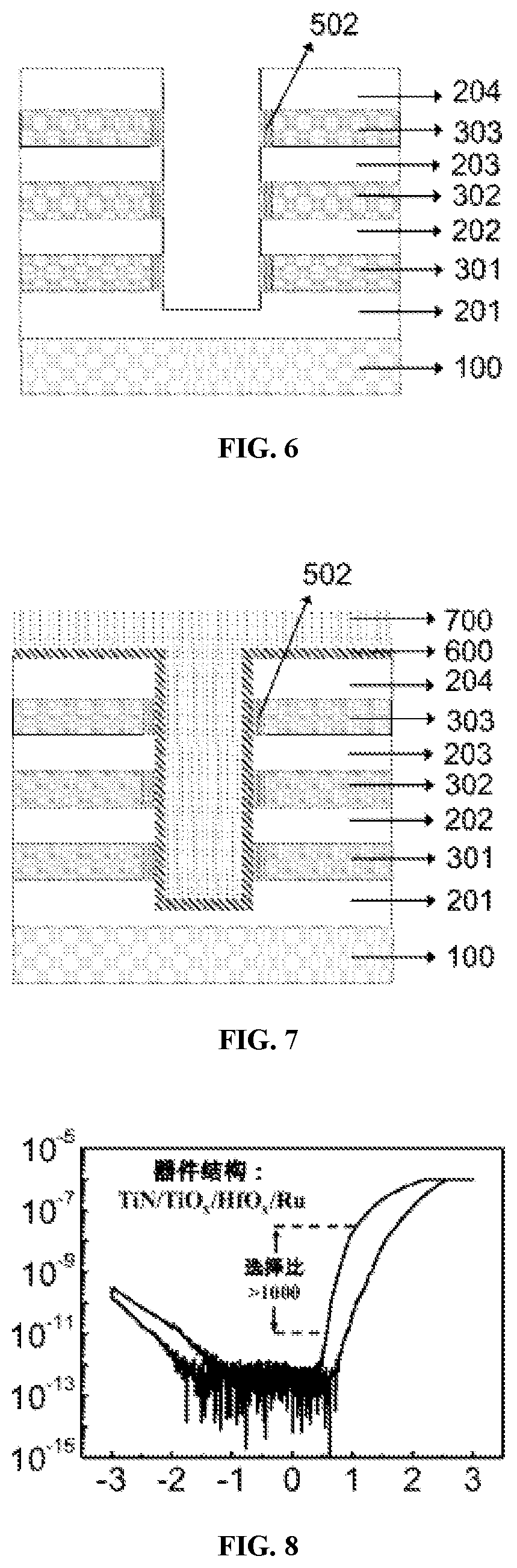

Self-gating Resistive Random-Access Memory device and preparation method thereof

ActiveCN105826468APrevent leakageSolve technical problems of leakageSolid-state devicesSemiconductor devicesElectrical resistance and conductanceElectricity

The invention discloses a self-gating resistive random-access memory device and a preparation method thereof. The self-gating resistive random-access memory device includes: a lower electrode; an insulating medium layer which is in perpendicular crossing arrangement with the lower electrode so as to form a stacked composition. The stacked composition is provided therein with a vertical groove; a gating layer which is generated on the lower electrode through a self-alignment technique, in which an interlayer electric leakage channel which passes by the gating layer is isolated by the insulating medium layer; a resistance transferring layer which is disposed inside the vertical groove and is connected to the insulating medium layer and the gating layer; an upper electrode which is arranged inside the resistance transferring layer. The memory device provided by the technical solution, generates the gating layer on the lower electrode through the self-alignment technique, allows the interlayer electric leakage channel which passes the gating layer to be insulated by the insulating medium layer, and prevents upper and lower word lines from leaking electricity through the gating layer, which address the problem of electric leakage among the upper and lower word lines of the self-gating resistive random-access memory device and increase reliability of the device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

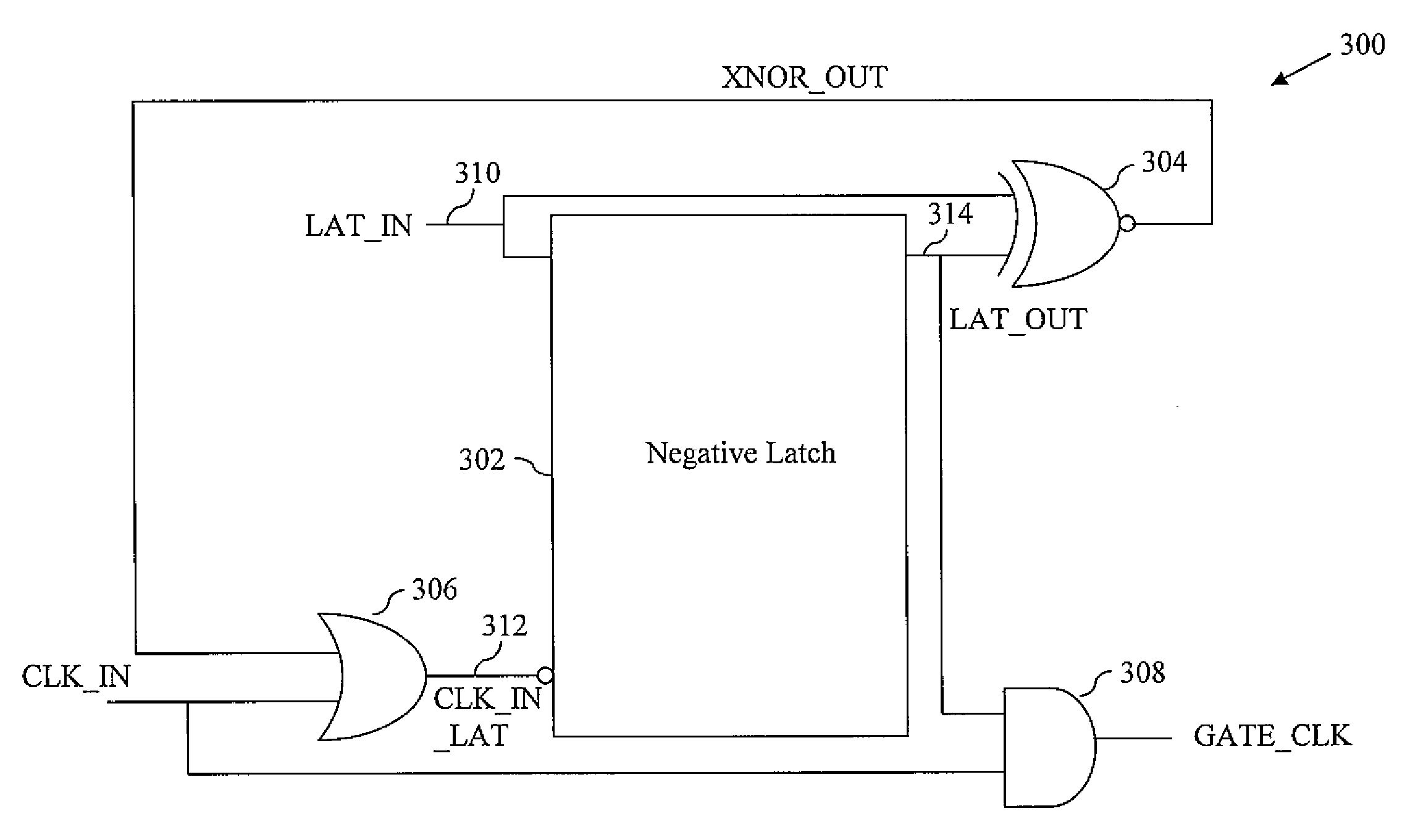

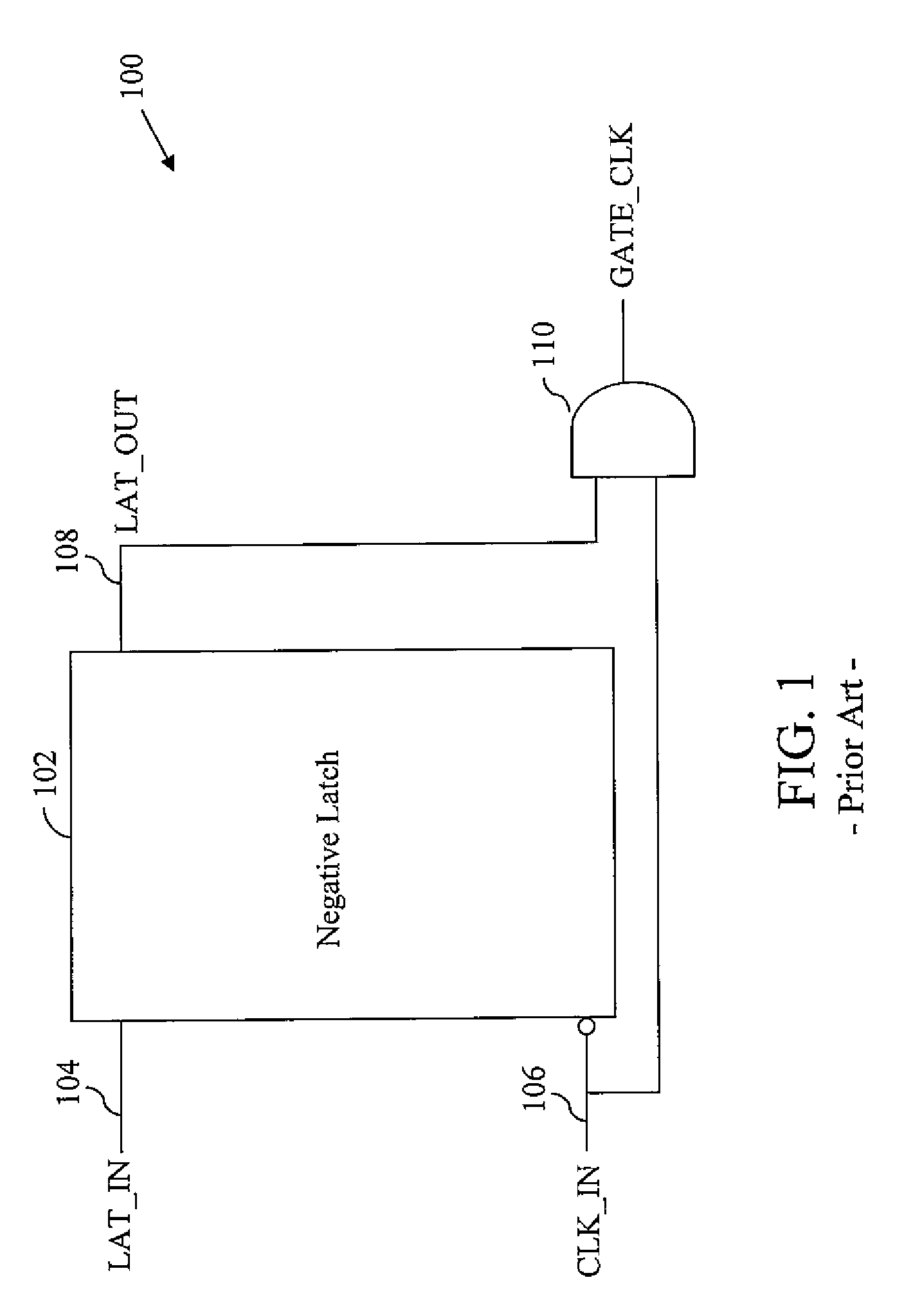

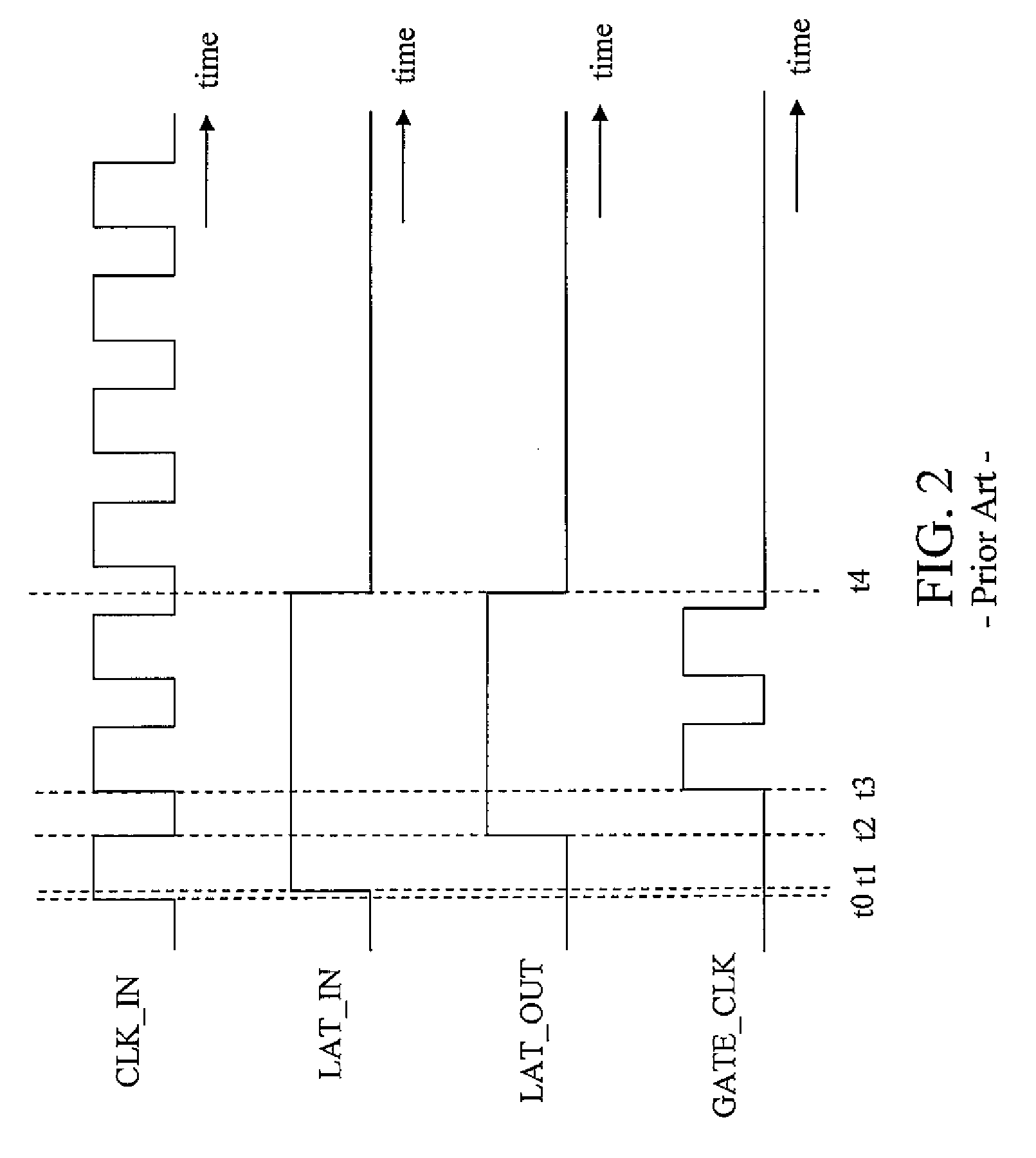

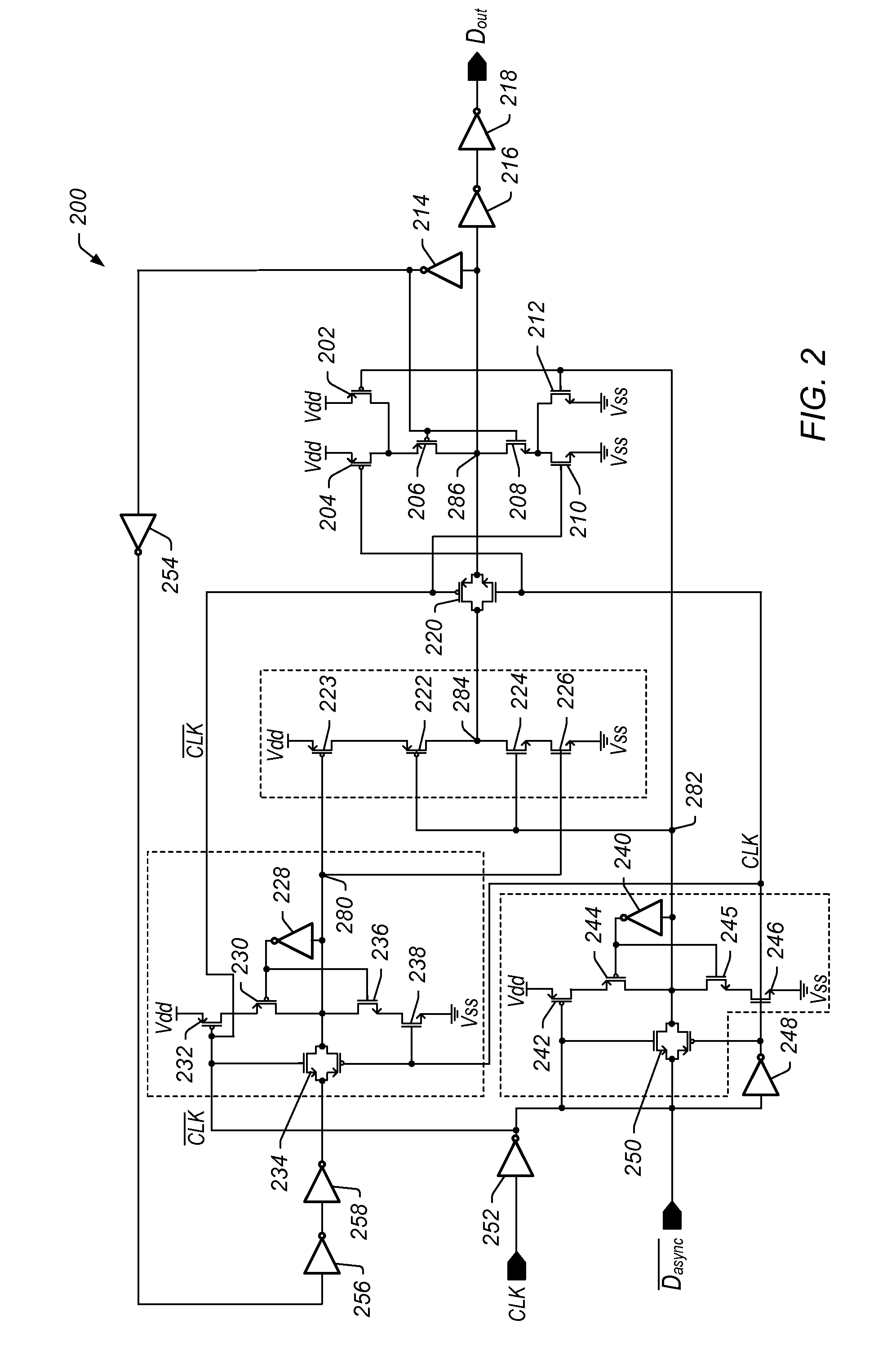

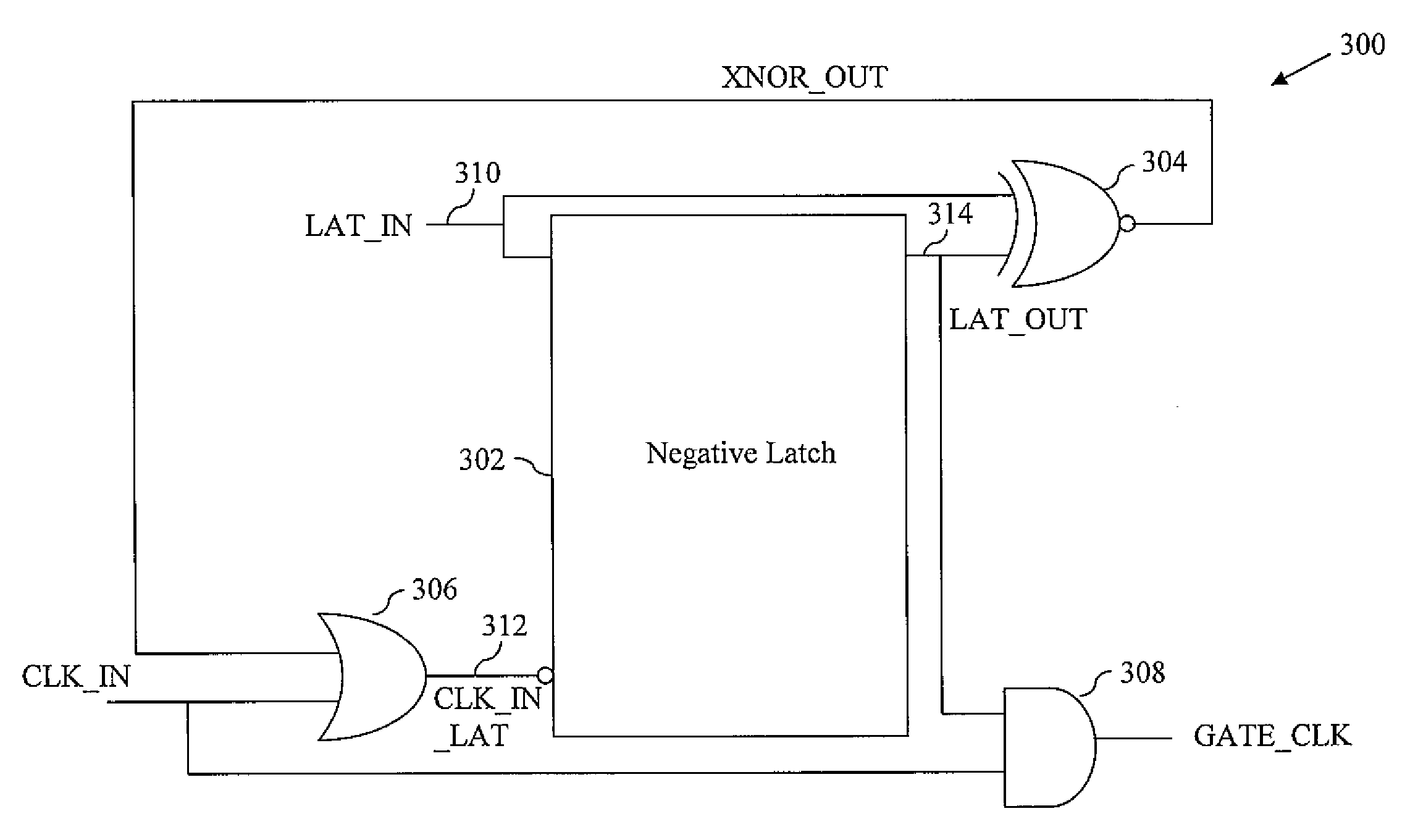

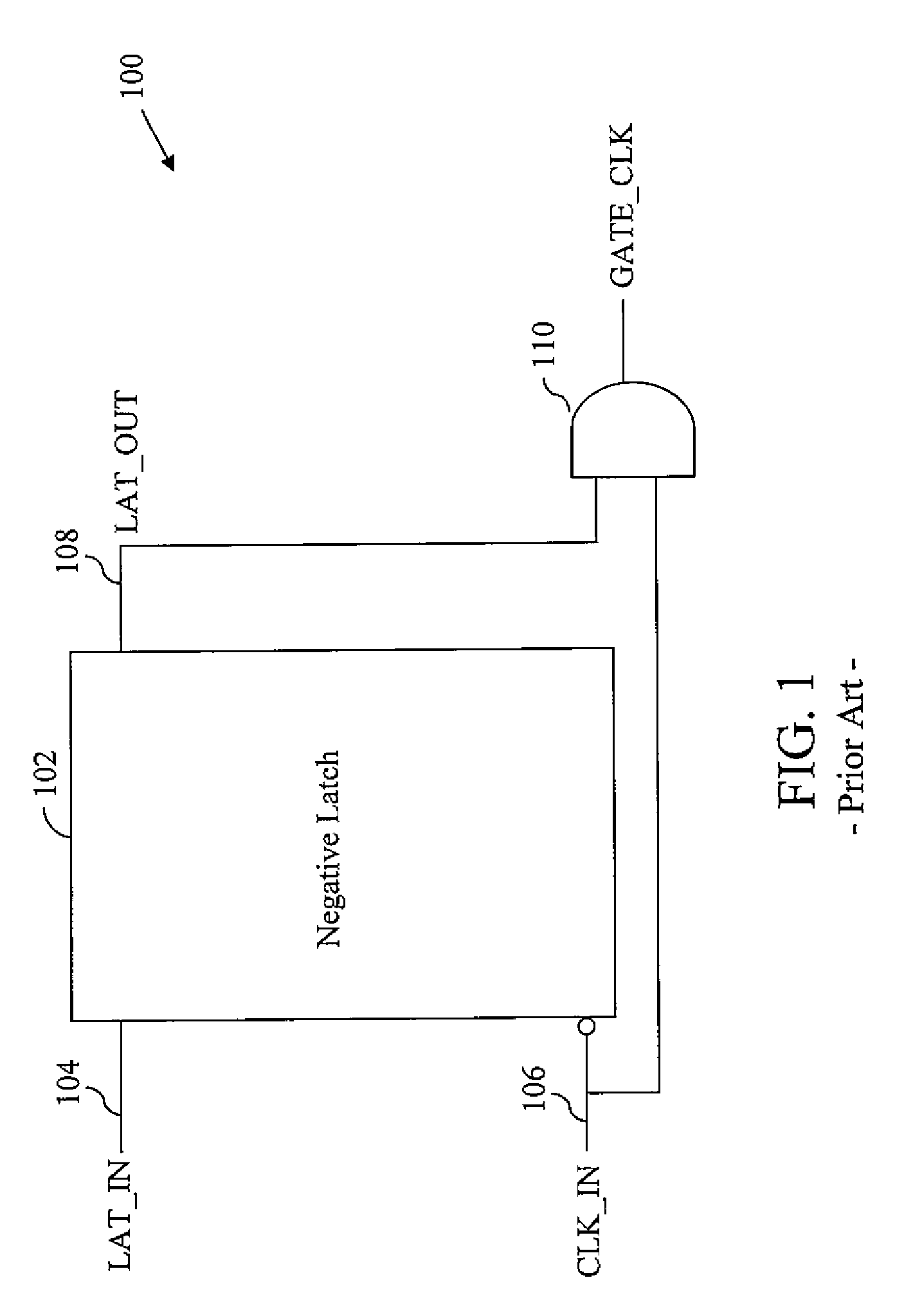

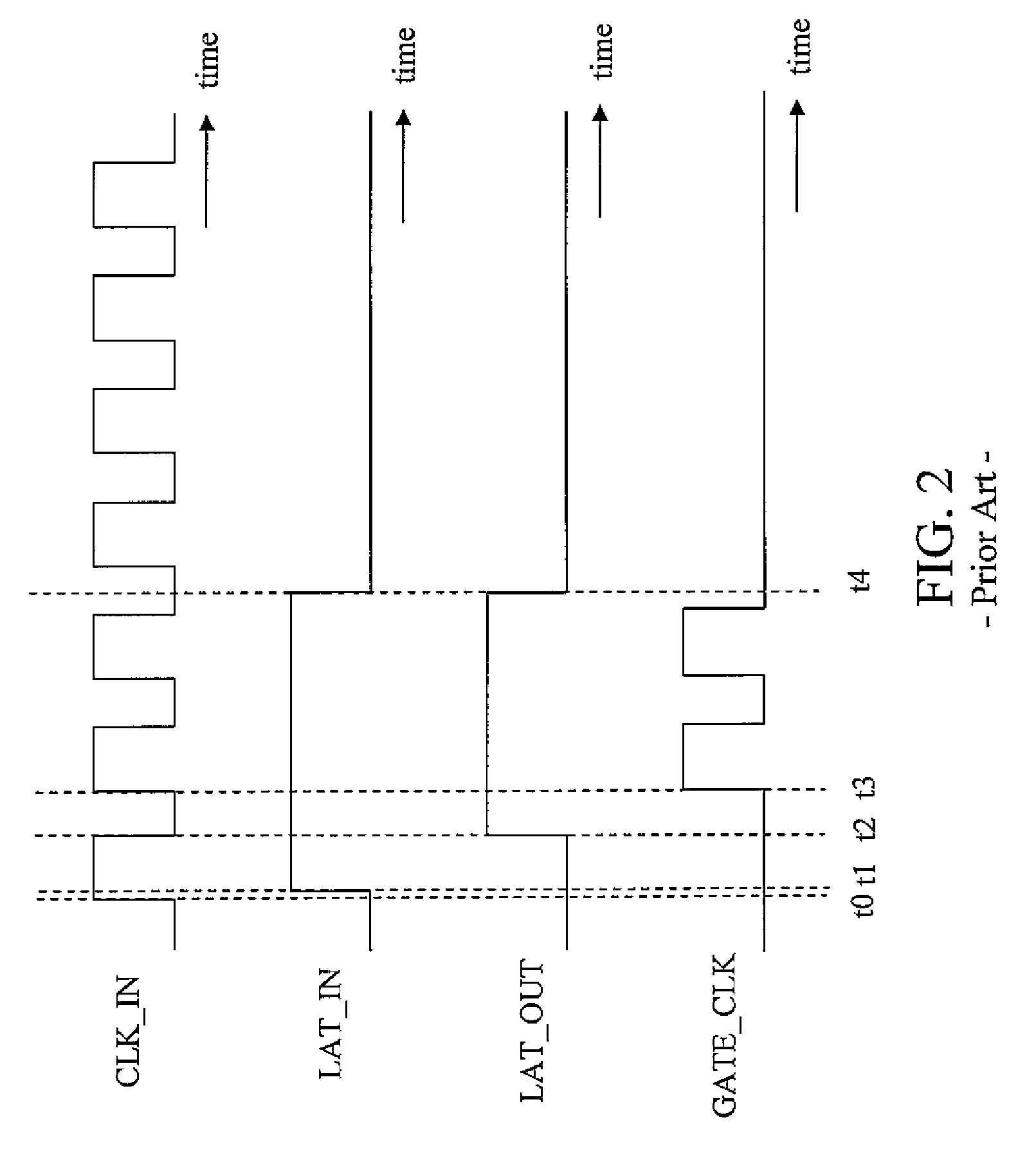

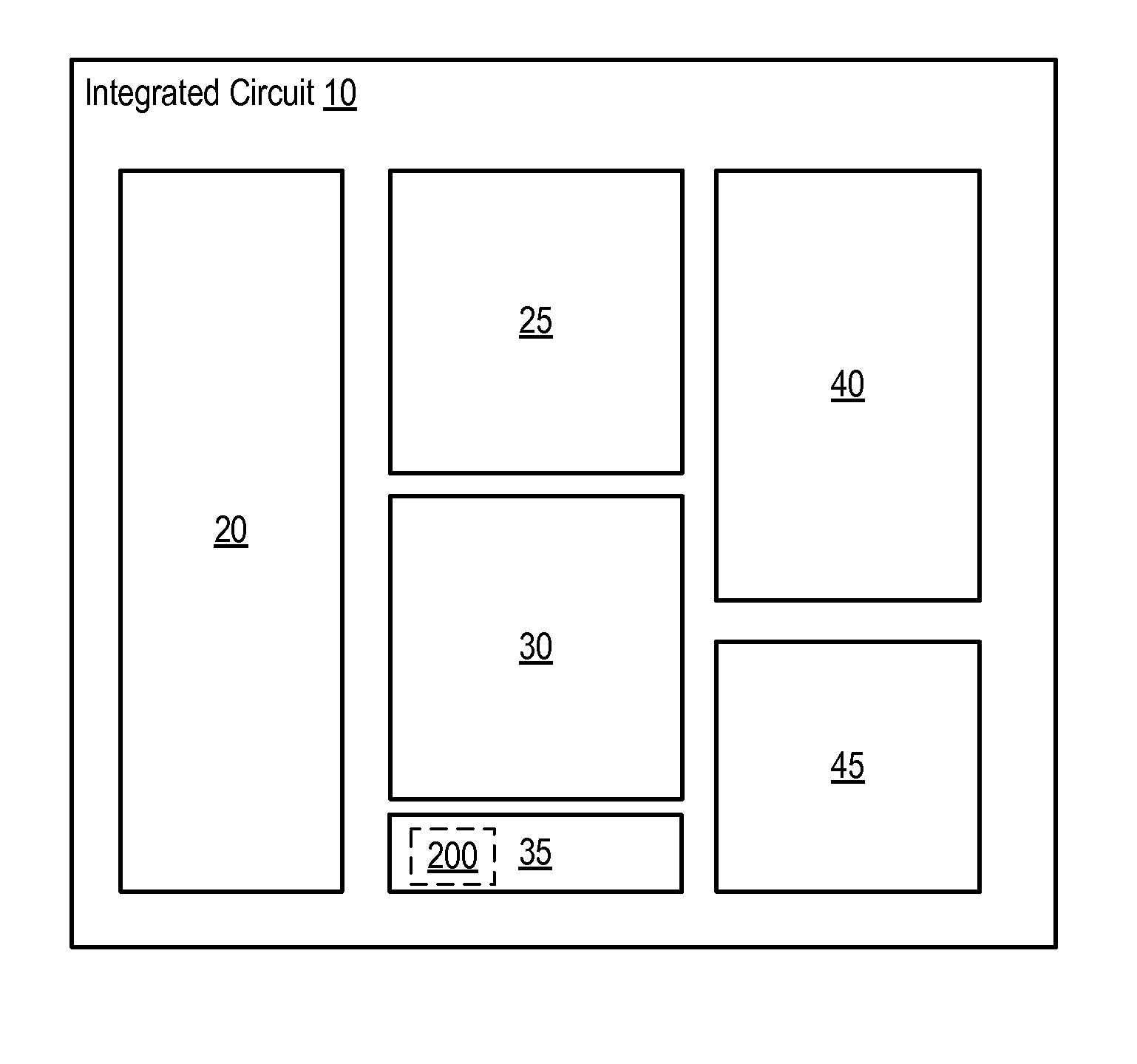

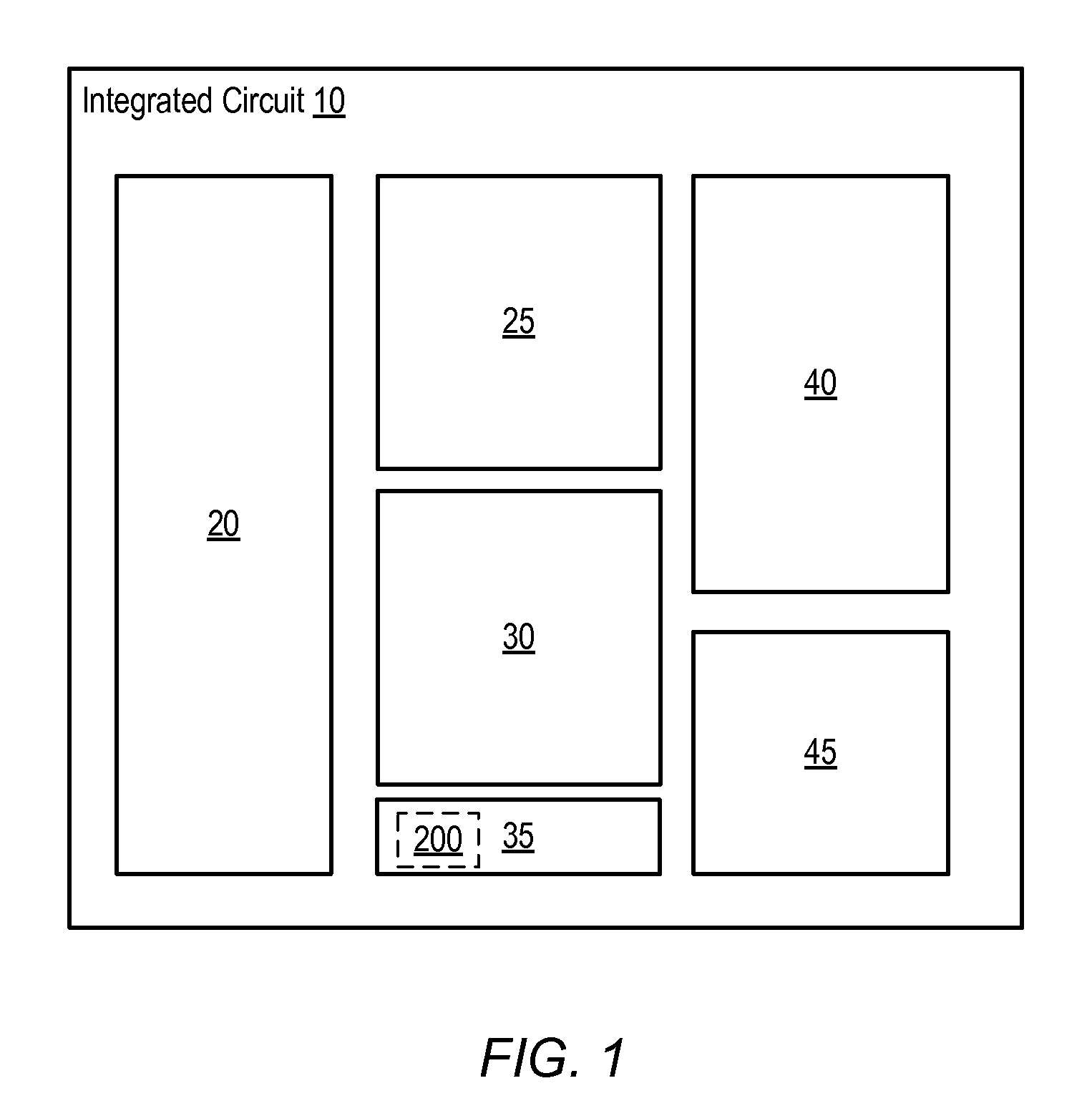

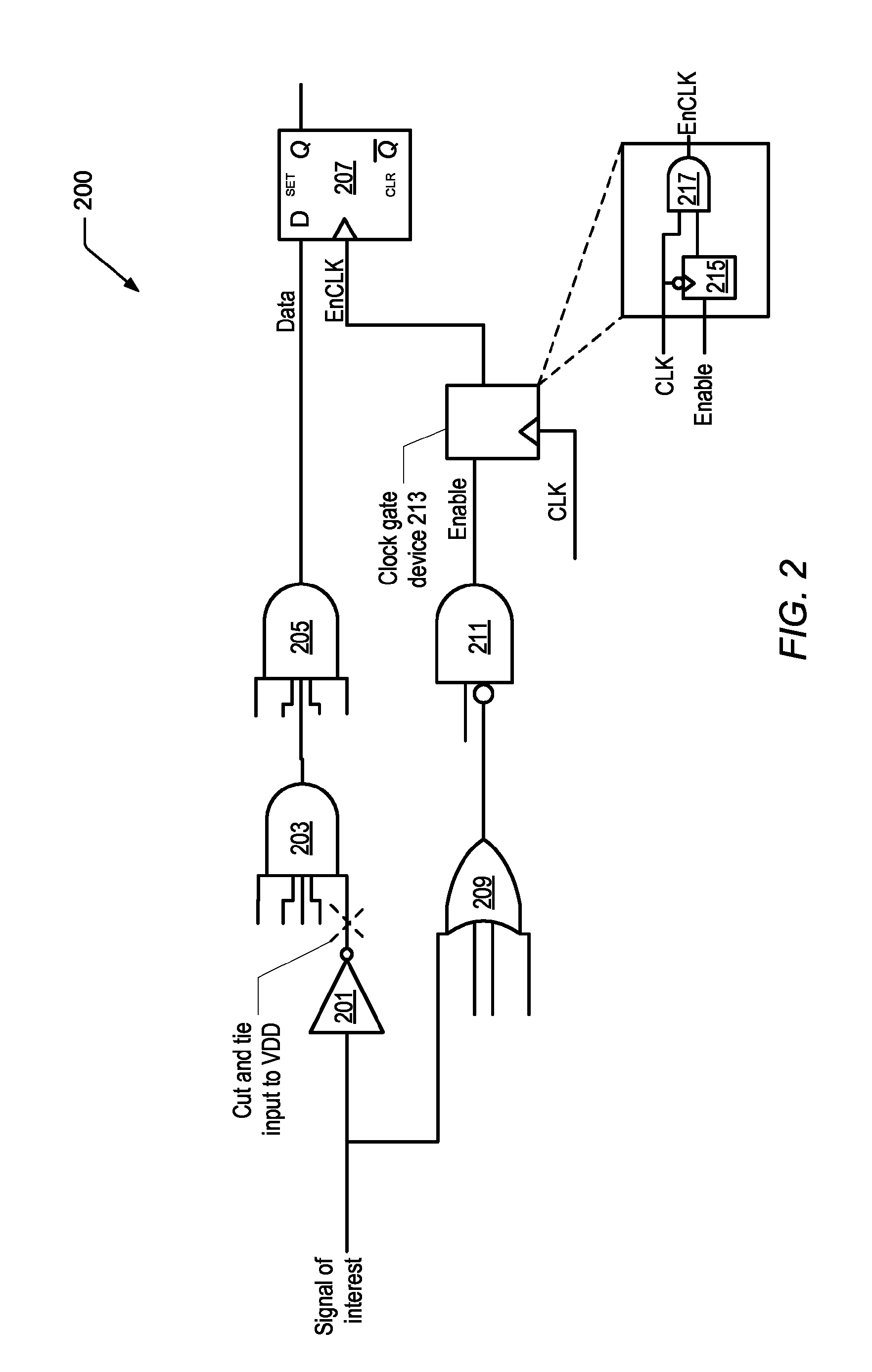

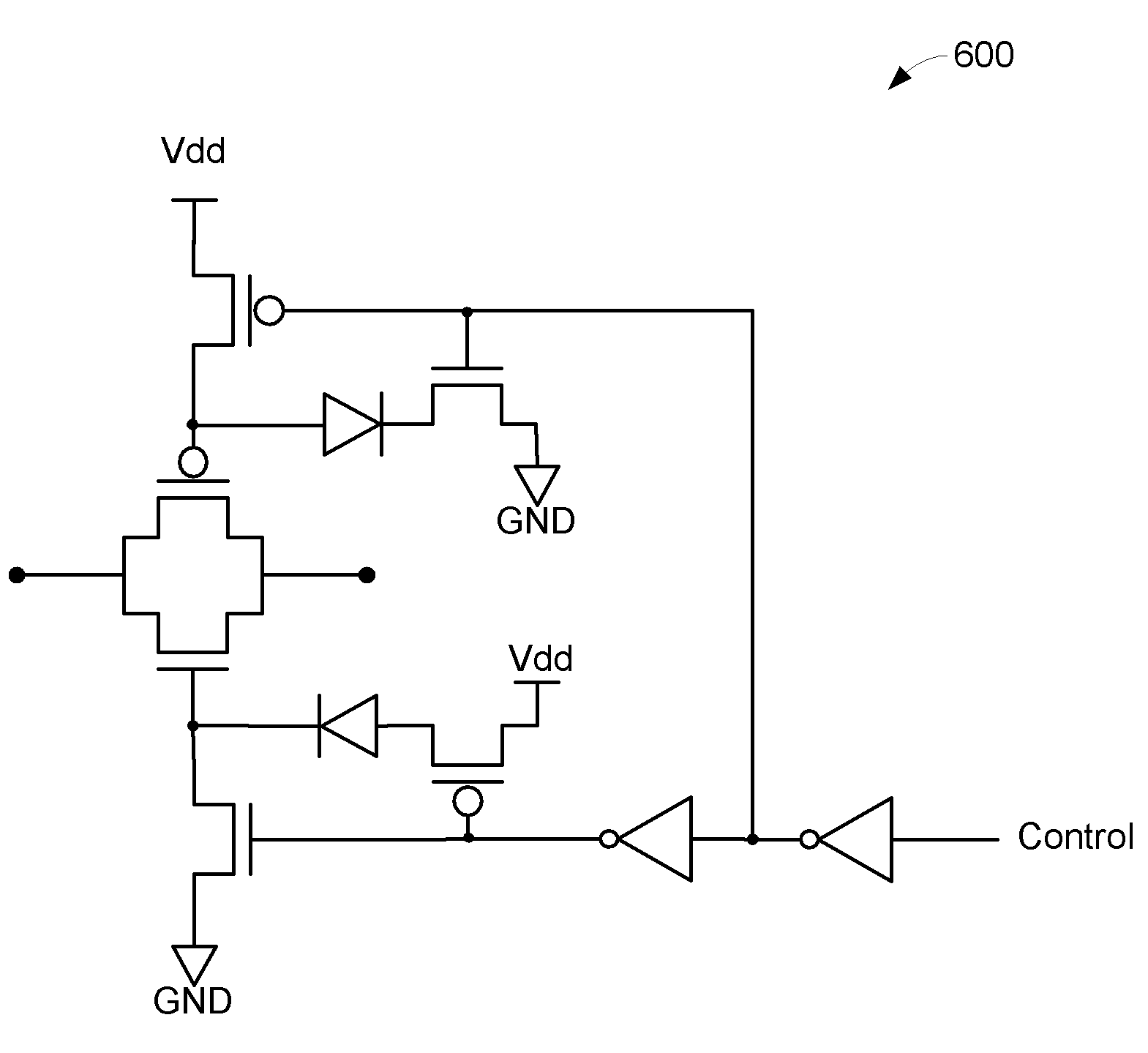

Low power, self-gated, pulse triggered clock gating cell

ActiveUS20100109707A1Power reduction by control/clock signalDuration/width modulated pulse demodulationEngineeringLogic circuitry

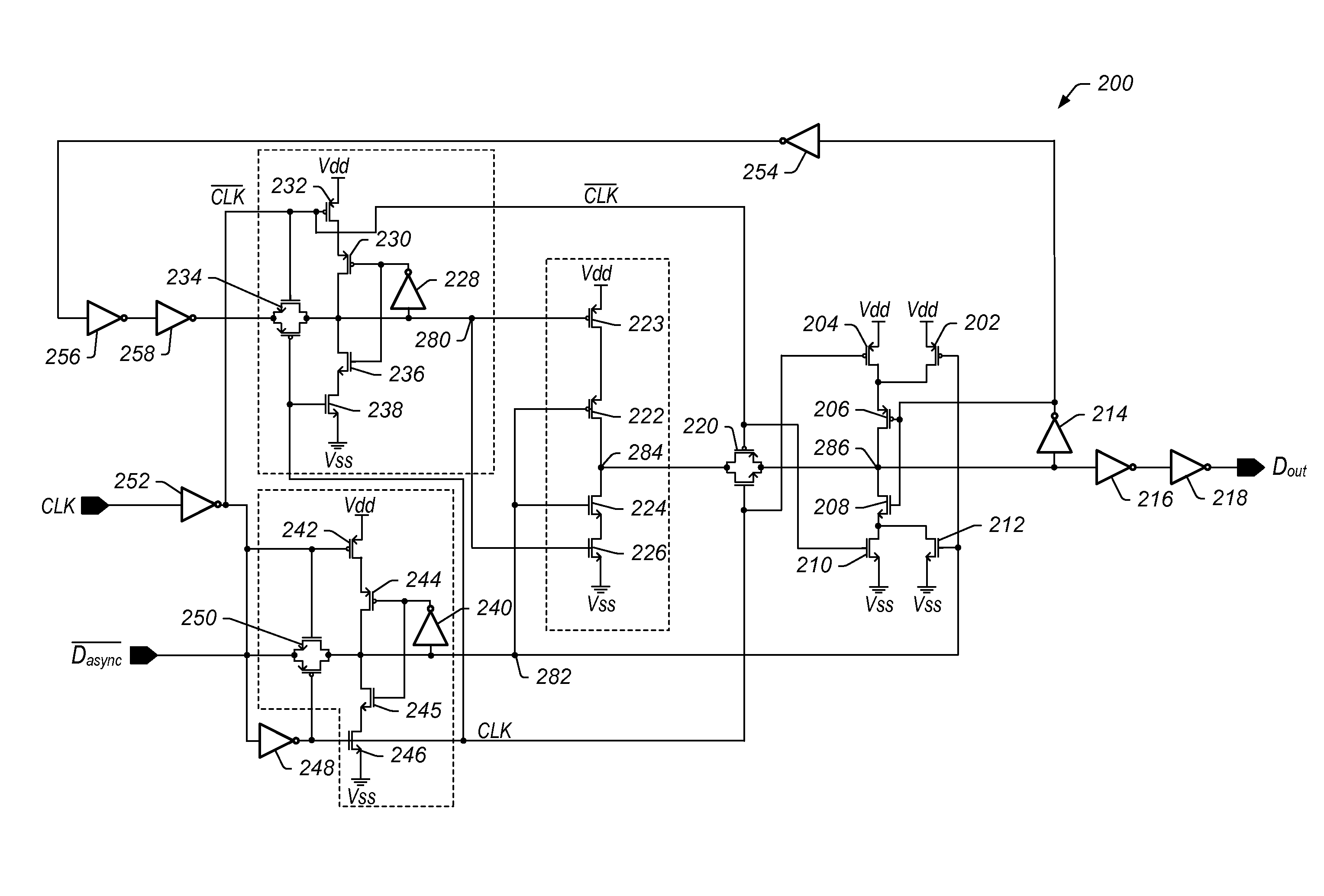

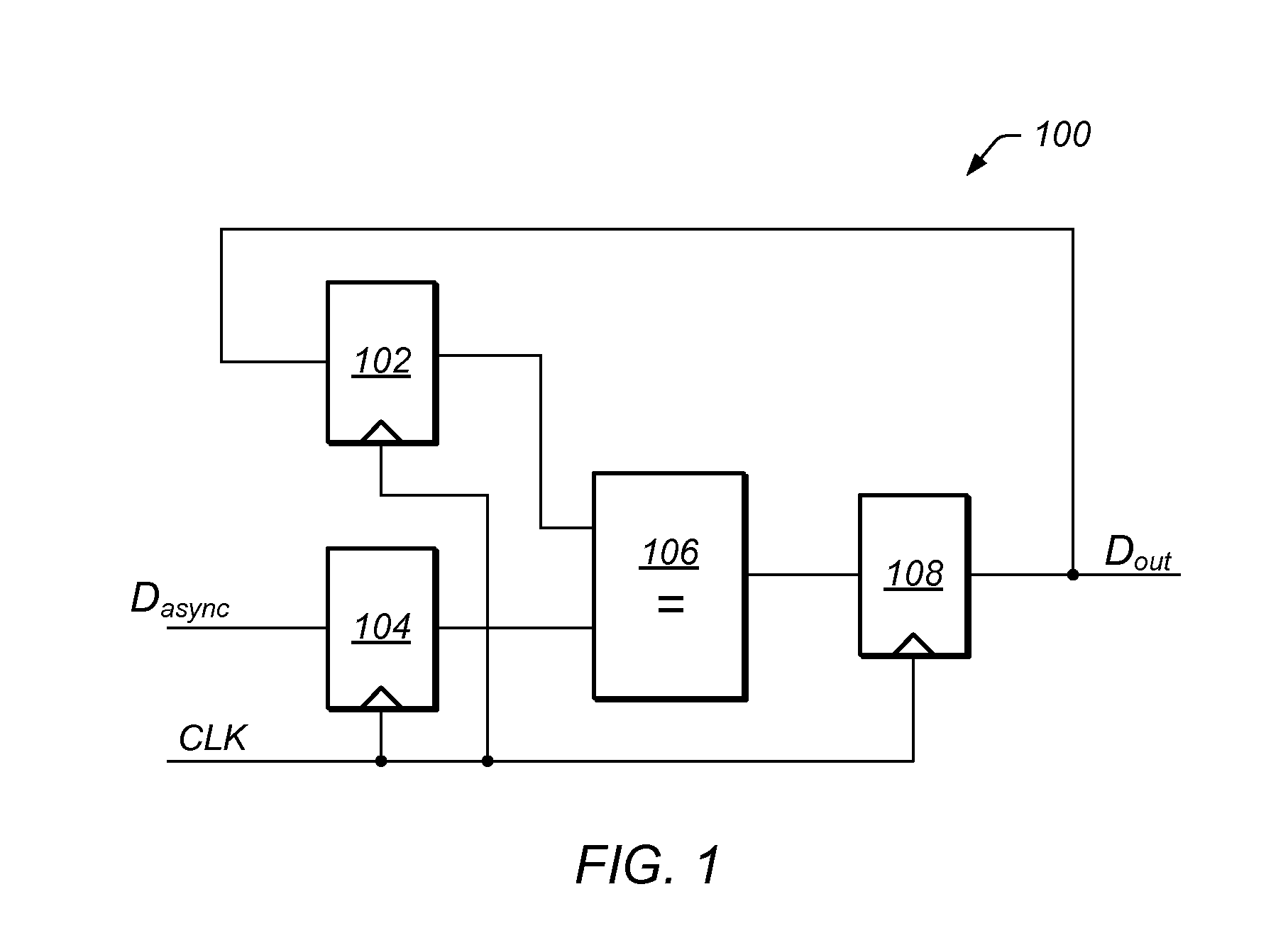

A clock gating cell for gating clock signals includes a latch circuit, a comparison logic circuit, a first logic circuit, and a second logic circuit. An input signal is provided to the latch circuit. An input clock signal is provided to the first logic circuit. The first logic circuit switches the input clock signal based on a comparison signal generated by the comparison logic circuit, thereby generating a latch clock signal. The latch clock signal switches between a first state and a second state only when the input signal switches between the first state and the second state, thereby preventing power loss of the clock gating cell.

Owner:NXP USA INC

Methods and software for self-gating a set of images

InactiveUS7142703B2Enhance the imageImproves calcium scoringUltrasonic/sonic/infrasonic diagnosticsElectrocardiographyEcg signalProjection image

Owner:MERATIVE US LP

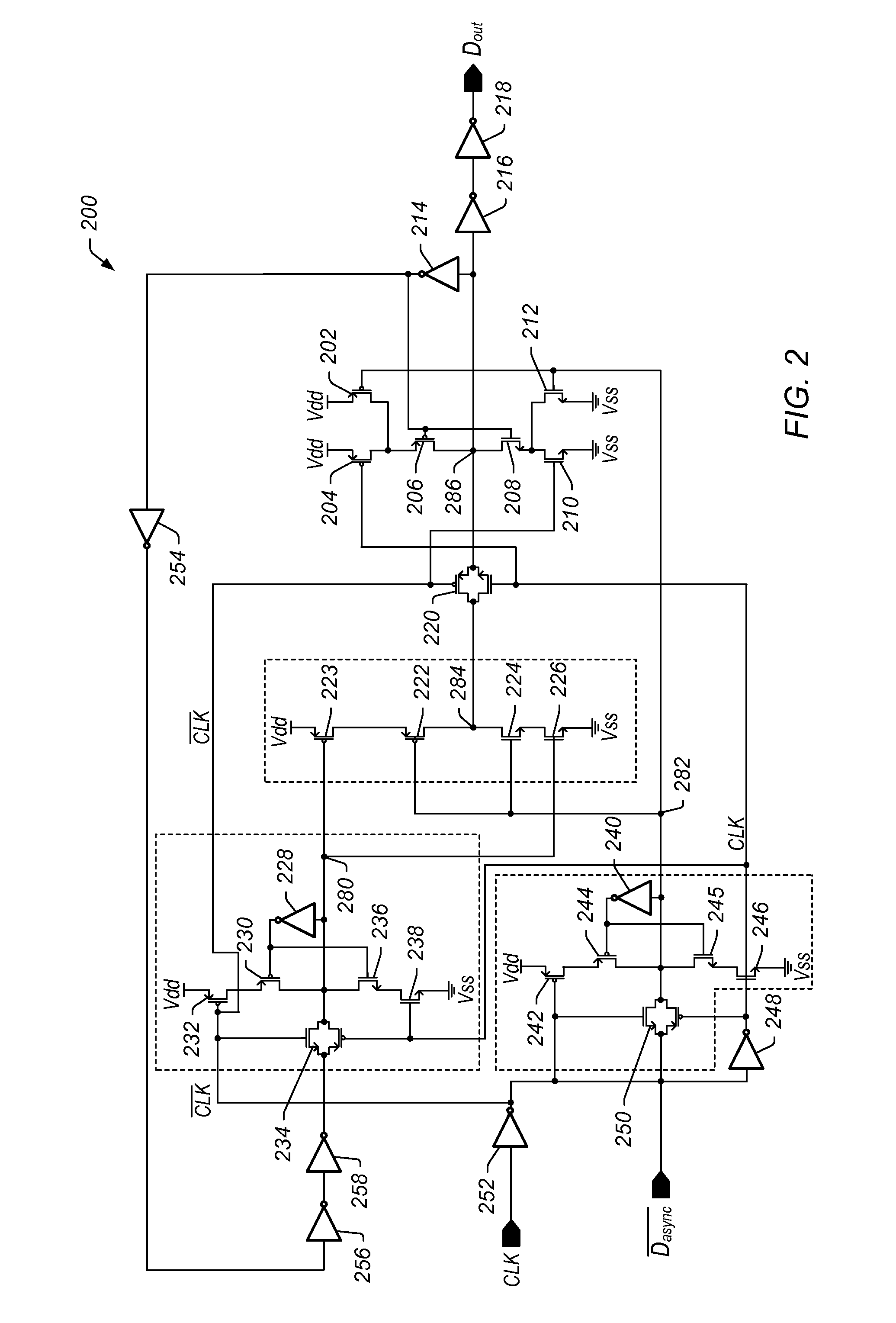

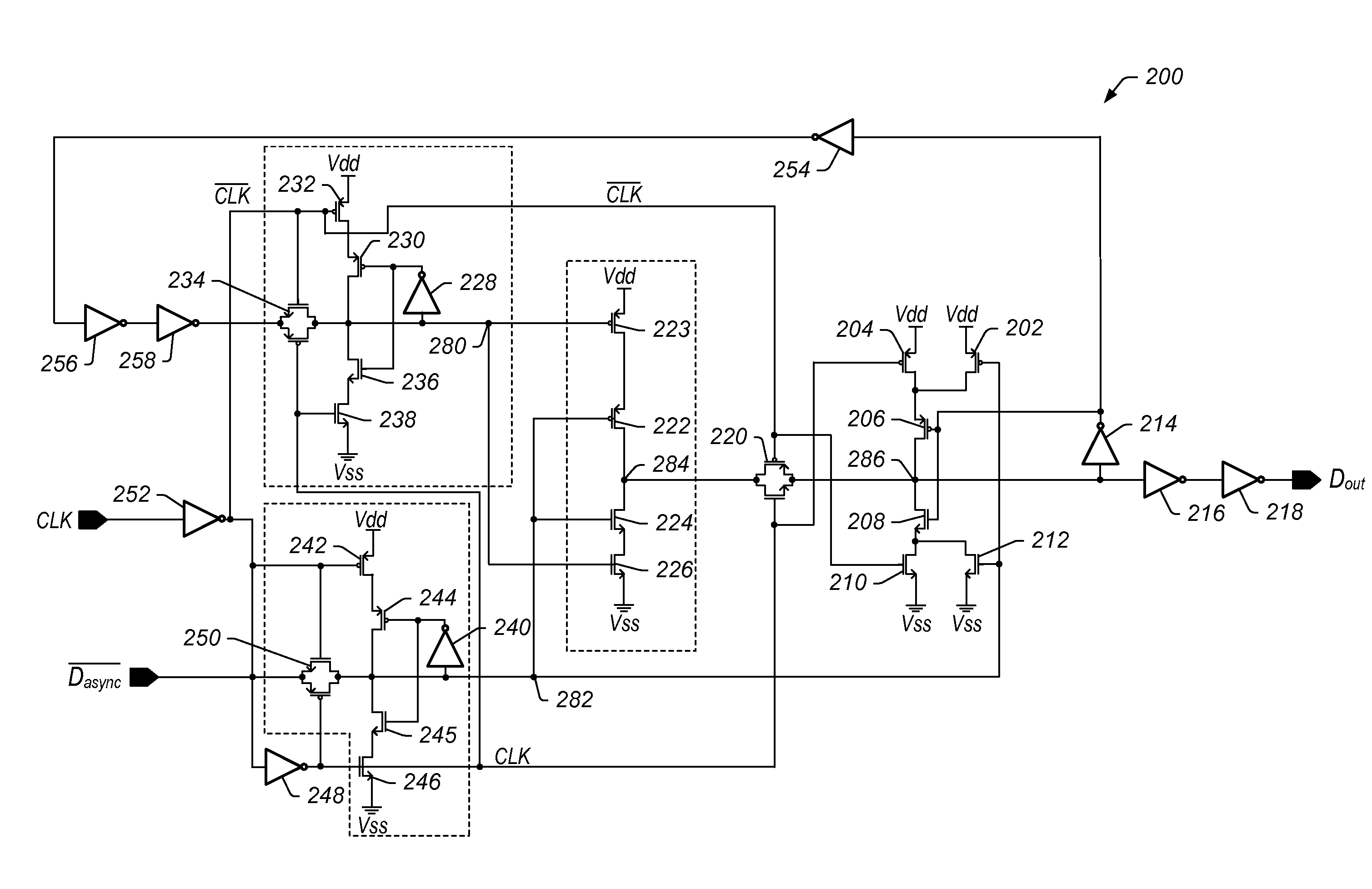

Self-gating synchronizer

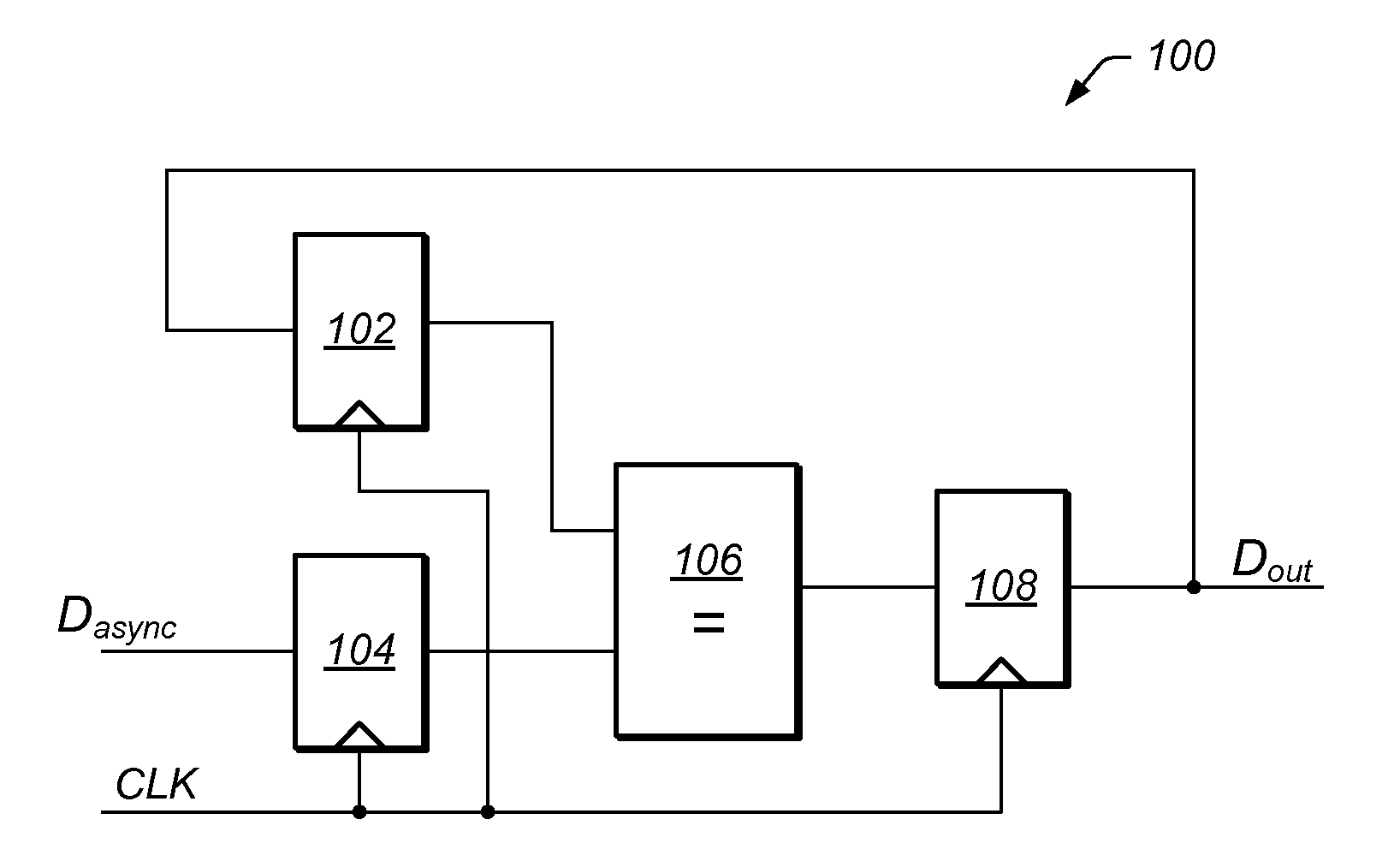

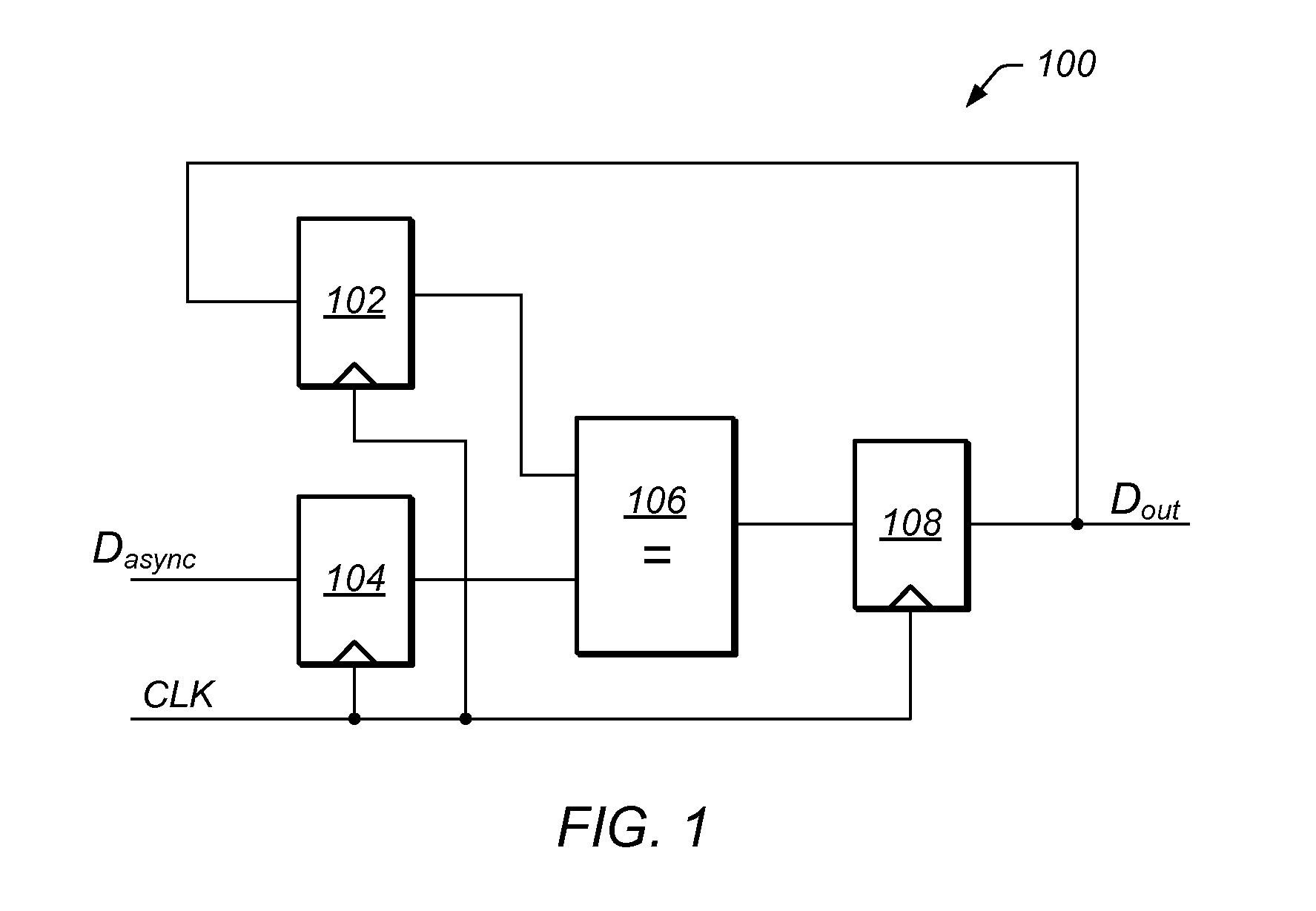

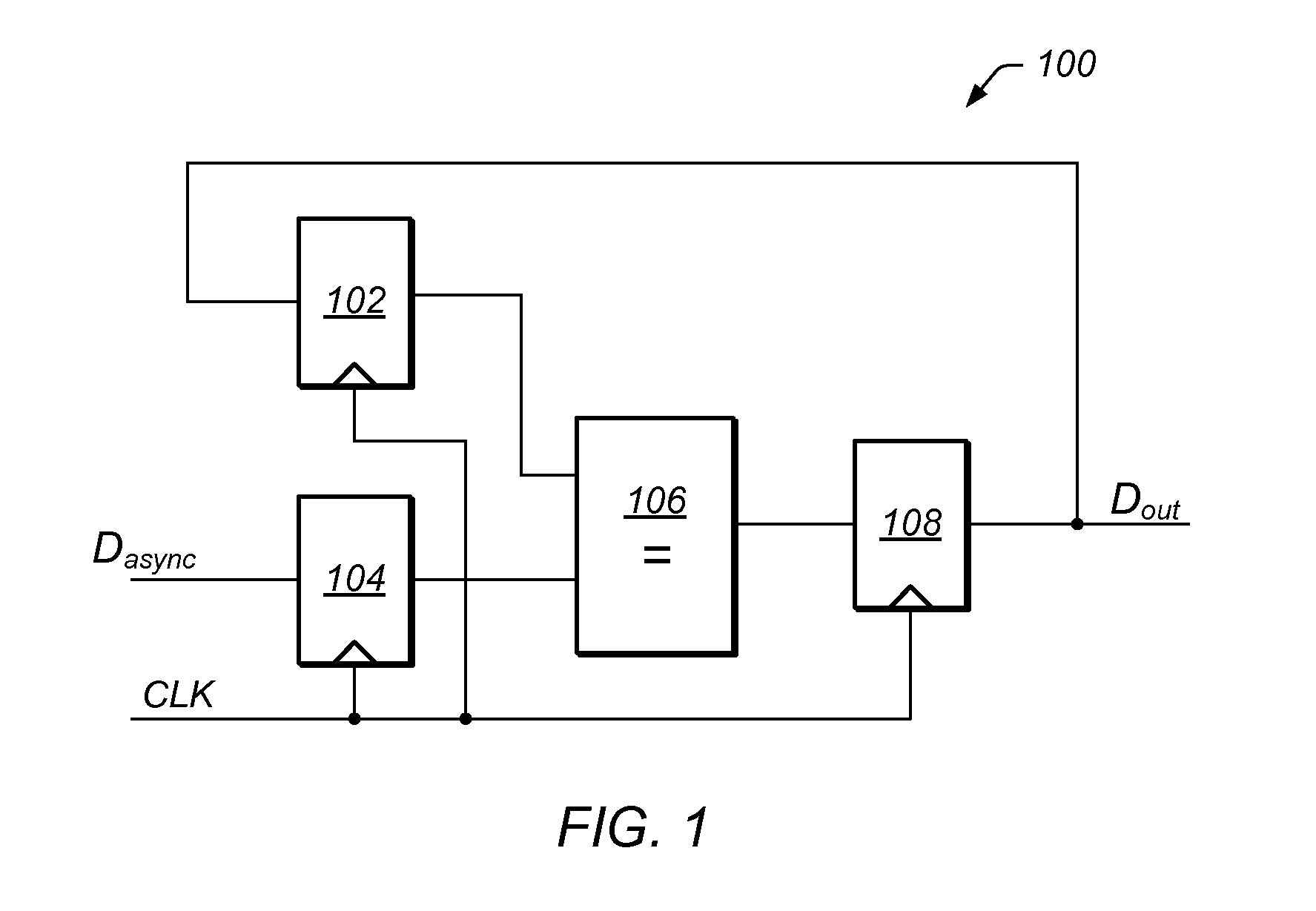

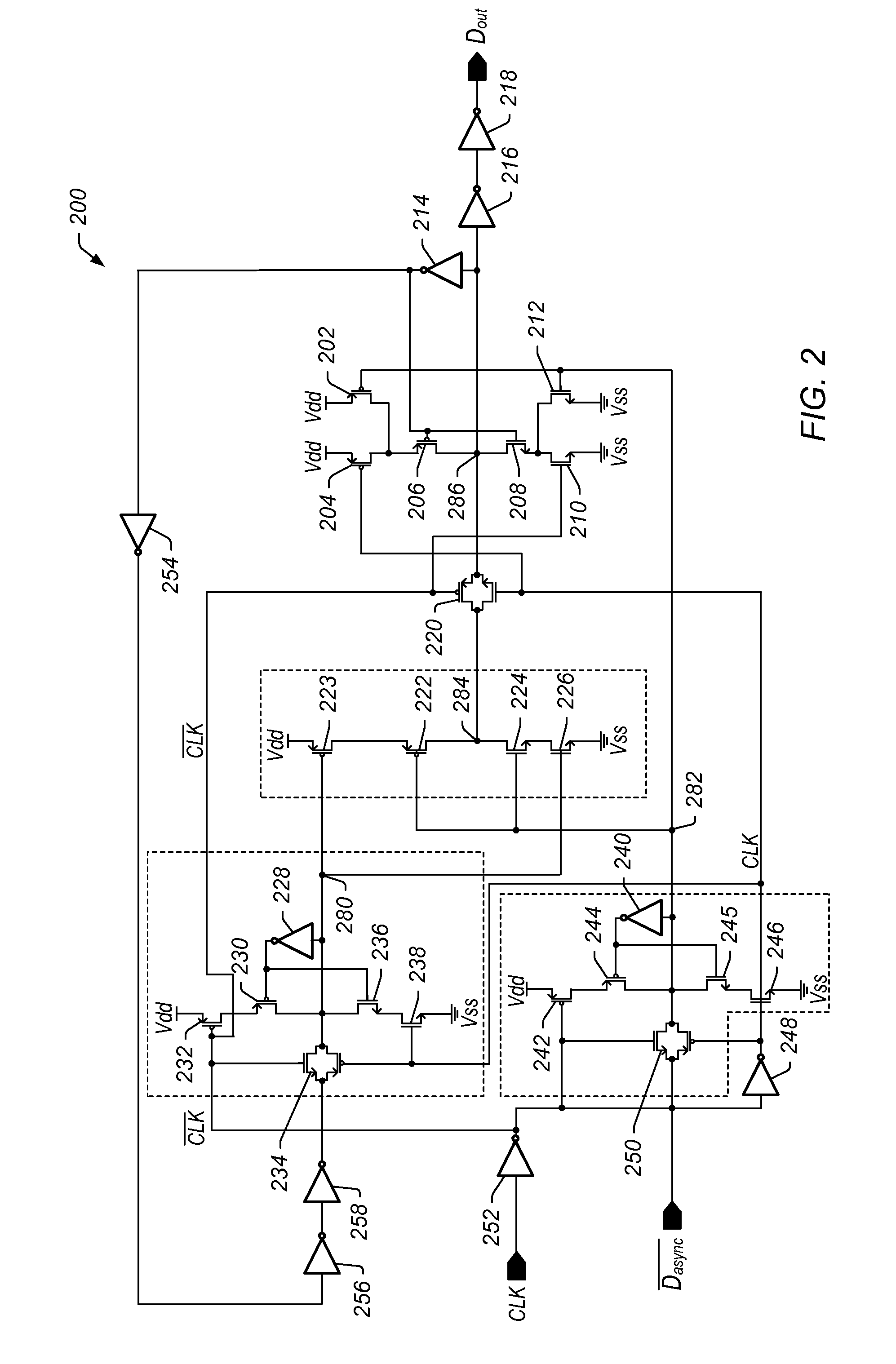

InactiveUS7977976B1Avoid contentionHinders its propagationPulse manipulationSynchronising arrangementLogic stateComputer science

A synchronizer circuit for transferring data from a source clock domain to a target clock domain. A first latch in the target clock domain may capture a data value corresponding to current data received from the source clock domain. Under certain conditions, the first latch may enter into a metastable, or undefined logic state. A second latch may remain stable, and store a previous value corresponding to data that has most recently been transferred from the source clock domain to the target clock domain. The respective values output by the two latches may be compared by a detection circuit, and a value derived from the output value of the first latch and corresponding to the current data may be written to an output latch if the current data differs from the stored previous value. The detection circuit may also provide a defined logical value to the output latch even if the first latch is in a metastable state.

Owner:APPLE INC

Methods and apparatus for terahertz wave amplitude modulation

InactiveUS8836446B2Amplitude modulation detailsElectromagnetic wave modulationA wave amplitudeCapacitance

A wave amplitude modulator for modulating a transmitted electromagnetic wave includes one or multiple self-gated capacitively coupled pair(s) of electron layers such as semiconductor or semimetal layers. Two electrical contacts are placed to each layer of electrons of the self-gated pair(s), and a power source is electrically connected to them. The power source, by varying the voltage applied between layers of electrons, tunes the electron density thereof, thereby adjusting the optical conductivity thereof, and the change in the optical conductivity of the layers of electrons causes an amplitude modulation of the transmitted electromagnetic wave passing through the capacitively coupled layers of electrons.

Owner:UNIV OF NOTRE DAME DU LAC

Self-Gating Synchronizer

ActiveUS20110285431A1Avoid contentionHinders its propagationPulse automatic controlPulse manipulationLogic stateData value

A synchronizer circuit for transferring data from a source clock domain to a target clock domain. A first latch in the target clock domain may capture a data value corresponding to current data received from the source clock domain. Under certain conditions, the first latch may enter into a metastable, or undefined logic state. A second latch may remain stable, and store a previous value corresponding to data that has most recently been transferred from the source clock domain to the target clock domain. The respective values output by the two latches may be compared by a detection circuit, and a value derived from the output value of the first latch and corresponding to the current data may be written to an output latch if the current data differs from the stored previous value. The detection circuit may also provide a defined logical value to the output latch even if the first latch is in a metastable state.

Owner:APPLE INC

Low power, self-gated, pulse triggered clock gating cell

ActiveUS7808279B2Power reduction by control/clock signalDuration/width modulated pulse demodulationLogic circuitrySelf gating

Owner:NXP USA INC

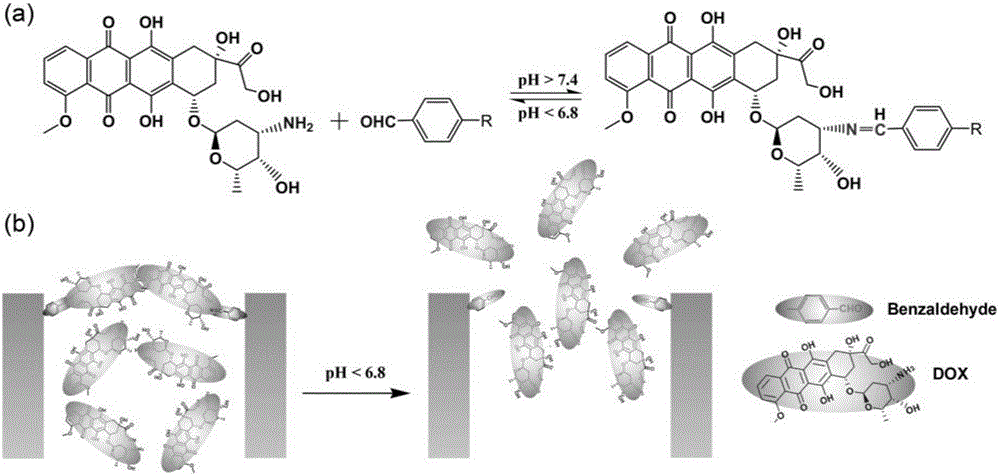

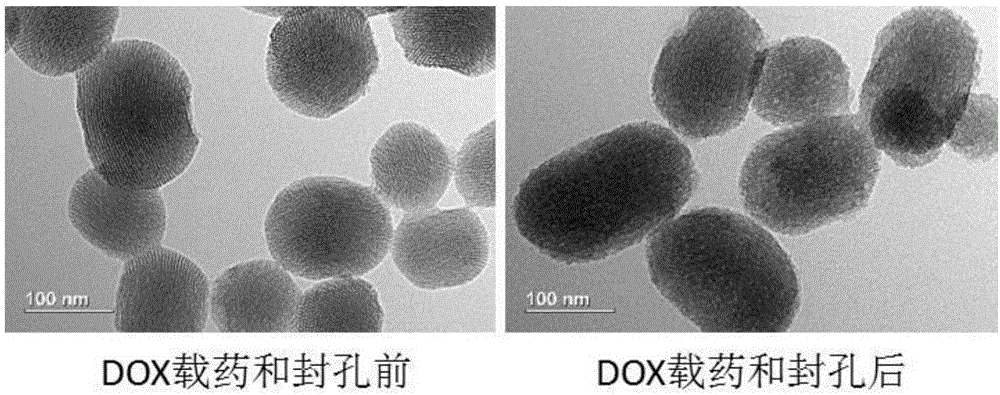

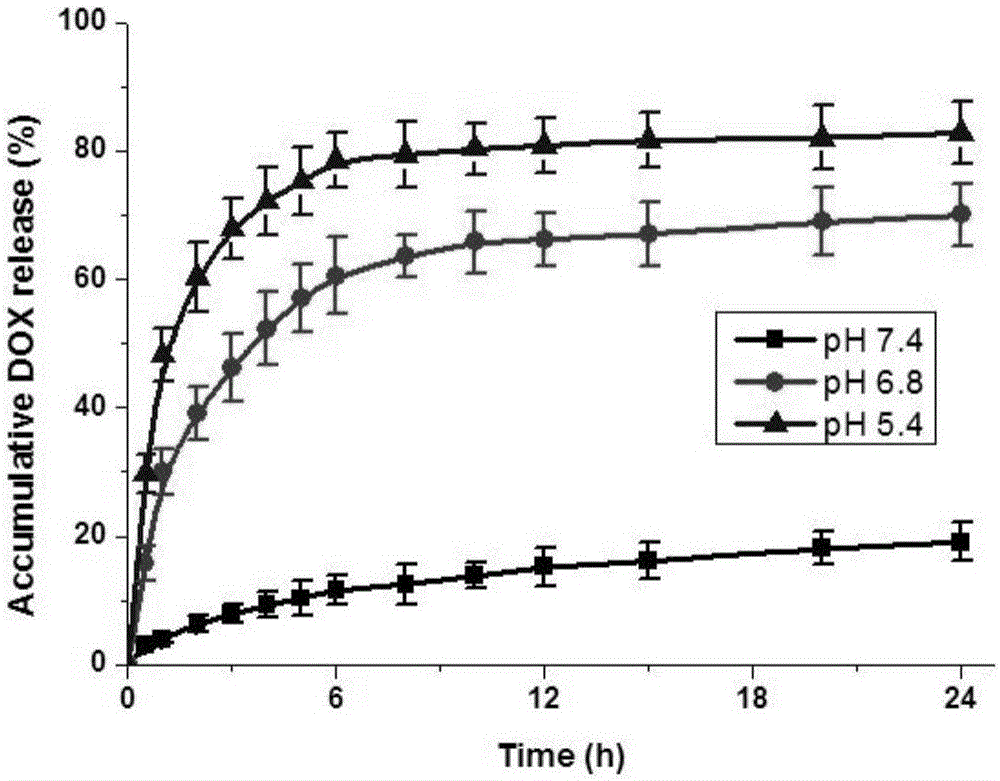

Preparation method of pH-sensitive drug-self-gating mesoporous nano antitumor carrier

ActiveCN106267230AAchieve controlled releaseSmall toxicityOrganic active ingredientsPharmaceutical non-active ingredientsSide effectSilanes

The invention belongs to the technical field of medicine, and particularly relates to a preparation method of a pH-sensitive drug-self-gating mesoporous nano antitumor carrier. The preparation method includes: reacting orderedmesoporous silicon dioxide with amino-containing trimethoxy silane to obtain mesoporous silicon dioxide with the surface aminated; subjecting para-carboxyl benzaldehyde and aminated mesoporous silicon dioxide to amidation to obtain mesoporous silicon dioxide with the surface amidated; loading doxorubicin which is a wide-spectrum antitumor drug amidated mesoporous silicon dioxide in a weak acidic condition, restoring to a neutral condition to obtain the pH-sensitive DOX-self-gating mesoporous nano carrier loaded with the antitumor drug DOX, and complex assistant chemical molecules do not need to be used as gating materials, so that reducing of toxic and side effect of foreign components in the actual tumor treatment process is facilitated, and the carrier has high efficacy and drug release performance sensitive to tumor acidic microenvironment.

Owner:SUZHOU UNIV

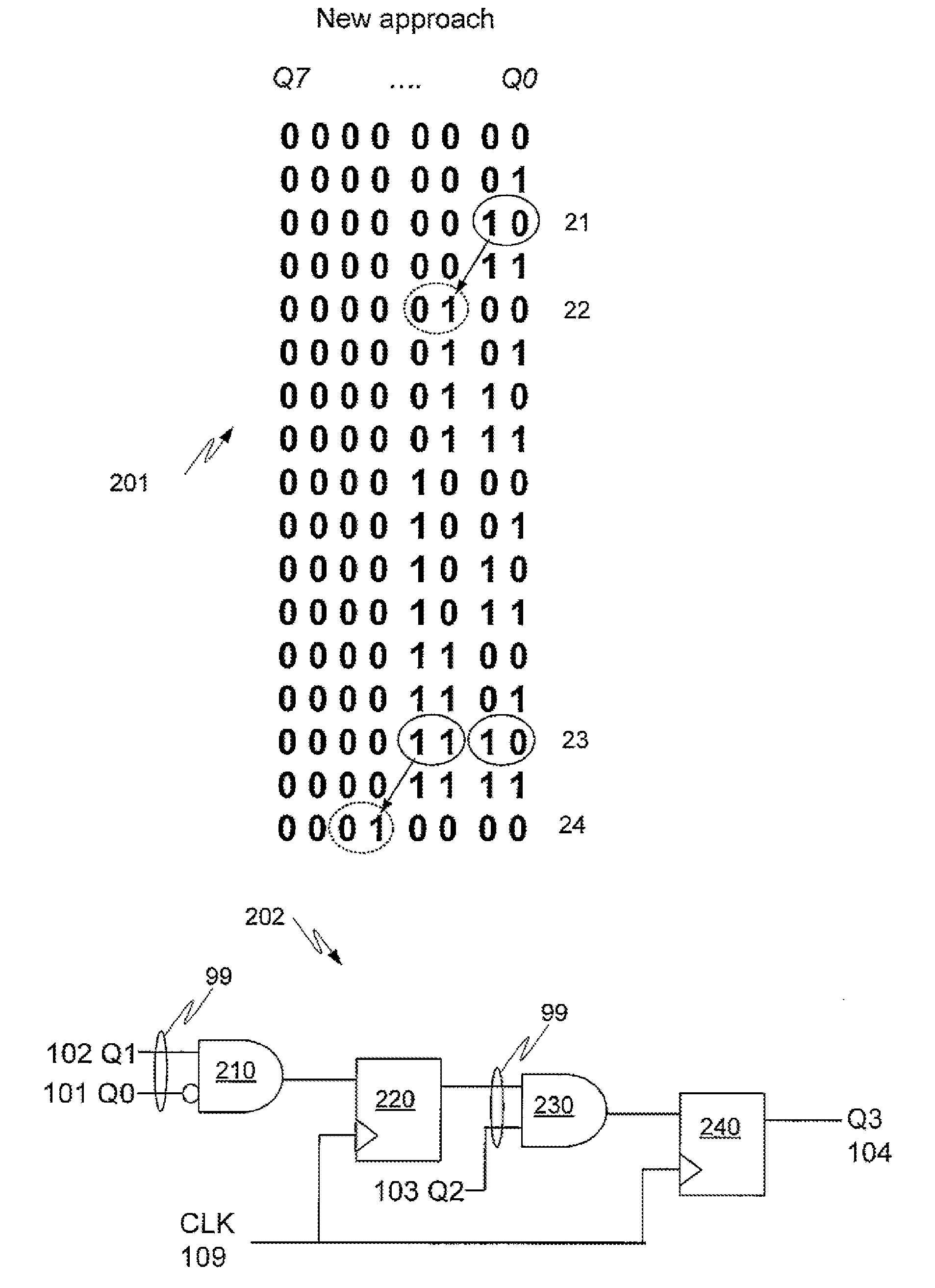

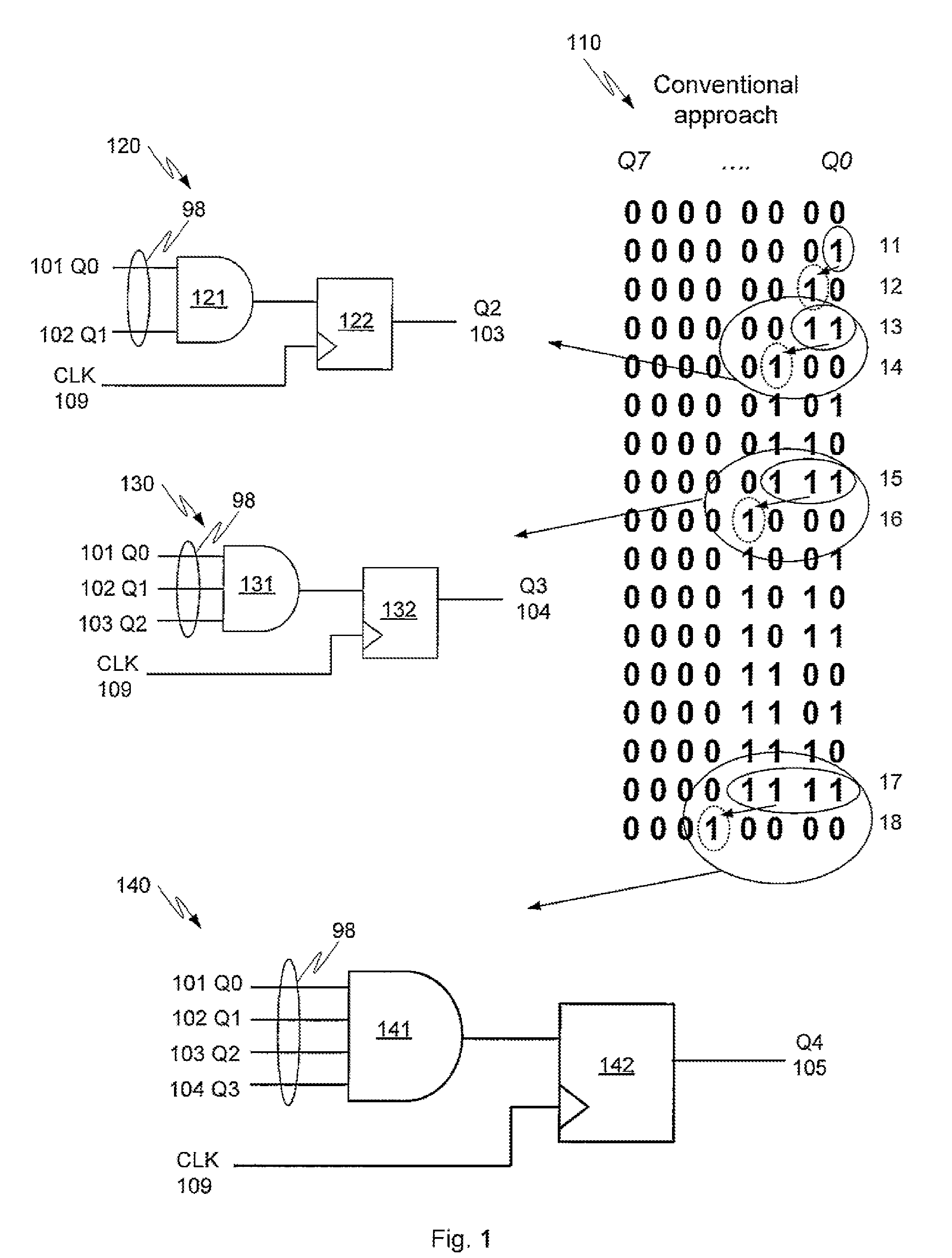

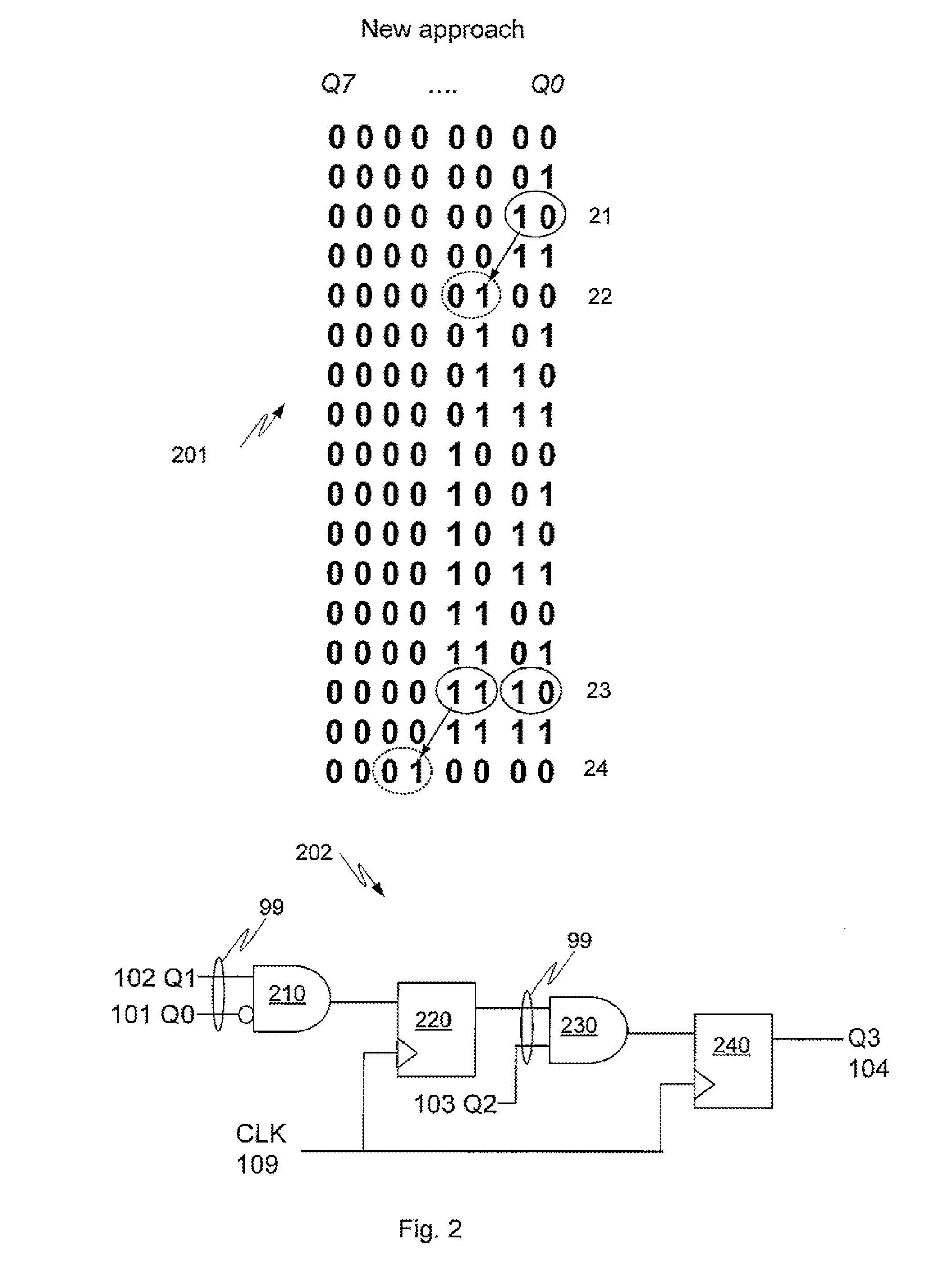

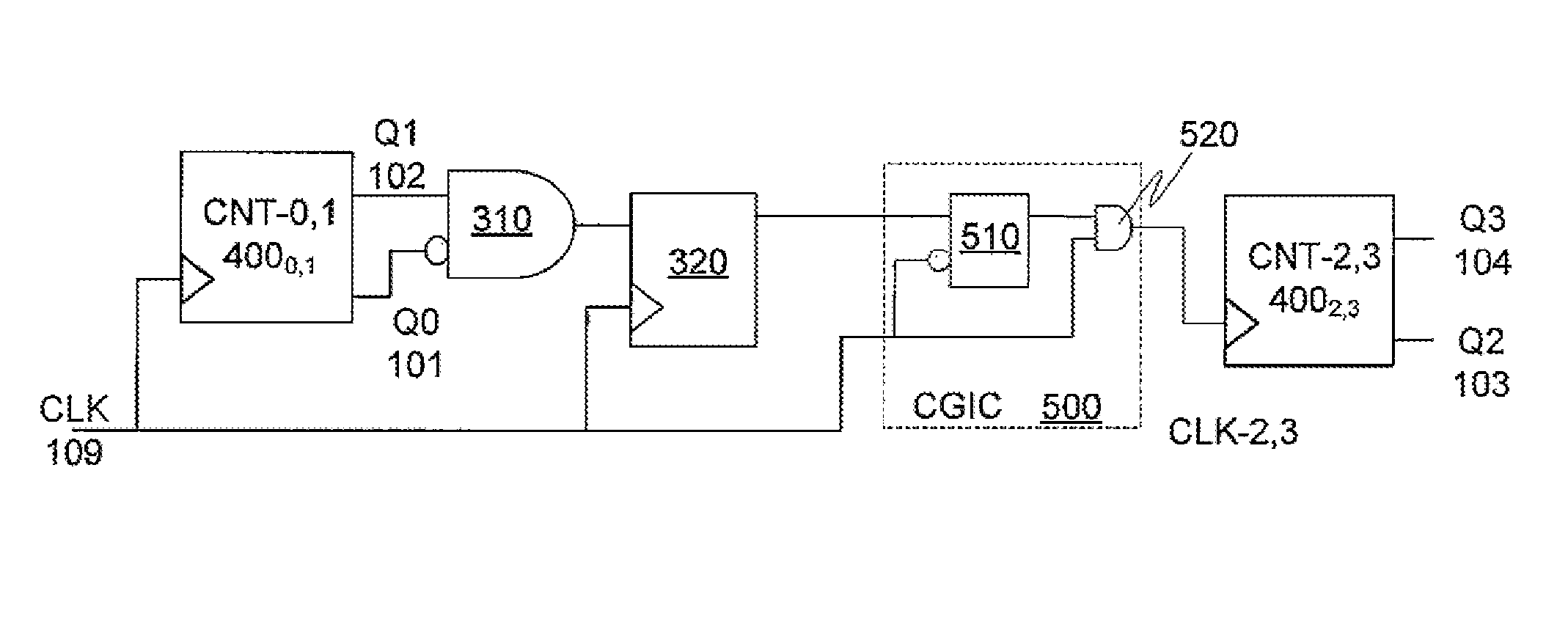

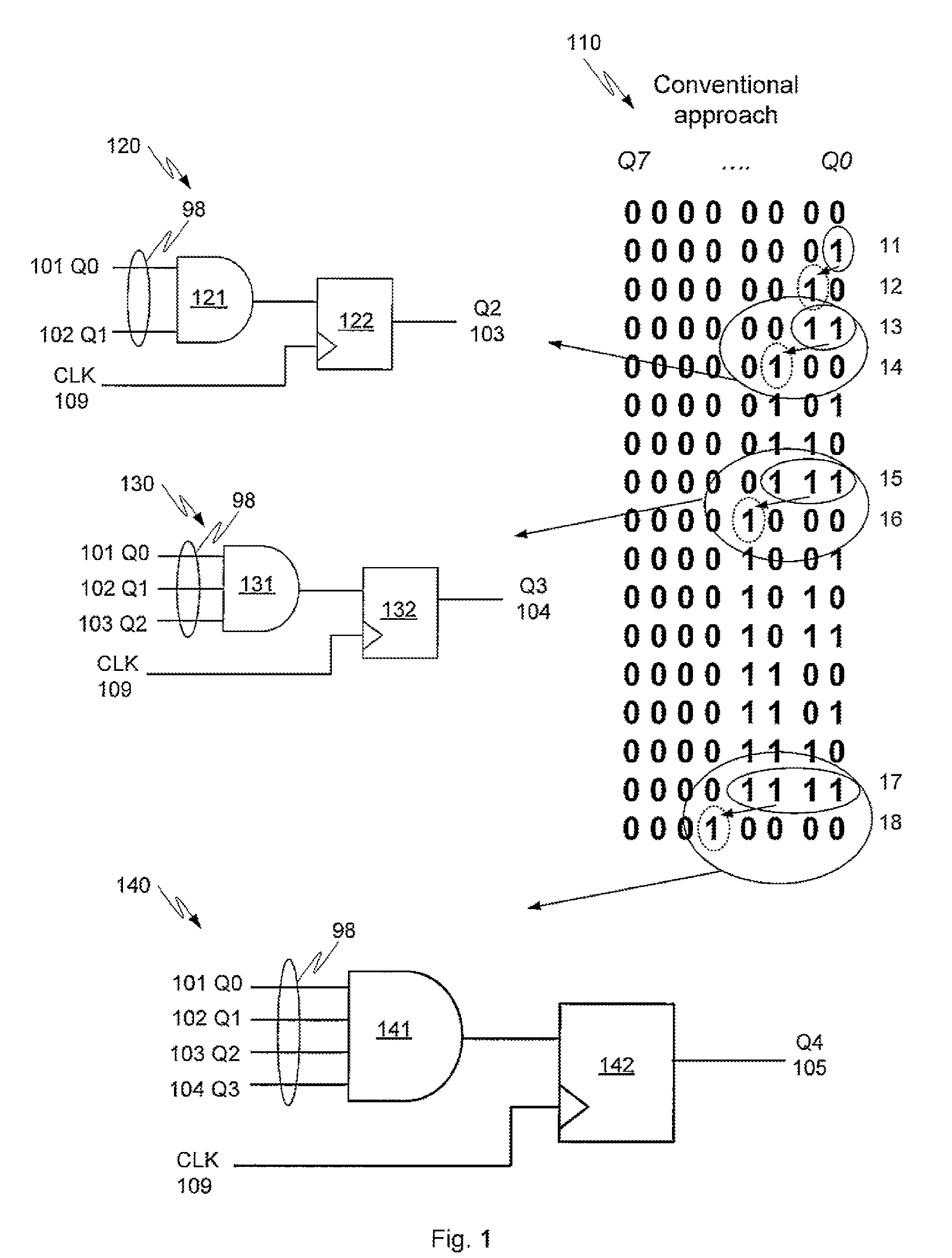

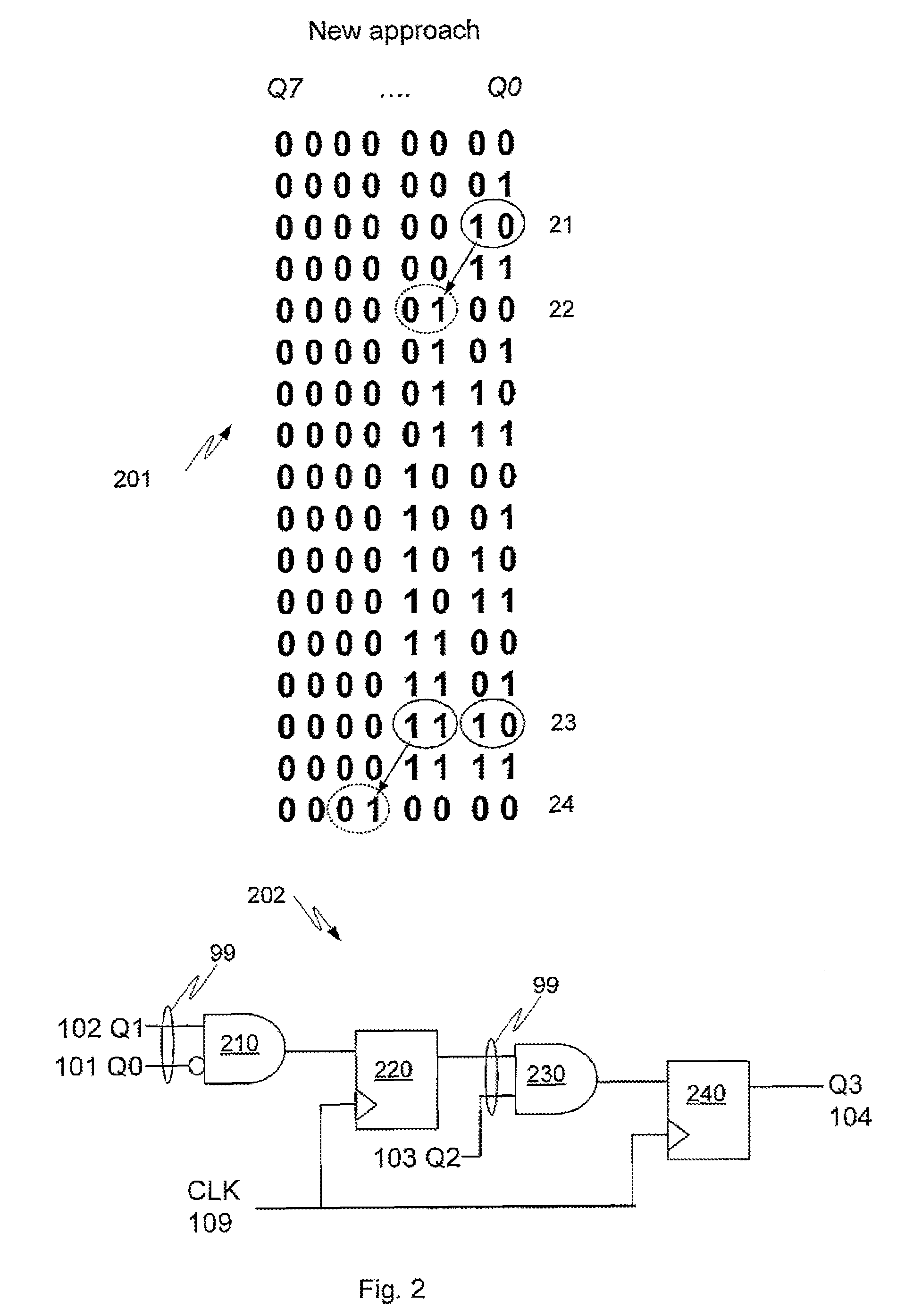

Digital self-gated binary counter

ActiveUS20150010124A1Counting chain synchronous pulse countersCounting chain asynchronous pulse countersLogical combinationComputer module

An n-bit counter is formed from cascading counter sub-modules. The counter includes combinatorial control logic coupled to a lower order counter sub-module. The control logic is arranged to clock gate at least one higher order counter sub-module dependent on a logical combination of outputs of the lower order counter sub-module and where the control logic uses pipelining to store at least one previous control logic output for use in determining a later control logic output.

Owner:NXP USA INC

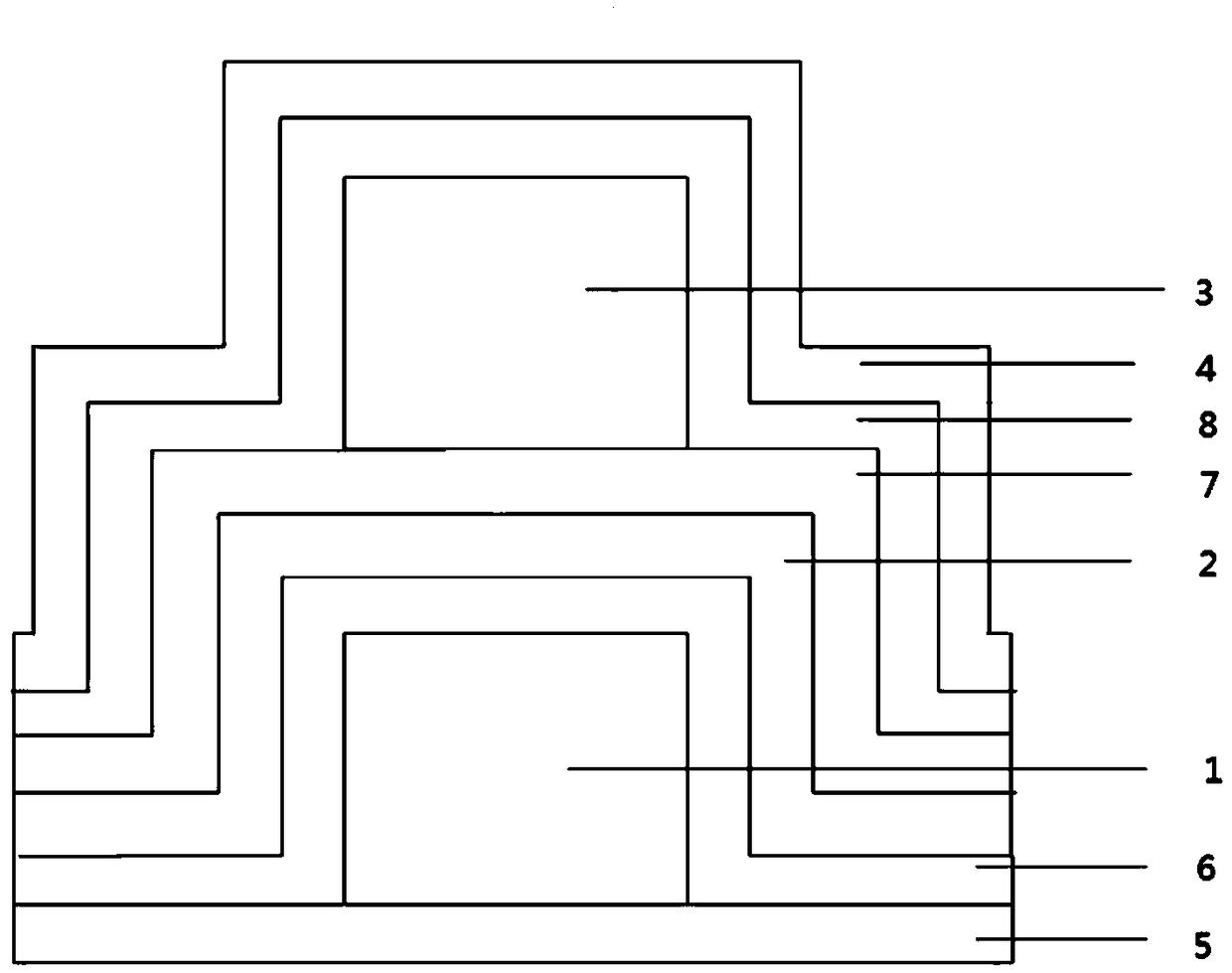

Resistive layer self-gating resistive random access memory as well as building method and application thereof

ActiveCN108735898AImprove compatibilityAvoid introducingElectrical apparatusMicro nanoStatic random-access memory

The invention relates to a resistive layer self-gating resistive random access memory as well as a building method and application thereof. The resistive random access memory comprises an overlappinglayer, wherein the overlapping layer comprises a fourth Hf layer, a fourth Si<3>N<4> layer, a third Hf layer, a third Si<3>N<4> layer, a second Hf layer, a second Si<3>N<4> layer, a first Hf layer anda first Si<3>N<4> layer which are arranged in sequence from outside to inside. During 1R array gating based on a homogeneous HfO<x> base, a resistive layer is taken as a gating layer, so that an extra third gating device is prevented from being introduced. An asymmetrical structure is machined based on micro-nano for filling (or hollowing), a depletion region is formed on the periphery of a filling region under the micro-nano scale, and the depletion region dynamically changes along with an external electric field. A self-gating effect is achieved according to the universal physical principle. Thus, the resistive random access memory is not limited to the HfO<x> material, but also suitable for all materials capable of forming the depletion region.

Owner:金雪尚呈(杭州)科技有限公司

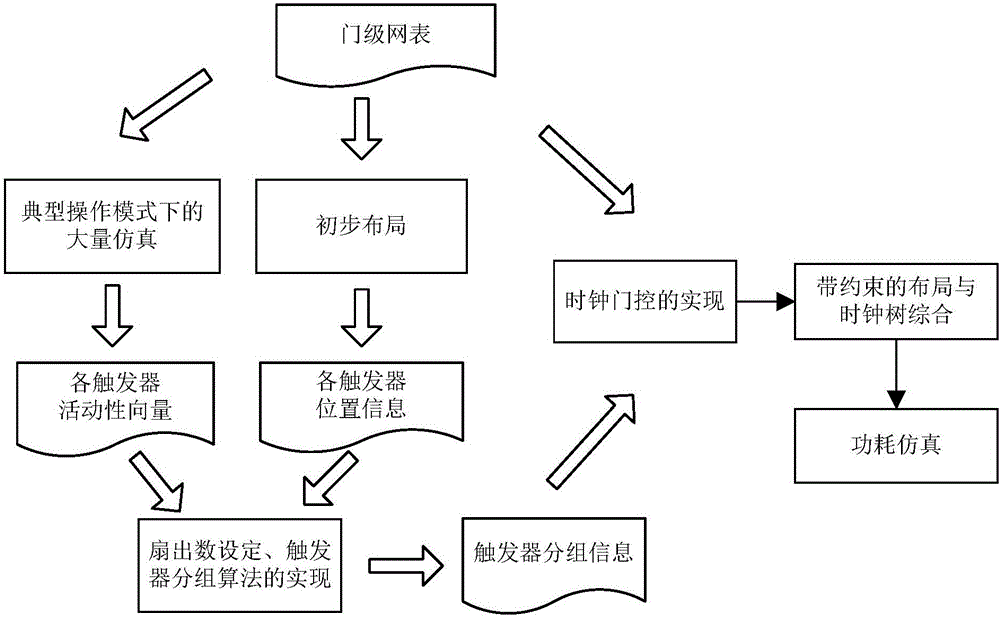

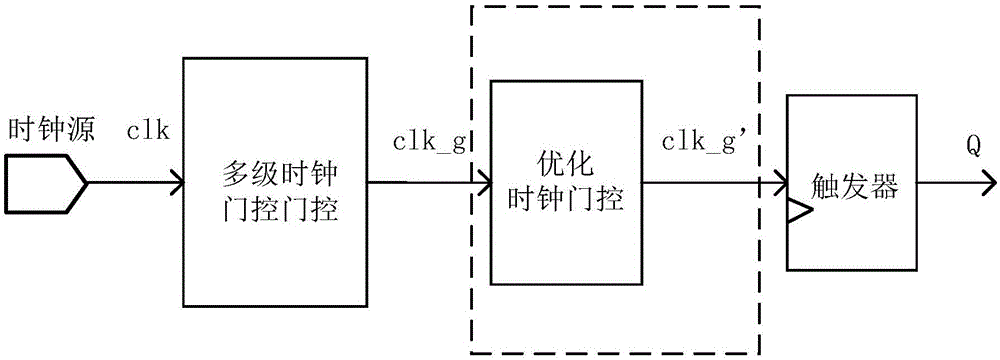

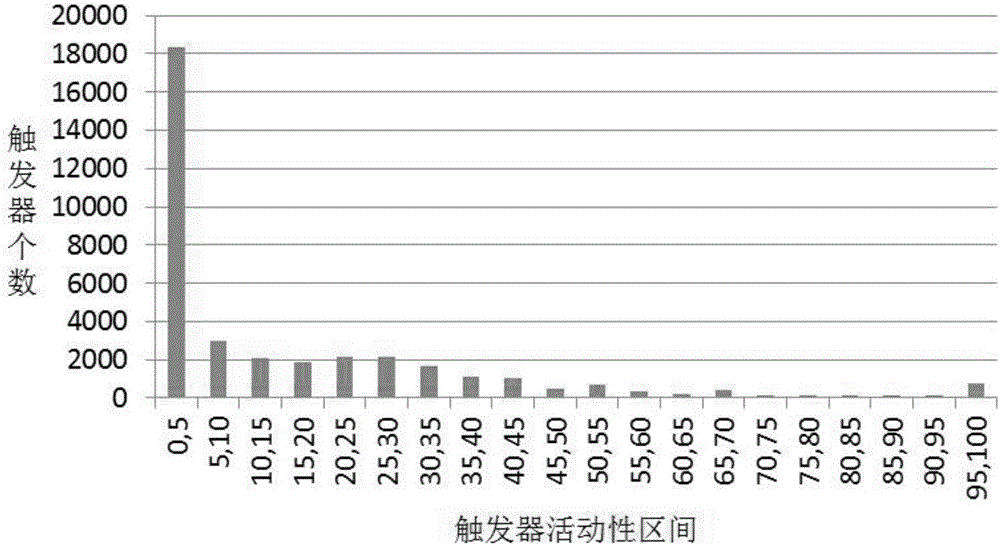

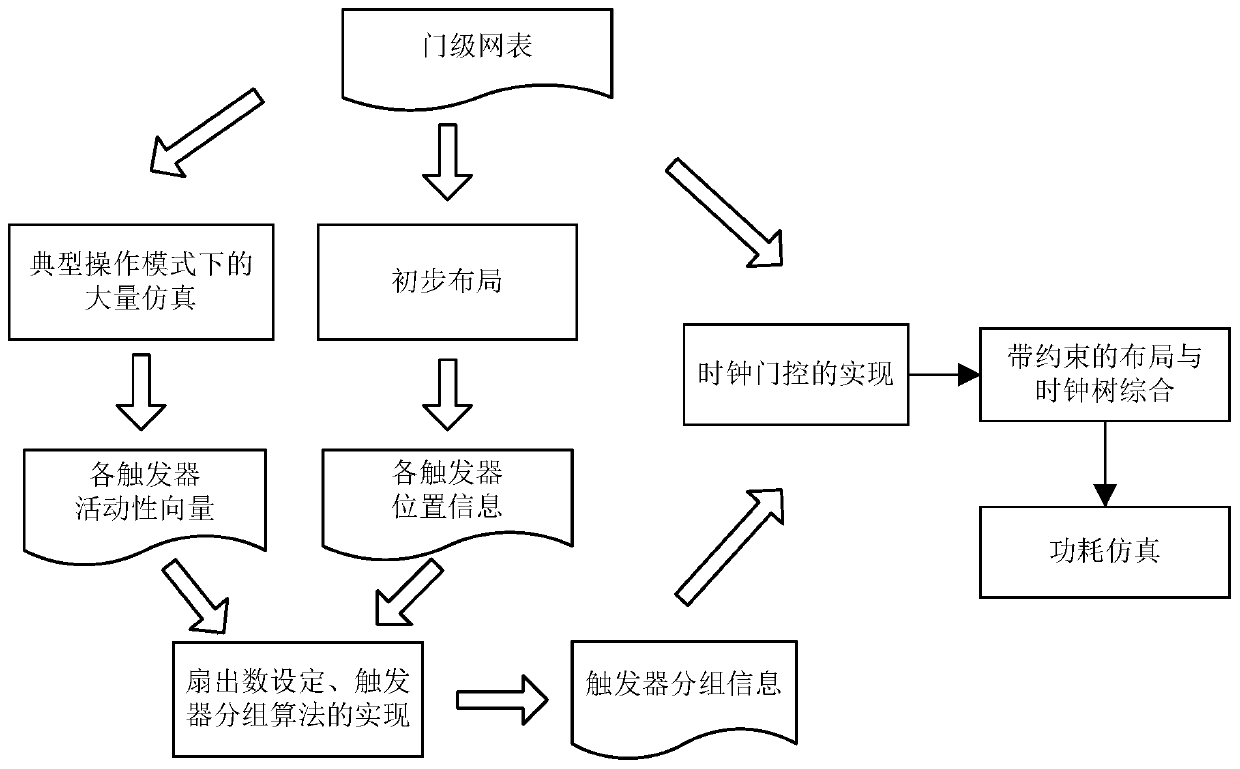

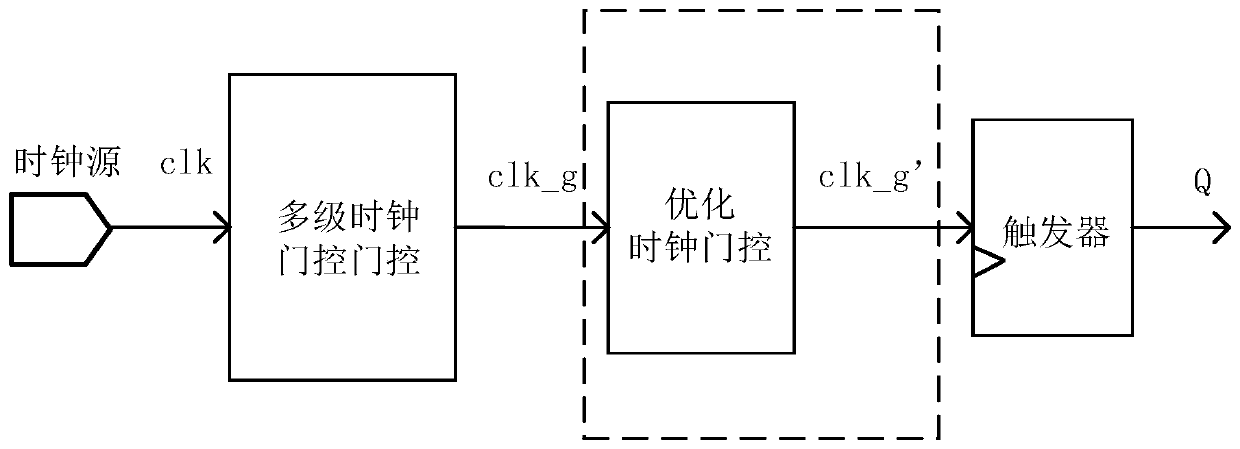

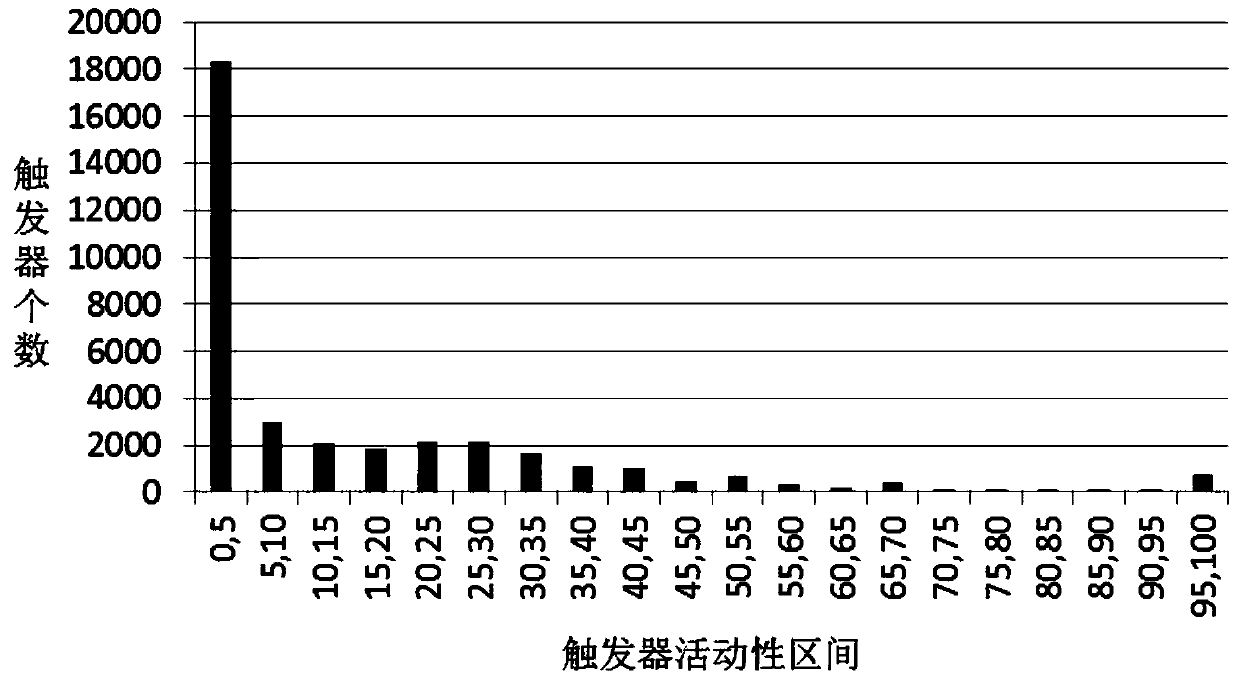

Activity similarity based trigger grouping clock gating method

ActiveCN106527575AIncreased gated periodReduce dynamic power consumptionGenerating/distributing signalsDigital signal processingClock tree

The invention discloses an activity similarity based trigger grouping clock gating method. The method includes the following steps: acquiring an activity vector of each trigger in a typical working mode on the basis of gate level simulation in a typical working mode of a kernel of a digital signal processor, and acquiring the transition rate of the triggers and the correlation among the triggers by counting and processing the activity vectors of the triggers; performing initial layout by using a layout tool, and acquiring initial positions of the triggers in the kernel of the digital signal processor in a layout; and achieving grouping of the triggers by using transition rate information and trigger position data; achieving clock gating through trigger grouping information and the XOR gate self-gating method; and making a new layout for new generated net lists, and achieving clock tree comprehensive and power consumption simulation verification. The method can achieve trigger grouping clock gating of the kernel of the digital signal processor, can effectively prolong the gating period of a clock, and can reduce the dynamic power consumption.

Owner:RES INST OF SOUTHEAST UNIV IN SUZHOU

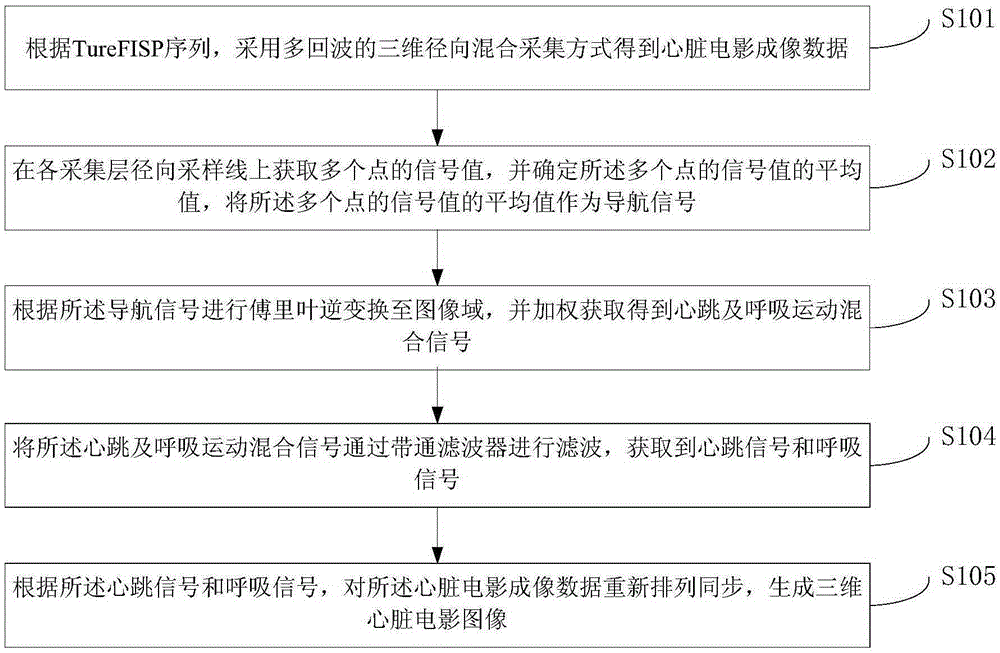

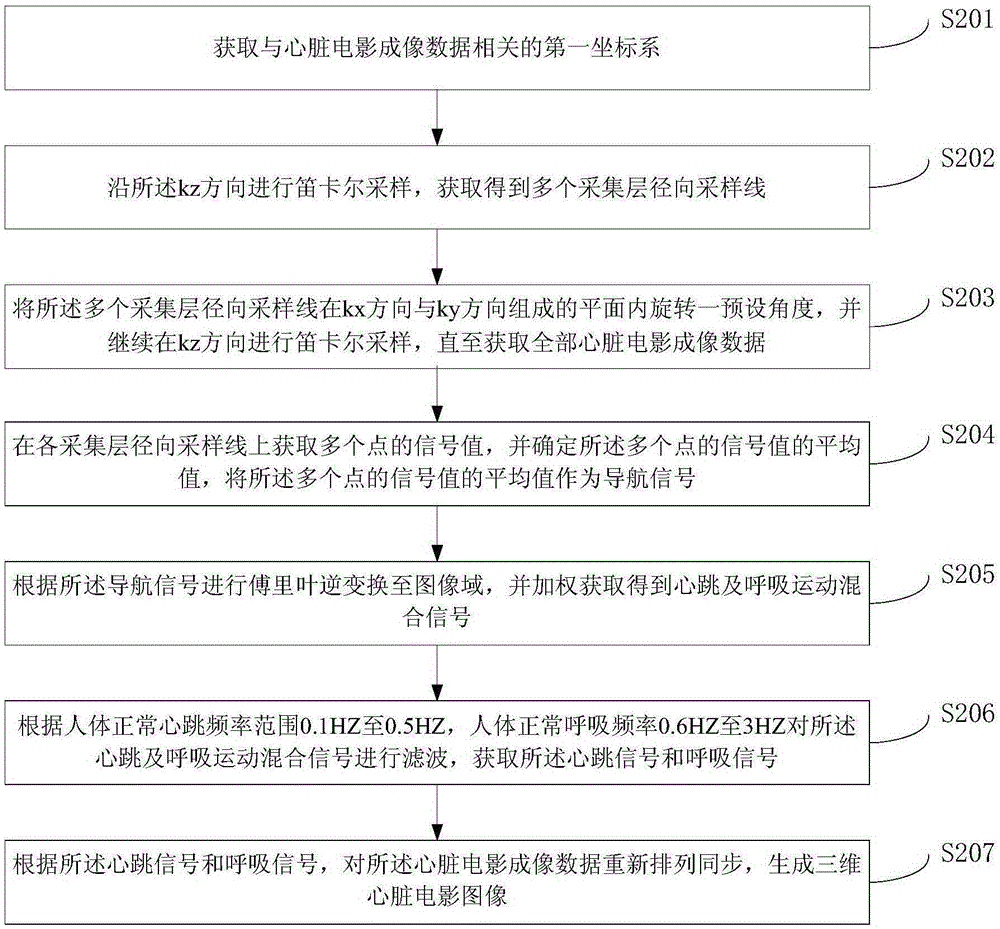

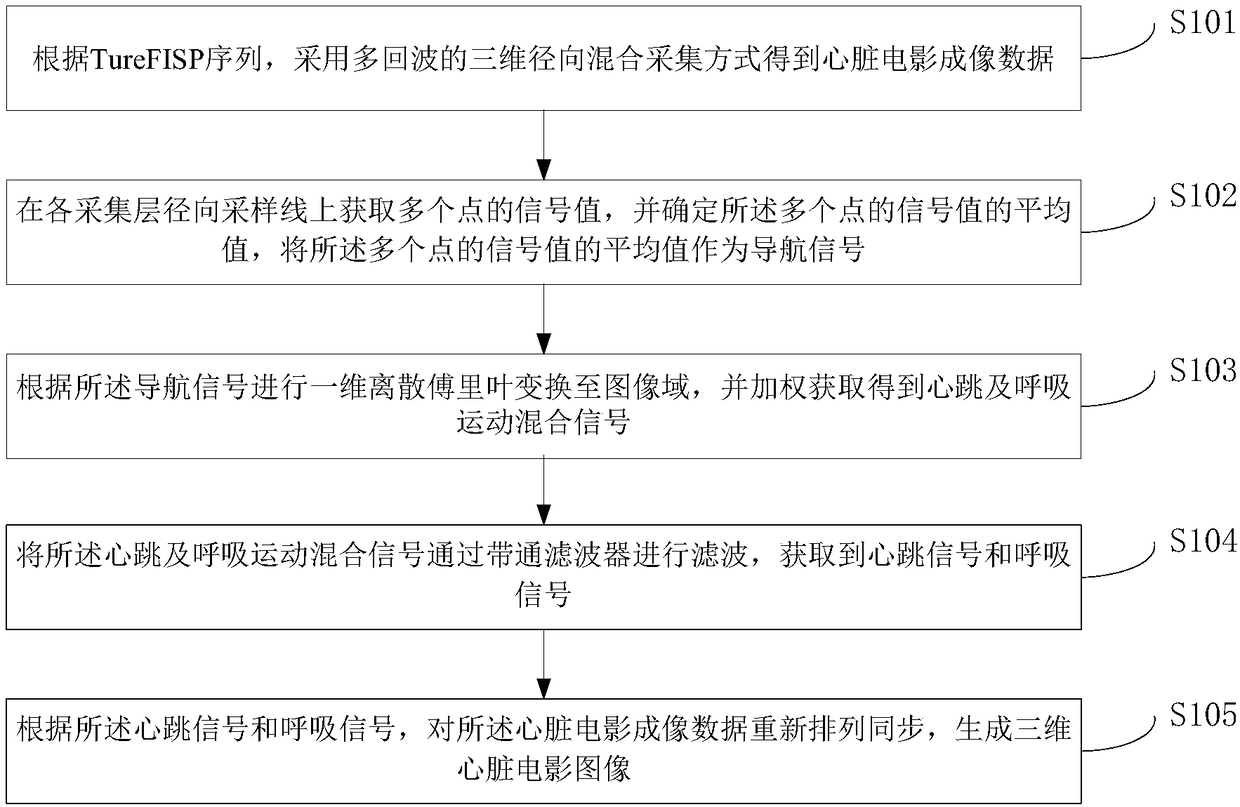

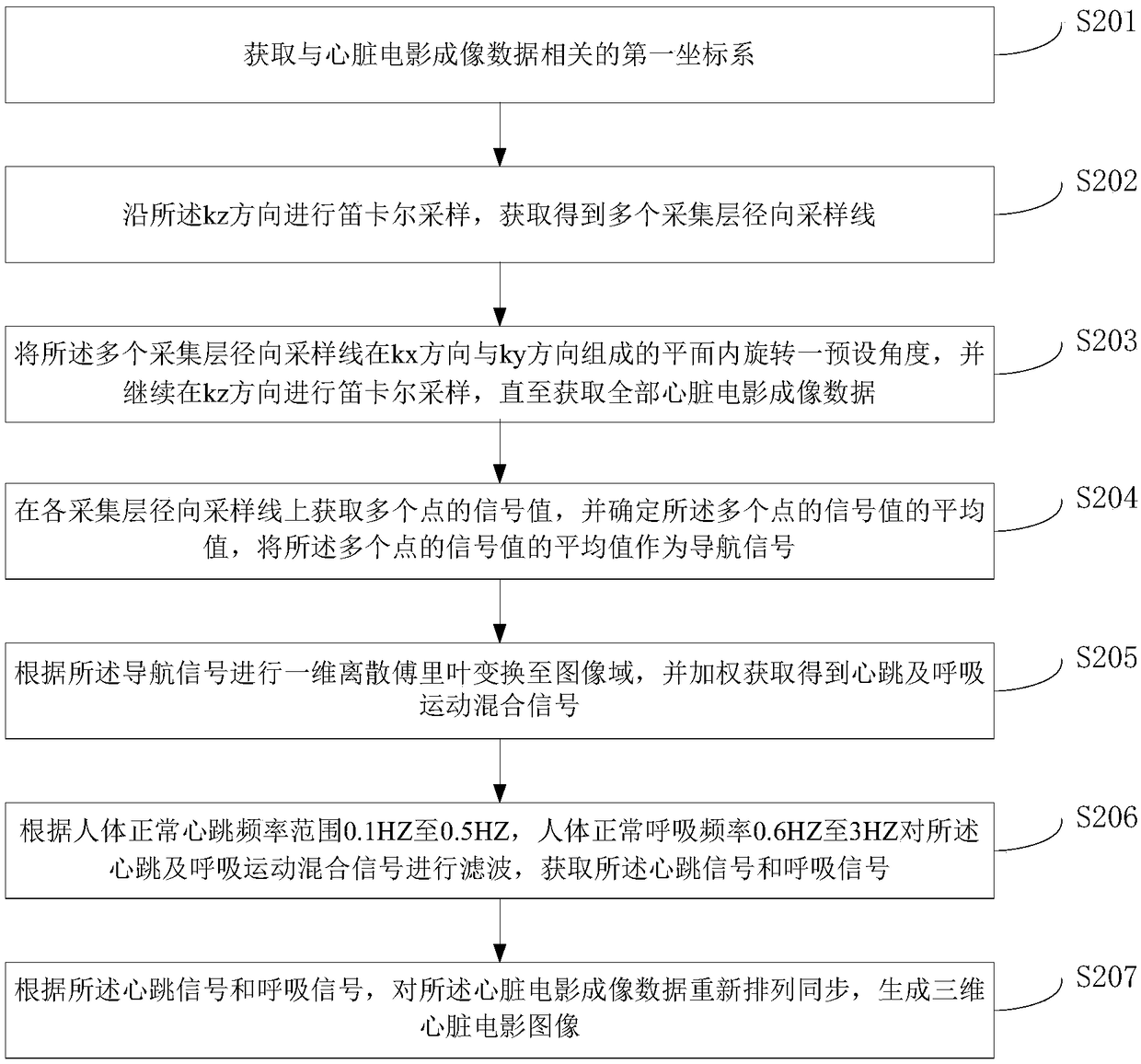

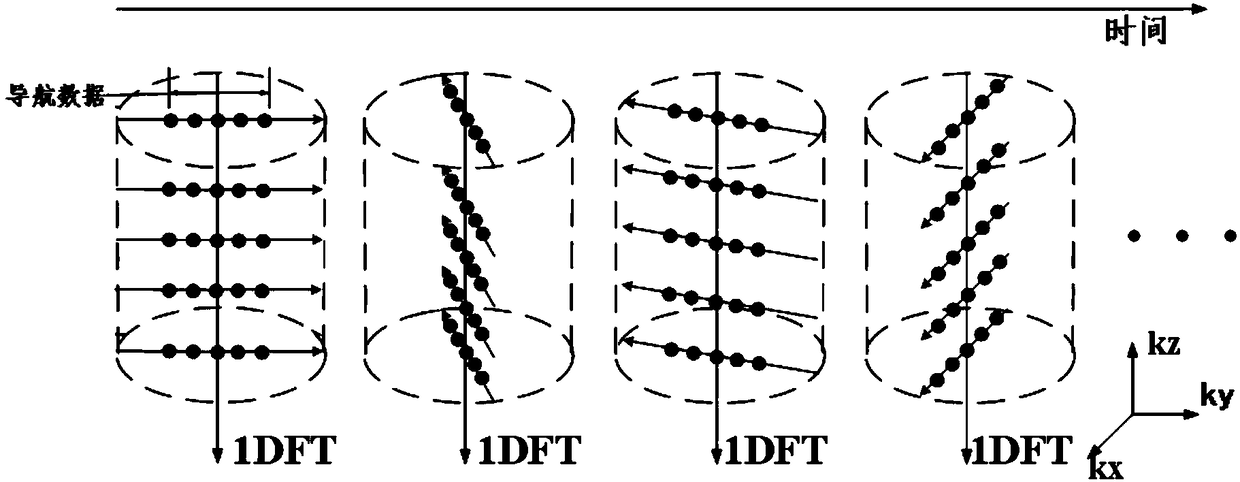

Motion signal extracting method and device for self-gating three-dimensional cardiac imaging

ActiveCN105266813AImprove image qualityMotion signal is accurateDiagnostic recording/measuringSensorsBand-pass filterMultiple point

The invention provides a motion signal extracting method and device for self-gating three-dimensional cardiac imaging, and relates to the technical field of three-dimensional cardiac imaging. The method includes the steps that according to the TureFISP sequence, cardiac cine imaging data are obtained by adopting a multi-echo three-dimensional radial mixed collecting mode; signal values of multiple points are obtained from radial sampling lines of all collecting layers in the cardiac cine imaging data, and average values of the signal values of the multiple points are determined to serve as navigation signals; the navigation signals are subjected to inverse Fourier transformation to be transformed into an image domain, and heartbeat and breathing motion mixed signals are obtained through weighting; the heartbeat and breathing motion mixed signals are filtered through a band-pass filter to obtain heartbeat signals and breath signals; according to the heartbeat signals and the breath signals, the cardiac cine imaging data are arrayed and synchronized again to generate three-dimensional cardiac images. The problem that in the prior art, the quality of the rebuilt cardiac cine images is affected as obtained motion signals are inaccurate is solved.

Owner:SHENZHEN INST OF ADVANCED TECH CHINESE ACAD OF SCI

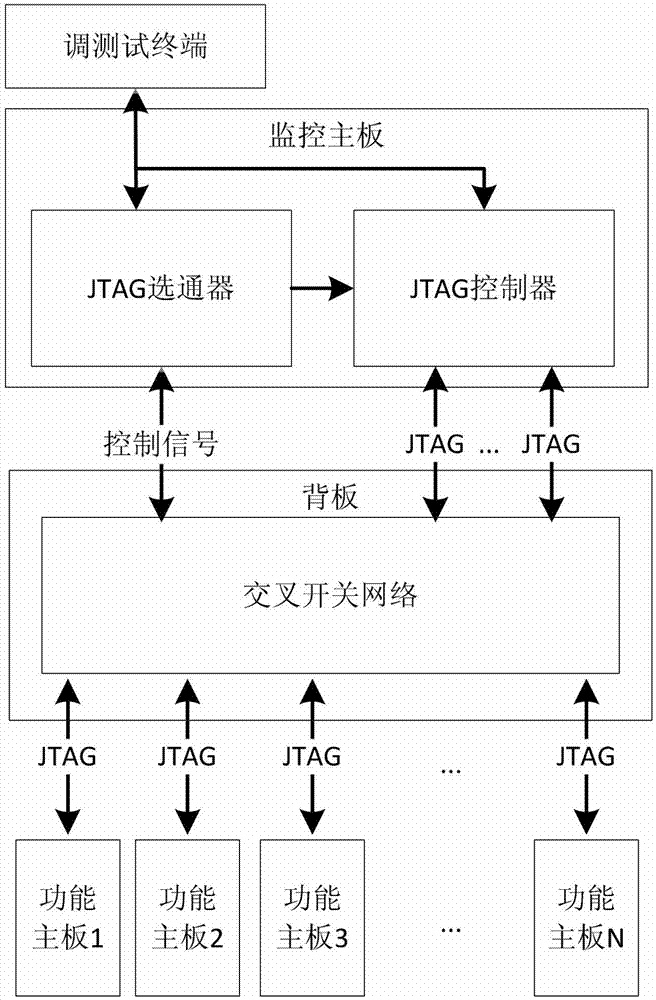

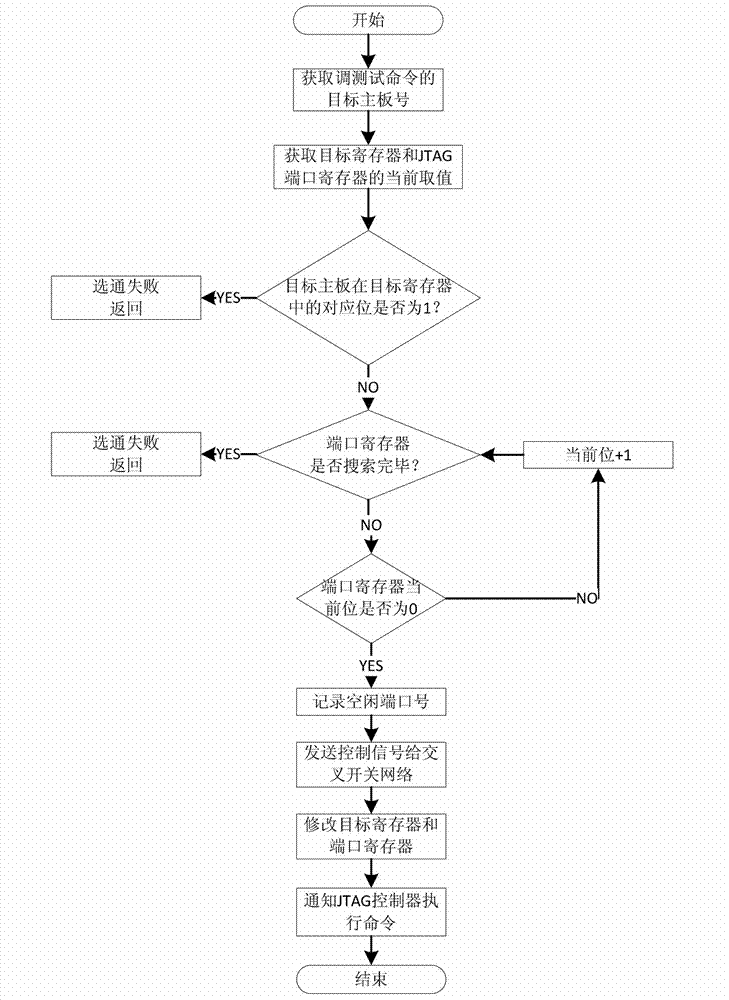

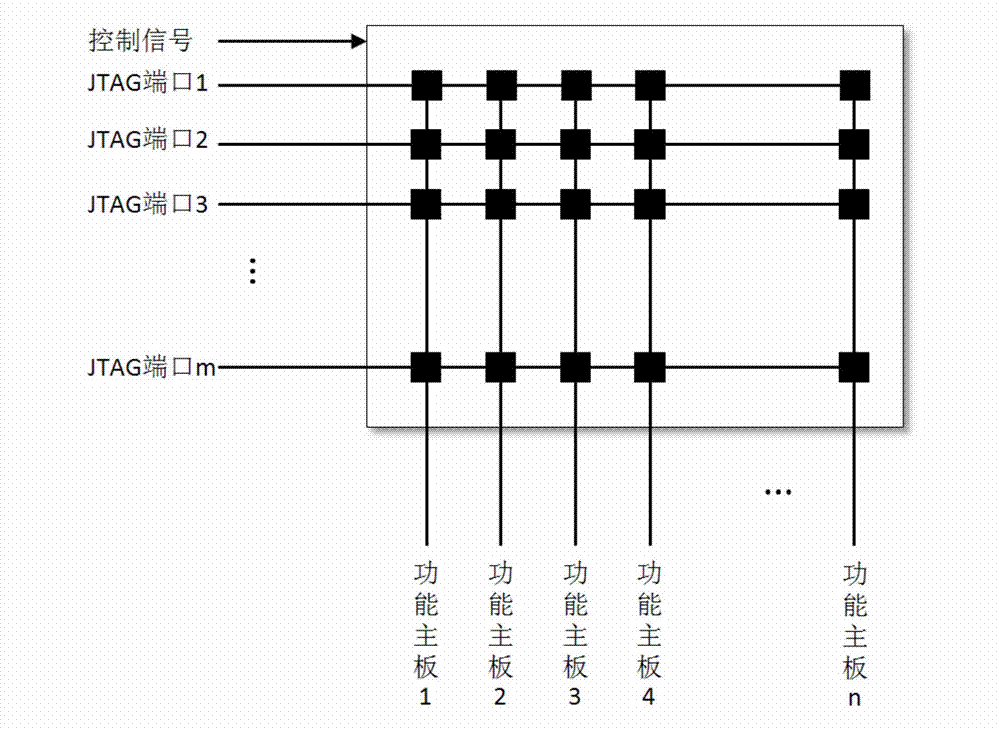

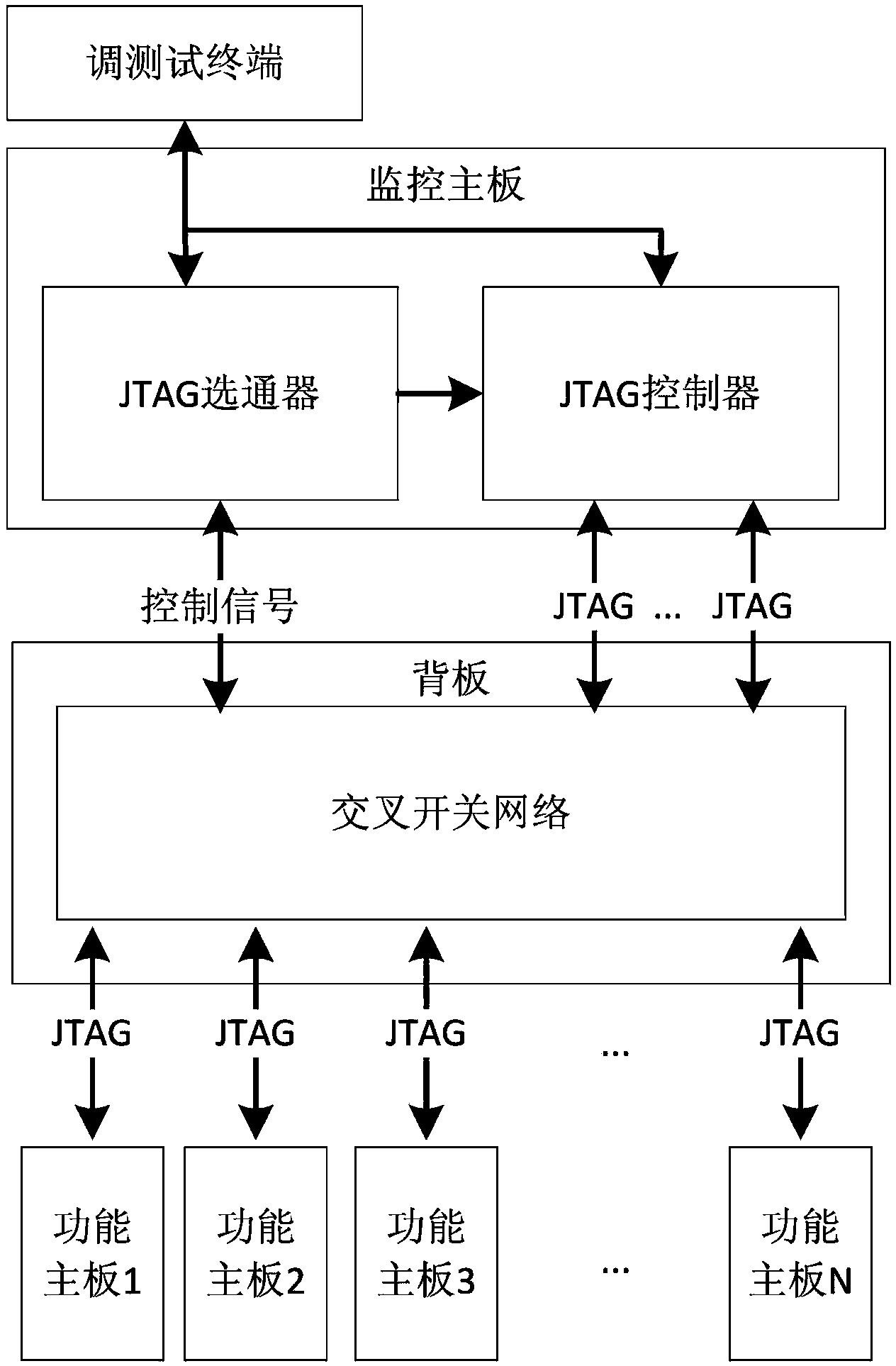

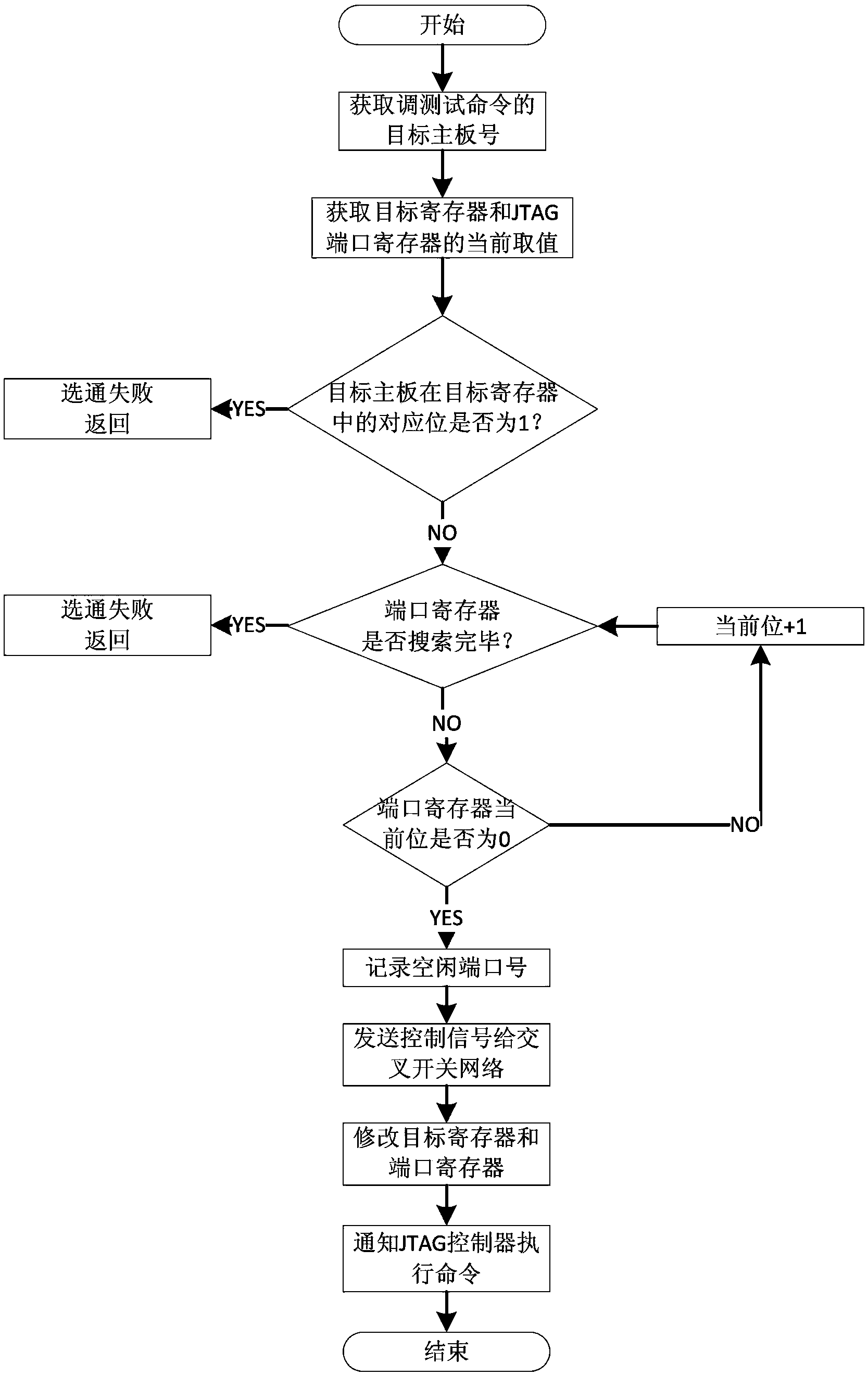

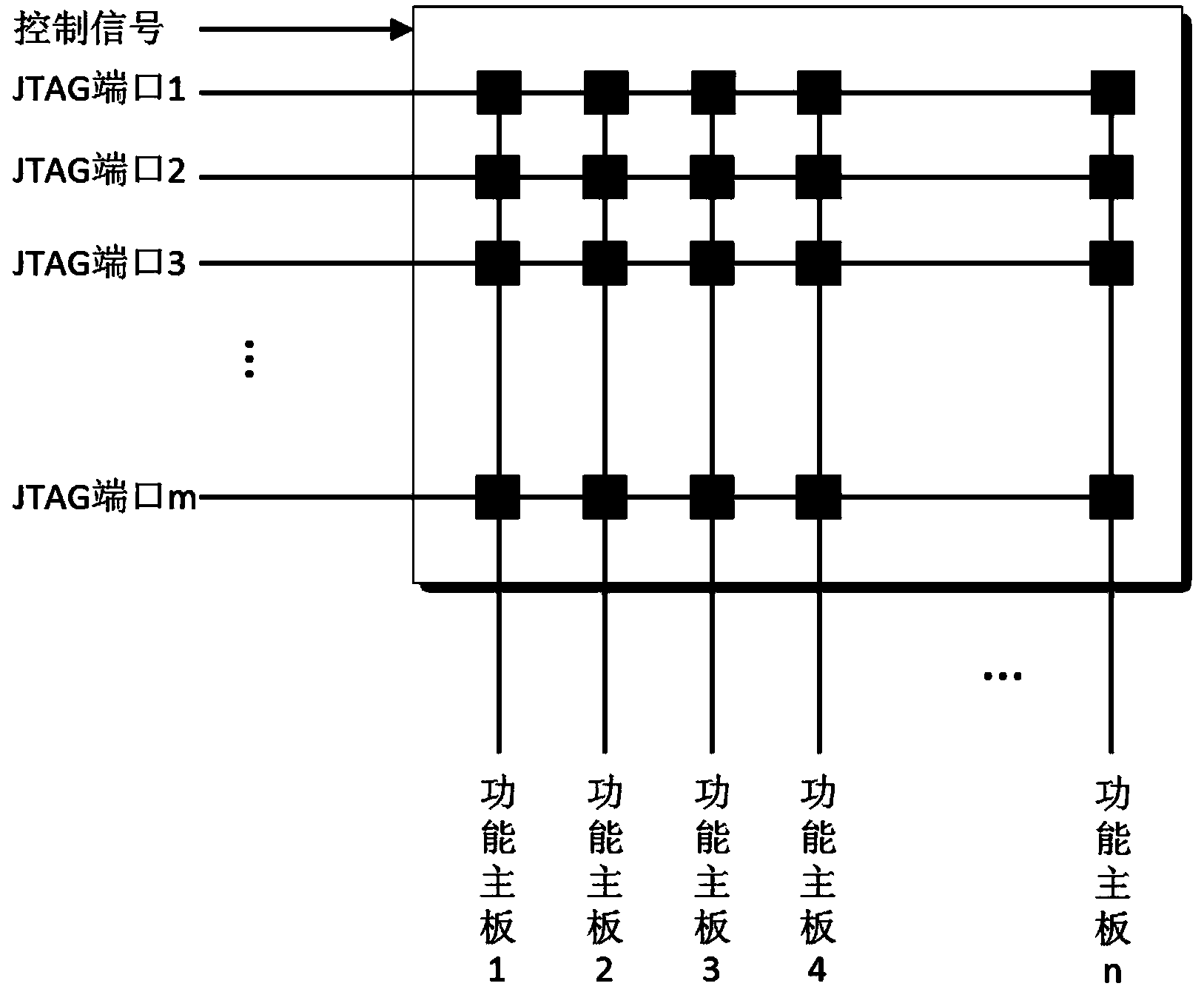

Super computing system oriented self-gating boundary scan test method and device

ActiveCN103163451AIncrease flexibilityReduce the numberElectrical testingCrossbar switchControl signal

The invention discloses a super computing system oriented self-gating boundary scan test method and a super computing system oriented self-gating boundary scan test device. The method comprises the following steps of: calculating to obtain the optimum test joint test action group (JTAG) line according to an input target main board number, a test command and test concurrency to determine a JTAG output port of a monitoring main board and send a control signal; and receiving the control signal of a JTAG gate by using a crossbar network on a rear panel, and changing turn-on and turn-off of each switch in the crossbar switch network according to the control signal to finish gating and executing a test command by using the gated JTAG output port. The device comprises a JTAG controller and the JTAG gate which are positioned on the monitoring main board, and a crossbar switch network module positioned on the rear panel. The method and the device have the advantages of simple structure, few rear panel wire, high test flexibility, high test efficiency and balanced JTAG line load.

Owner:NAT UNIV OF DEFENSE TECH

Method for identifying redundant signal paths for self-gating signals

InactiveUS8332800B2CAD circuit designSoftware simulation/interpretation/emulationComputer scienceLogic circuitry

A method for identifying and removing redundant signal paths includes determining whether a given input to a logic circuit is coupled to both an input of a cone of logic of a data input of a clocked state element and a clock gate circuit that is coupled to disable a clock input to the clocked state element. The method may include removing the given input from the cone of logic such that the given input is no longer coupled to the input of the cone of logic responsive to determining that the given input is coupled to both the input of the cone of logic and the clock gate circuit. The method may include preserving the given input to the clock gate circuit such that the given input continues to be coupled to the clock gate circuit after being removed from the input of the cone of logic.

Owner:APPLE INC

Self-gating synchronizer

InactiveUS8134387B2Avoid contentionHinders its propagationPulse manipulationSynchronising arrangementLogic stateComputer science

A synchronizer circuit for transferring data from a source clock domain to a target clock domain. A first latch in the target clock domain may capture a data value corresponding to current data received from the source clock domain. Under certain conditions, the first latch may enter into a metastable, or undefined logic state. A second latch may remain stable, and store a previous value corresponding to data that has most recently been transferred from the source clock domain to the target clock domain. The respective values output by the two latches may be compared by a detection circuit, and a value derived from the output value of the first latch and corresponding to the current data may be written to an output latch if the current data differs from the stored previous value. The detection circuit may also provide a defined logical value to the output latch even if the first latch is in a metastable state.

Owner:APPLE INC

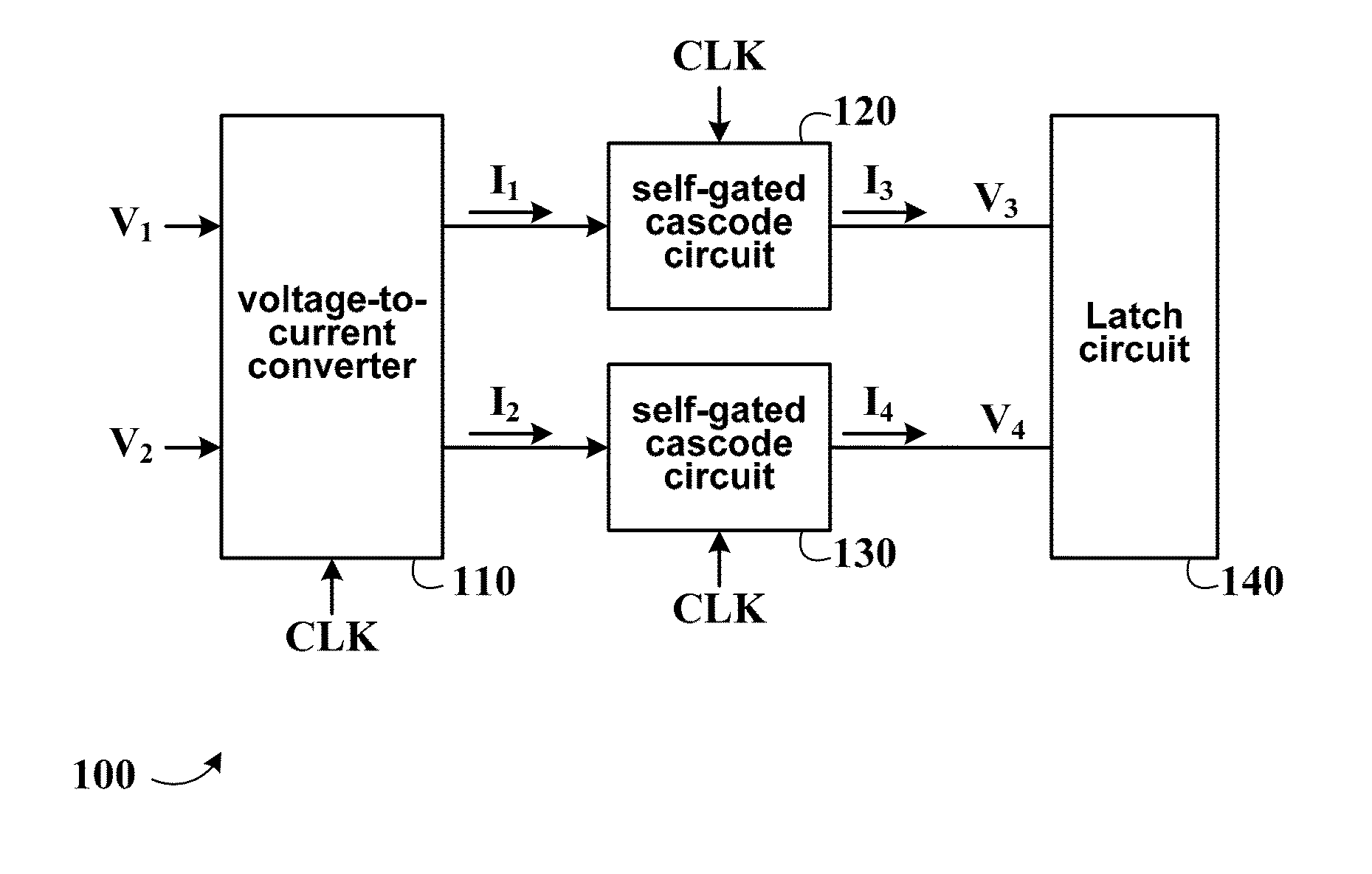

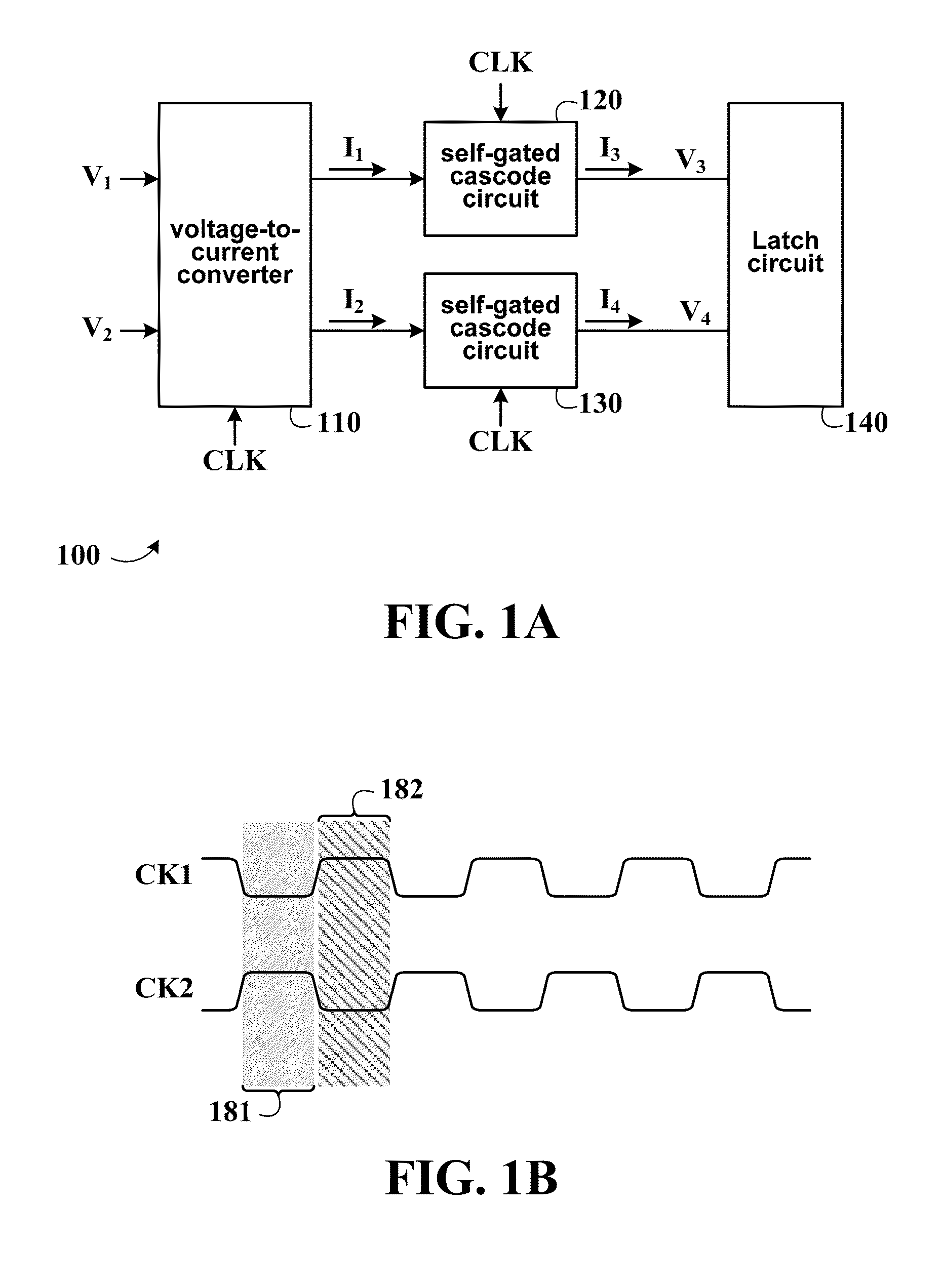

High-speed clocked comparator and method thereof

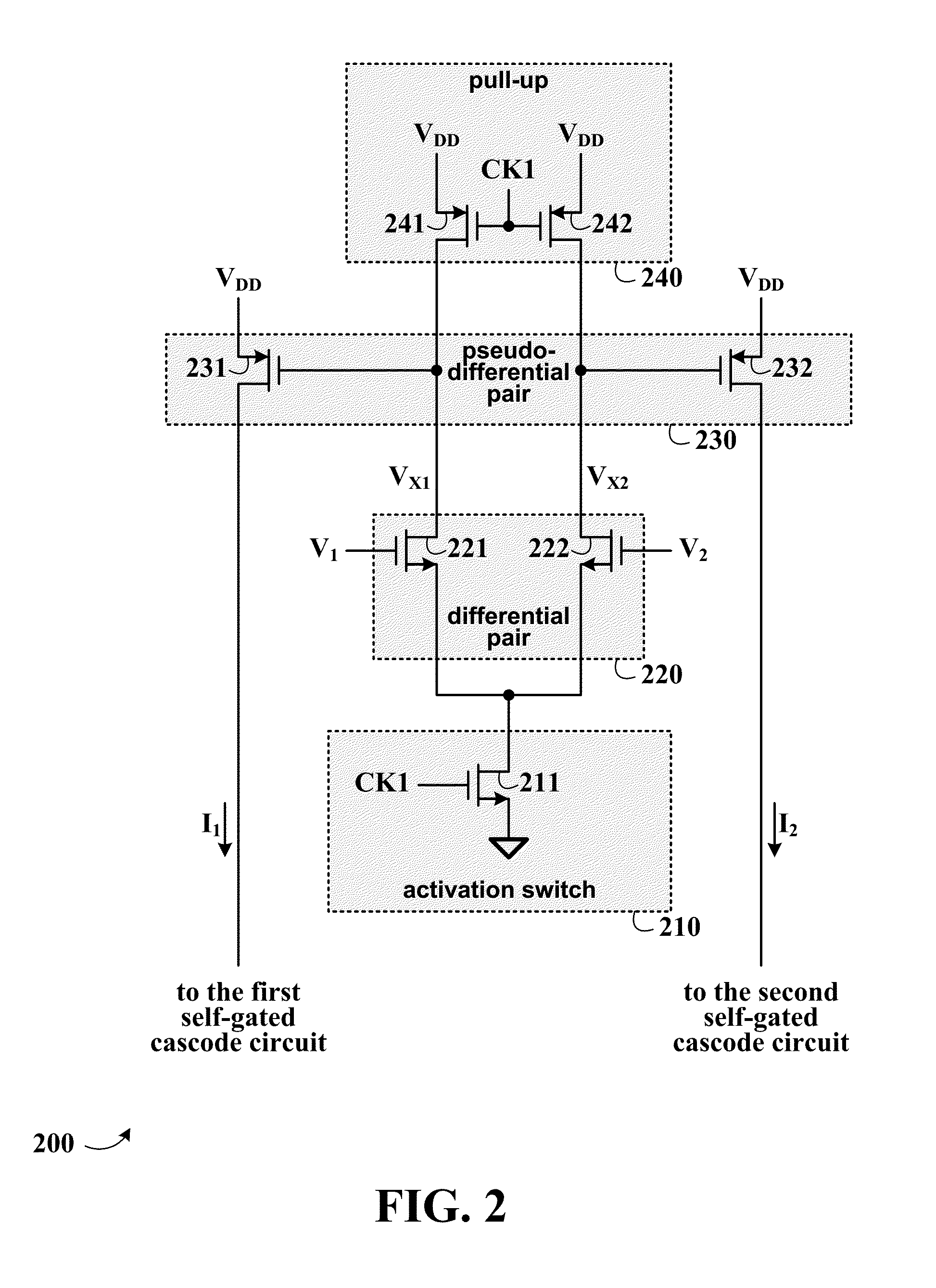

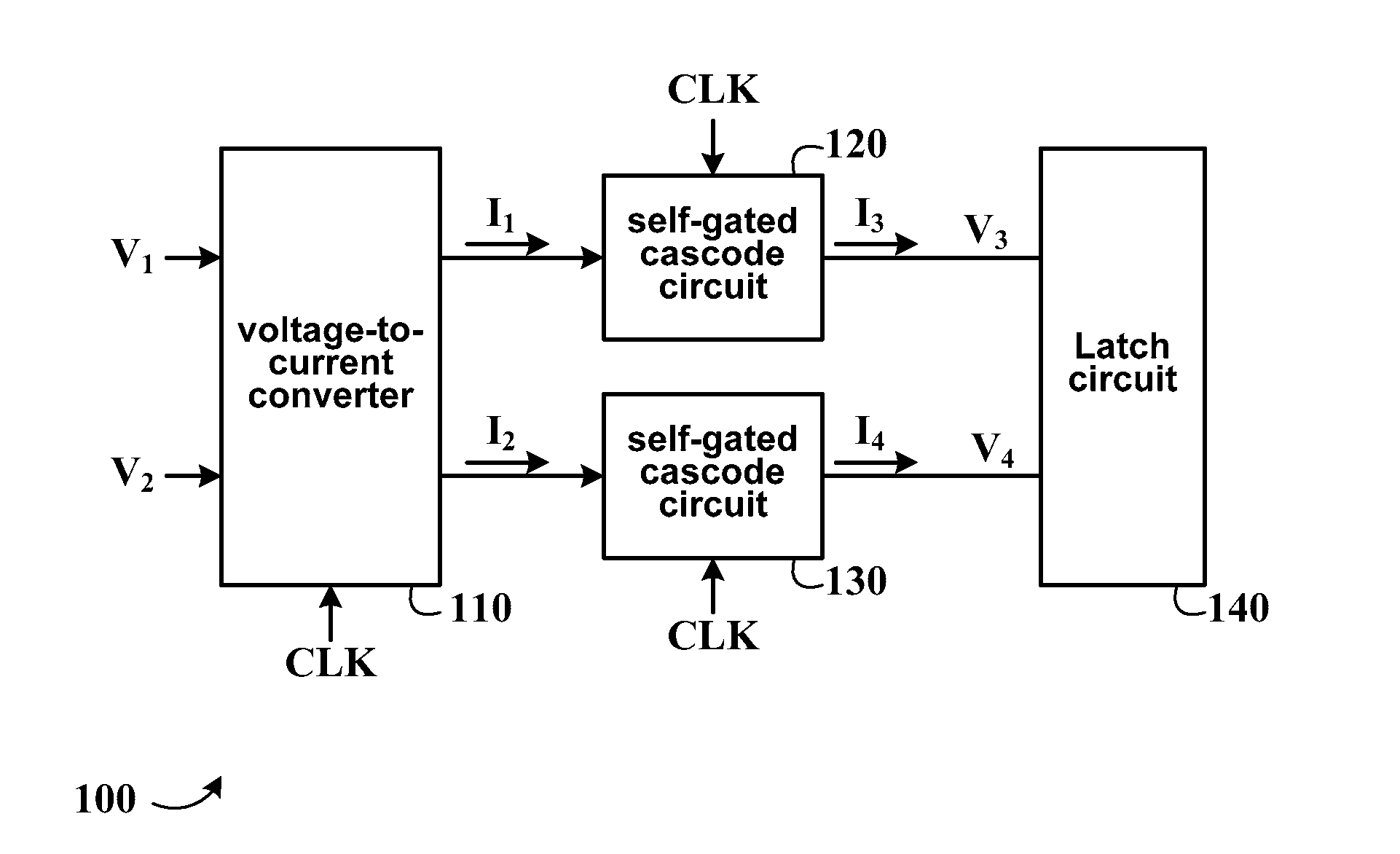

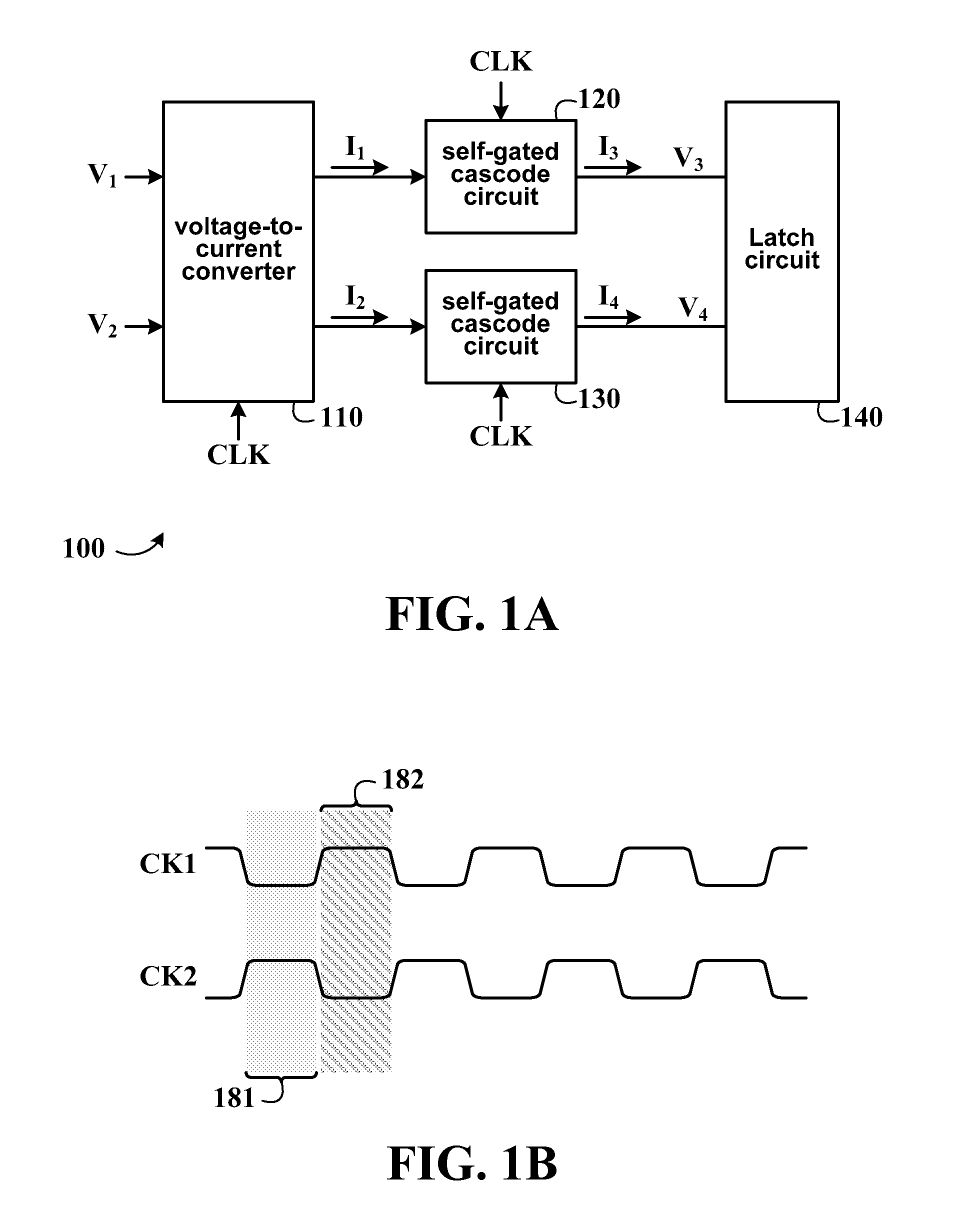

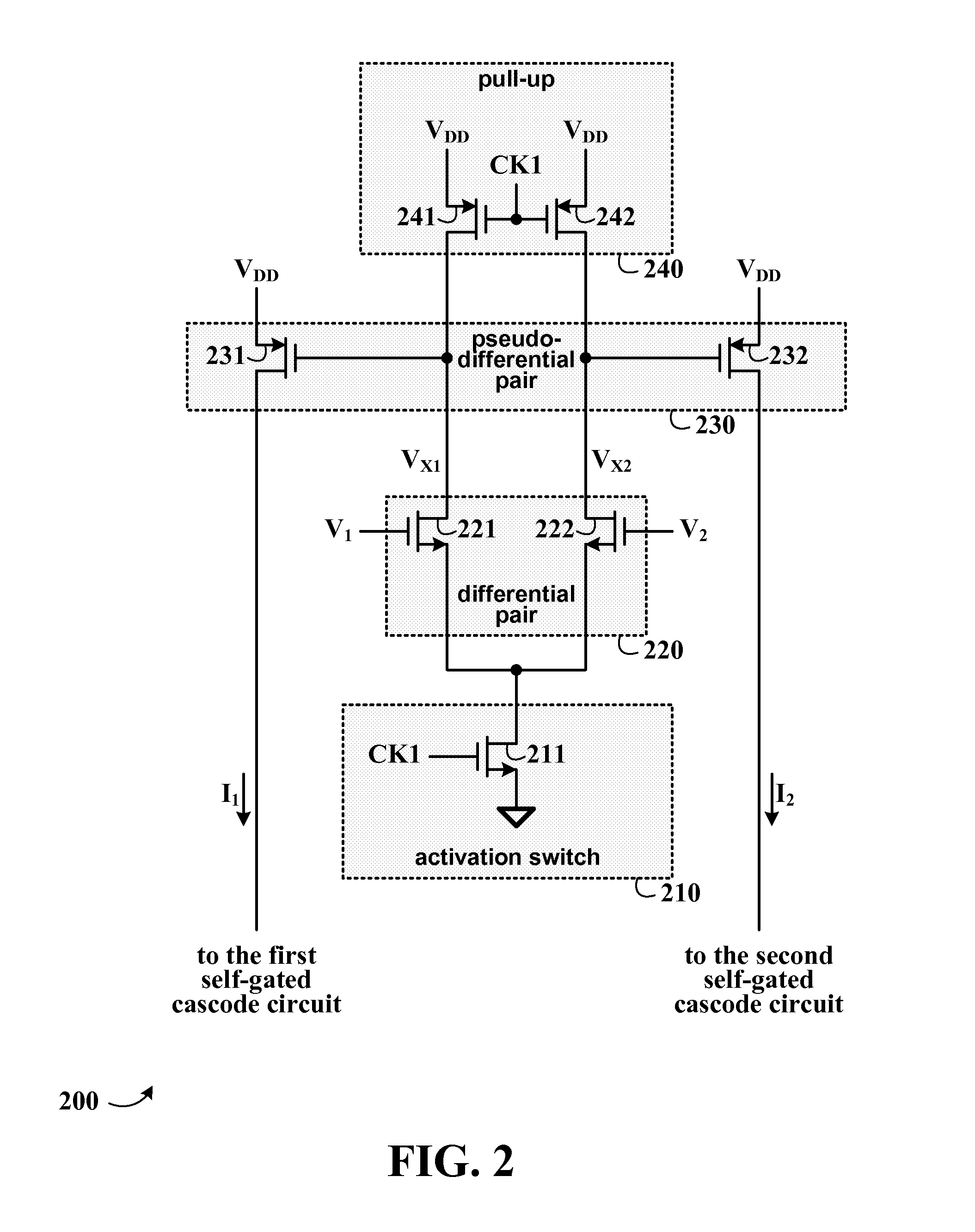

ActiveUS9225320B1Increase speedReduce power consumptionMultiple input and output pulse circuitsPulse descriminationImage resolutionCascode

A circuit includes a voltage-to-current converter receives a first voltage and a second voltage and outputs a first current and a second current in accordance with a clock signal. A first self-gated cascode circuit receives the first current and outputs a third current in accordance with the clock signal. A second self-gated cascode circuit receives the second current and outputs a fourth current in accordance with the clock signal. A latch circuit receives the third current and the fourth current and establishes a third voltage and a fourth voltage representing a resolution of a comparison between the third current and the fourth current, wherein the first self-gated cascode circuit is conditionally shut off based on a level of the third voltage, and the second self-gated cascode circuit is conditionally shut off based on a level of the fourth voltage.

Owner:REALTEK SEMICON CORP

High-speed clocked comparator and method thereof

ActiveUS20160020757A1Increase speedReduce power consumptionElectric analogue storesElectronic switchingImage resolutionCascode

Owner:REALTEK SEMICON CORP

Self-gating resistive storage device and method for fabrication thereof

ActiveUS20190081237A1Improve equipment reliabilityPrevent leakageElectrical apparatusState of artEngineering

Provided are a self-gating resistive storage device and a method for fabrication thereof; said self-gating resistive storage device comprises: lower electrodes; insulating dielectric layers arranged perpendicular to, and intersecting with, the lower electrodes to form a stacked structure, said stacked structure being provided with a vertical trench; a gating layer grown on the lower electrodes by means of self-alignment technique, the interlayer leakage channel running through the gating layer being isolated via the insulating dielectric layers; a resistance transition layer arranged in the vertical trench and connected to the insulating dielectric layers and the gating layer; and an upper electrode arranged in the resistance transition layer. In the storage device provided by the described technical solution, the gating layer is grown on the lower electrodes by means of self-alignment technique, such that the interlayer leakage channel running through the gating layer is isolated via the insulating dielectric layers; thus leakage between the upper and lower word lines through the gating layer is prevented, solving the technical problem in the prior art of leakage between the upper and lower word lines in a self-gating resistive storage device, and improving the reliability of the device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

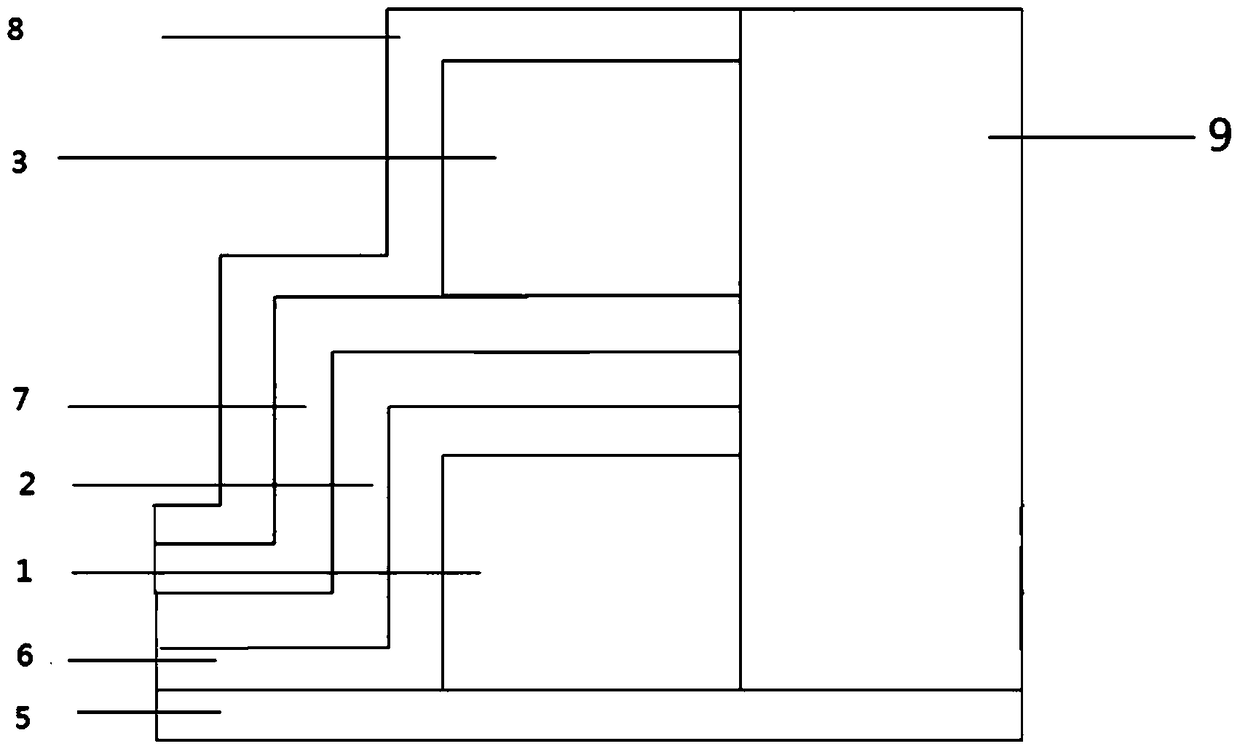

Self-gating device based on two-dimensional molybdenum oxide/molybdenum sulfide laminated structure and manufacturing method thereof

ActiveCN113241404AStrong miniaturizationImplementing the Self-Gating FeatureElectrical apparatusFinal product manufactureSemiconductor materialsMiniaturization

The invention discloses a self-gating device of a two-dimensional molybdenum oxide / molybdenum sulfide laminated structure and a manufacturing method of the self-gating device, and relates to the technical field of microelectronics. The self-gating device comprises an upper electrode layer, a lower electrode layer and a functional layer, wherein a functional layer material is located between the upper electrode layer and the lower electrode layer, the functional layer is formed by sequentially stacking a dielectric layer I and a dielectric layer II, the dielectric layer I is two-dimensional molybdenum oxide (alpha-MoO3), and the dielectric layer II is a semiconductor material of two-dimensional molybdenum sulfide (MoS2). Compared with the prior art, the self-gating device formed in a lamination mode solves the crosstalk problem in a cross integrated array under the condition that the occupied area is not enlarged; and the stacked structure of the dielectric layer I and the dielectric layer II realizes self-gating performance, shows good nonlinear characteristic, has the nonlinearity of 10<5>, and is extremely high in miniaturization, simple in process and cost-saving.

Owner:TIANJIN UNIVERSITY OF TECHNOLOGY

A self-selectable on-resistive memory device and its preparation method

ActiveCN105826468BPrevent leakageSolve technical problems of leakageSolid-state devicesSemiconductor devicesMaterials scienceSelf gating

The invention discloses a self-selectable resistive memory device and a preparation method thereof. The self-selectable resistive memory device comprises: a lower electrode; an insulating medium layer, which is vertically intersected with the lower electrode to form a stacked structure. In the stacked structure A vertical trench is provided; a gating layer is grown on the lower electrode by self-alignment technology, wherein the interlayer leakage channel flowing through the gating layer is isolated by the insulating medium layer; a resistance conversion layer is set In the vertical groove, it is in contact with the insulating medium layer and the gate layer; the upper electrode is arranged in the resistance conversion layer. In the storage device provided by the above technical solution, the gate layer is grown on the lower electrode by self-alignment technology, so that the interlayer leakage channel flowing through the gate layer is isolated by the insulating medium layer, and the leakage of the upper and lower word lines through the gate layer is avoided. Therefore, the technical problem of electric leakage between upper and lower word lines of the self-selectable on-resistance memory device in the prior art is solved, and the reliability of the device is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Self-gating resistive storage device having resistance transition layer in vertical trench in stacked structure of insulating dielectric layers and electrodes

ActiveUS10720578B2Improve equipment reliabilityPrevent leakageSolid-state devicesSemiconductor devicesPhysical chemistryEngineering

Provided are a self-gating resistive storage device and a method for fabrication thereof; said self-gating resistive storage device comprises: lower electrodes; insulating dielectric layers arranged perpendicular to, and intersecting with, the lower electrodes to form a stacked structure, said stacked structure being provided with a vertical trench; a gating layer grown on the lower electrodes by means of self-alignment technique, the interlayer leakage channel running through the gating layer being isolated via the insulating dielectric layers; a resistance transition layer arranged in the vertical trench and connected to the insulating dielectric layers and the gating layer; and an upper electrode arranged in the resistance transition layer. In the storage device provided by the described technical solution, the gating layer is grown on the lower electrodes by means of self-alignment technique, such that the interlayer leakage channel running through the gating layer is isolated via the insulating dielectric layers; thus leakage between the upper and lower word lines through the gating layer is prevented, solving the technical problem in the prior art of leakage between the upper and lower word lines in a self-gating resistive storage device, and improving the reliability of the device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

A motion signal extraction method and device for self-gated three-dimensional cardiac imaging

ActiveCN105266813BImprove image qualityDiagnostic recording/measuringSensorsBand-pass filterMultiple point

The invention provides a motion signal extracting method and device for self-gating three-dimensional cardiac imaging, and relates to the technical field of three-dimensional cardiac imaging. The method includes the steps that according to the TureFISP sequence, cardiac cine imaging data are obtained by adopting a multi-echo three-dimensional radial mixed collecting mode; signal values of multiple points are obtained from radial sampling lines of all collecting layers in the cardiac cine imaging data, and average values of the signal values of the multiple points are determined to serve as navigation signals; the navigation signals are subjected to inverse Fourier transformation to be transformed into an image domain, and heartbeat and breathing motion mixed signals are obtained through weighting; the heartbeat and breathing motion mixed signals are filtered through a band-pass filter to obtain heartbeat signals and breath signals; according to the heartbeat signals and the breath signals, the cardiac cine imaging data are arrayed and synchronized again to generate three-dimensional cardiac images. The problem that in the prior art, the quality of the rebuilt cardiac cine images is affected as obtained motion signals are inaccurate is solved.

Owner:SHENZHEN INST OF ADVANCED TECH CHINESE ACAD OF SCI

Super computing system oriented self-gating boundary scan test method and device

ActiveCN103163451BIncrease flexibilityReduce the numberElectrical testingTest efficiencyControl signal

Owner:NAT UNIV OF DEFENSE TECH

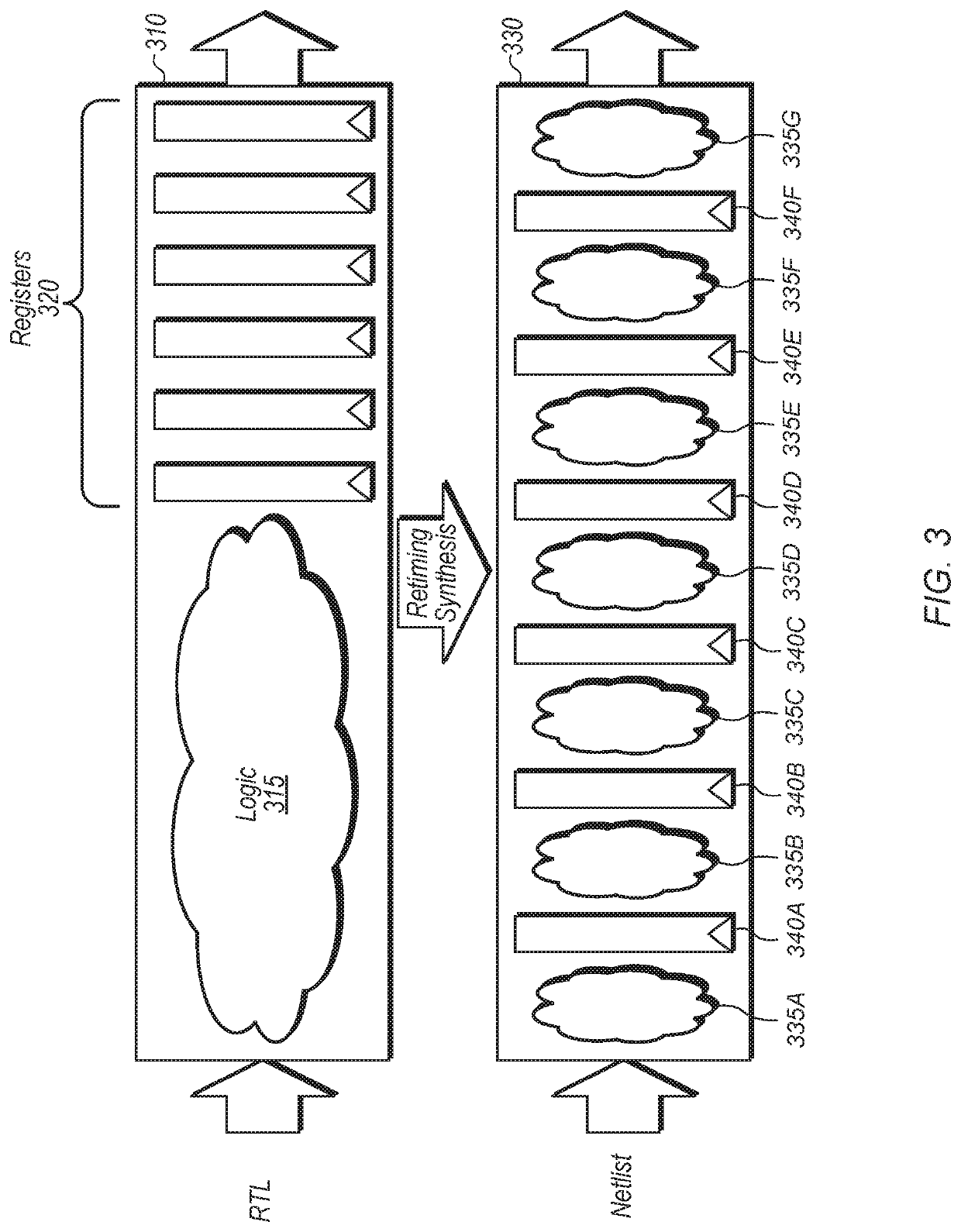

Stripe based self-gating for retiming pipelines

ActiveUS10917094B2Power reduction by control/clock signalDigital storageHemt circuitsLow power dissipation

Systems, apparatuses, and methods for implementing stripe-based self-gating and change detect signal propagation for retiming pipelines are disclosed. A circuit includes one or more stripes, with each stripe including a plurality of stages of registers, with each stage only receiving input signals from the preceding stage. For a given stripe, the first stage of registers are self-gated to reduce power consumption by only clocking a group of registers when any of their input signals change. The self-gating signals of the first stage of registers are combined together to create a change detect signal which is passed through a register and provided to a second stage of registers as a clock-enable signal. Accordingly, the second stage registers are only clocked when the change detect signal indicates a change will be forwarded from the first stage. This reduces power consumption for the second stage without causing the area increase associated with self-gating circuitry.

Owner:ADVANCED MICRO DEVICES INC

A trigger group clock gating method based on activity similarity

ActiveCN106527575BIncreased gated periodReduce dynamic power consumptionGenerating/distributing signalsDigital signal processingClock tree

The invention discloses an activity similarity based trigger grouping clock gating method. The method includes the following steps: acquiring an activity vector of each trigger in a typical working mode on the basis of gate level simulation in a typical working mode of a kernel of a digital signal processor, and acquiring the transition rate of the triggers and the correlation among the triggers by counting and processing the activity vectors of the triggers; performing initial layout by using a layout tool, and acquiring initial positions of the triggers in the kernel of the digital signal processor in a layout; and achieving grouping of the triggers by using transition rate information and trigger position data; achieving clock gating through trigger grouping information and the XOR gate self-gating method; and making a new layout for new generated net lists, and achieving clock tree comprehensive and power consumption simulation verification. The method can achieve trigger grouping clock gating of the kernel of the digital signal processor, can effectively prolong the gating period of a clock, and can reduce the dynamic power consumption.

Owner:RES INST OF SOUTHEAST UNIV IN SUZHOU

Digital self-gated binary counter

ActiveUS8983023B2Counting chain synchronous pulse countersCounting chain asynchronous pulse countersLogical combinationComputer module

An n-bit counter is formed from cascading counter sub-modules. The counter includes combinatorial control logic coupled to a lower order counter sub-module. The control logic is arranged to clock gate at least one higher order counter sub-module dependent on a logical combination of outputs of the lower order counter sub-module and where the control logic uses pipelining to store at least one previous control logic output for use in determining a later control logic output.

Owner:NXP USA INC

Method and apparatus for self gate pumped NMOS high speed switch

Owner:INTEGRATED DEVICE TECH INC