Super computing system oriented self-gating boundary scan test method and device

A technology of boundary scan and test method, which is applied in the direction of measuring devices, measuring electricity, and measuring electrical variables, etc., can solve problems such as poor flexibility and complicated backplane wiring, and achieve the effects of improving efficiency, improving flexibility, and reducing the number

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

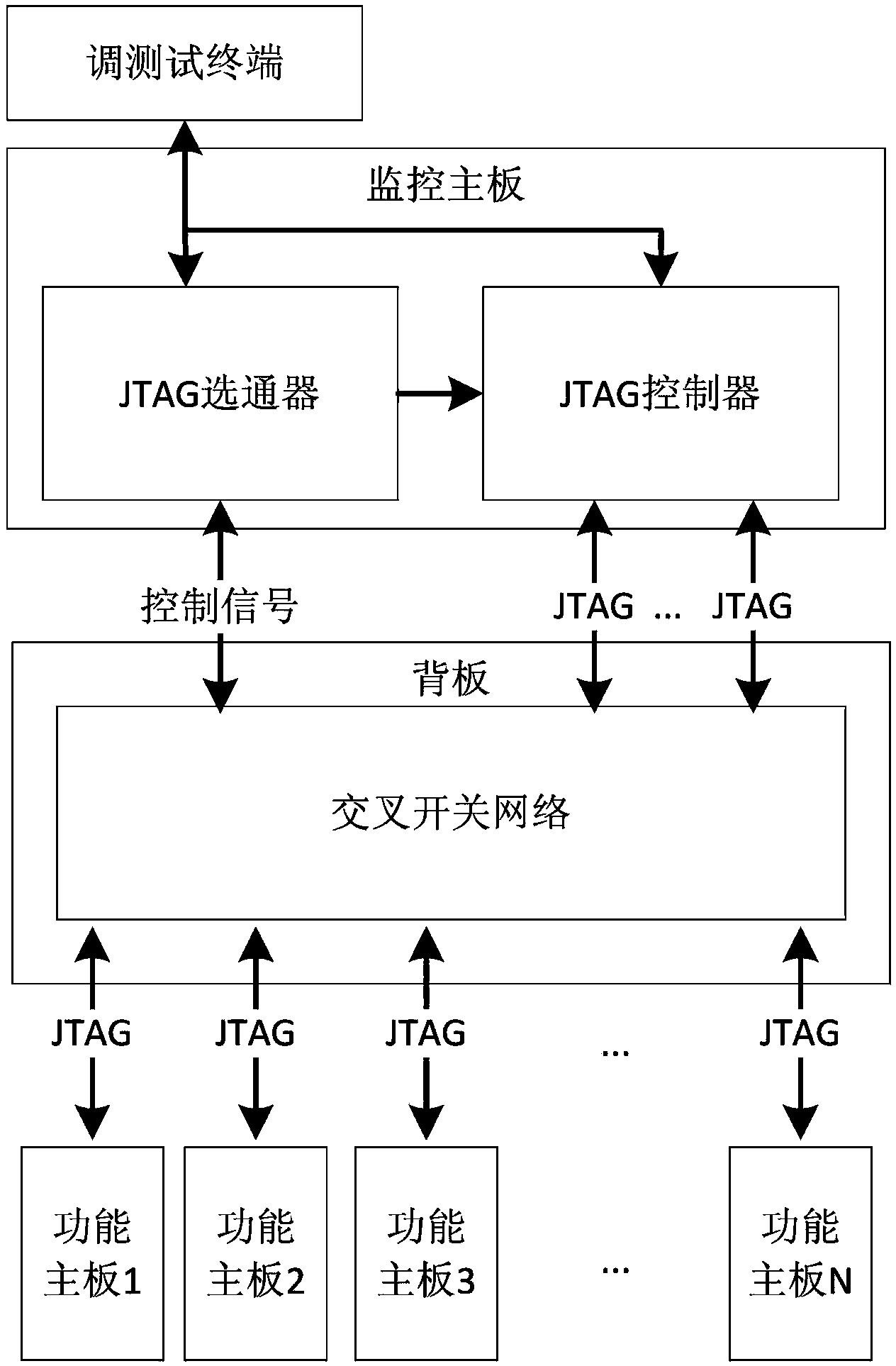

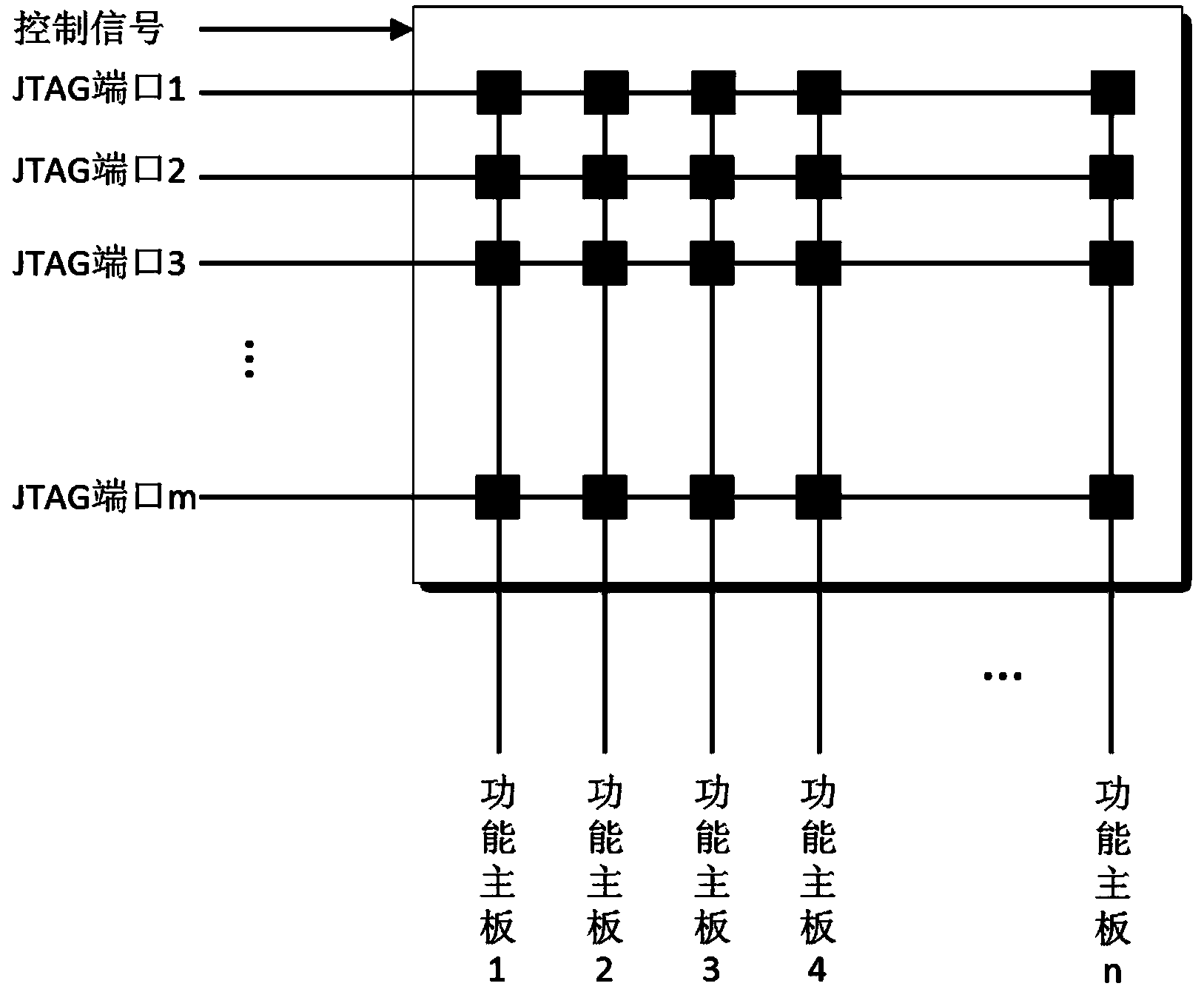

[0029] The supercomputing system-oriented self-selection boundary scan debugging test method of the present invention calculates the optimal tuning test JTAG line according to the input target motherboard number, debugging test command and debugging test concurrency, so as to determine the JTAG output port of the monitoring motherboard and issue control Signal; use the crossbar network on the backplane to receive the control signal of the JTAG strobe, change the on-off of each switch in the crossbar network according to the control signal, complete the strobe and use the gated JTAG output port to execute the debug test command.

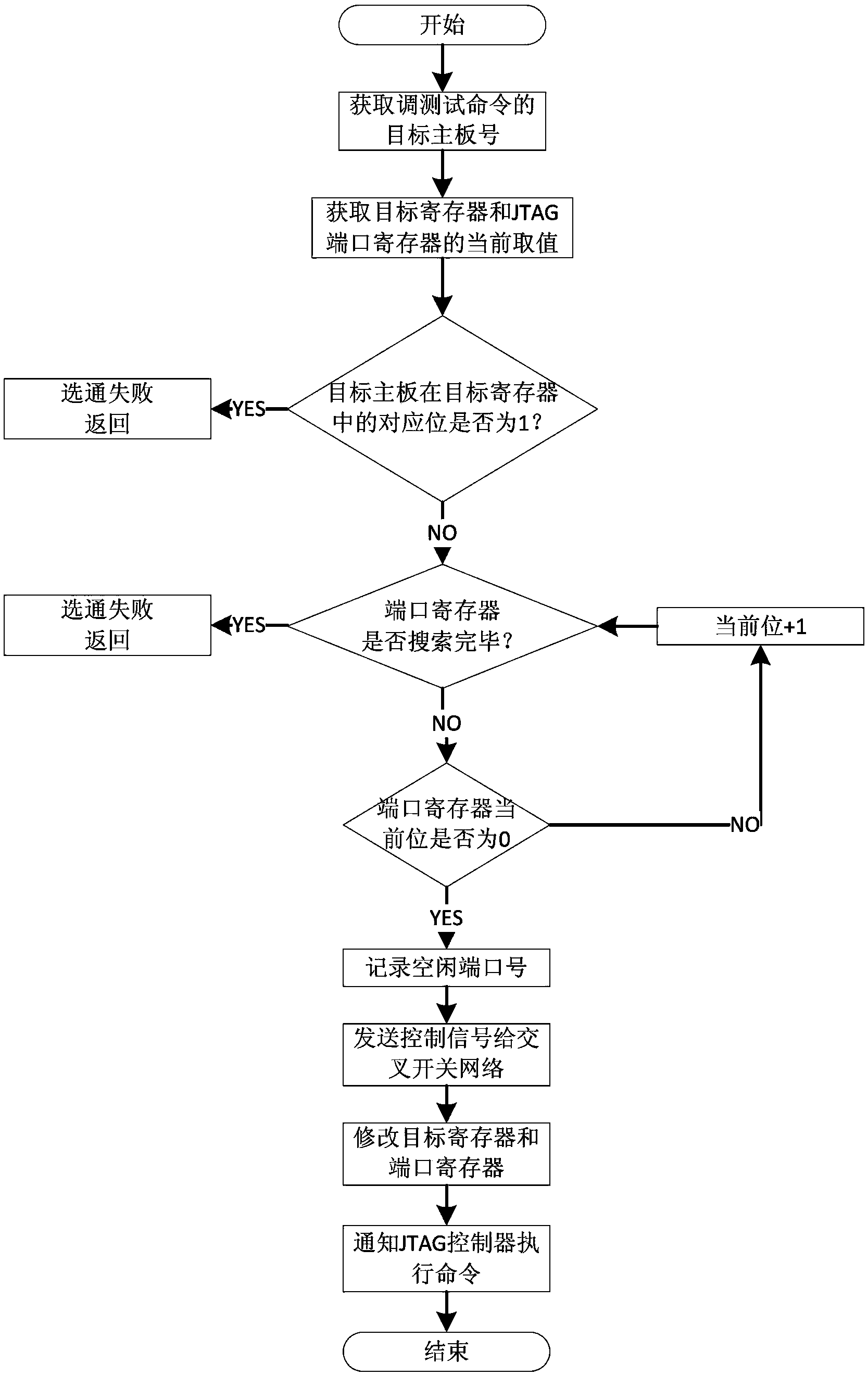

[0030] When performing strobing, a certain number of target registers are set according to the number of mainboards to be tested, and if a certain bit is 1, it indicates that the mainboard to be tested corresp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More