A trigger group clock gating method based on activity similarity

A clock gating and flip-flop technology, applied in the field of gate-level clock gating, can solve the problem of difficulty in ensuring clock gating efficiency, and achieve the effect of increasing the gating period and reducing dynamic power consumption.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

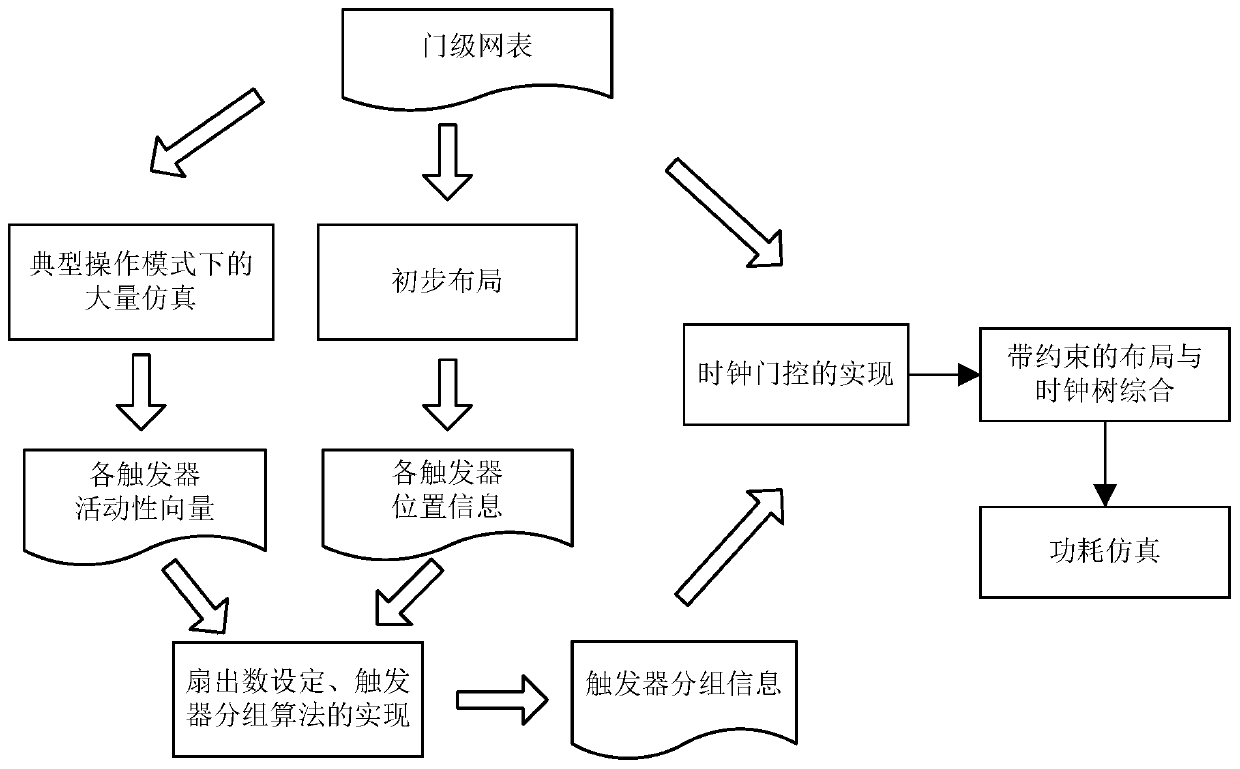

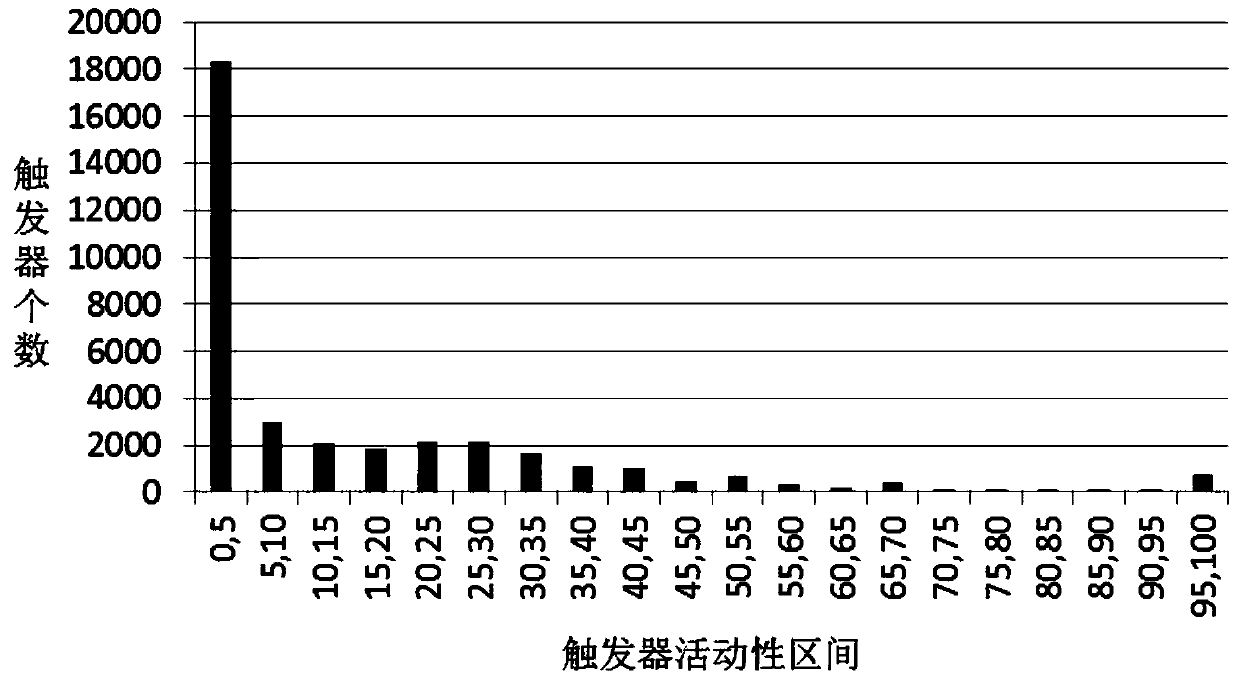

[0043] A DSP IP kernel CEVA-TL421 of CEVA Company is selected as the design verification object, and a synthesis tool DC of Synopsys Company is used to realize synthesis clock gating. For clock gating based on activity similarity, the activity information of the flip-flop needs to be obtained first. Flip-flop activity files are obtained through a large number of simulations of the synthesized gate-level netlist in typical modes. The file mainly includes three parts: the file information part, each trigger pin code, and each cycle trigger pin flip statistics. The second and third parts can be divided into two files and processed separately. Use the Perl script to split and match the two files, and count the activity vector of the trigger by matching the same pin. For the trigger pin code file, divide it by each trigger; for the trigger pin flip file of each period, divide it by period. The activity vector obtained by statistics is a binary vector. In the flip-flop activity v...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More