Self-gating Resistive Random-Access Memory device and preparation method thereof

A resistive memory, self-selecting technology, applied in the field of microelectronics, can solve the problems of device reliability and large leakage, and achieve the effects of improving reliability, avoiding leakage, and solving leakage between upper and lower word lines.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

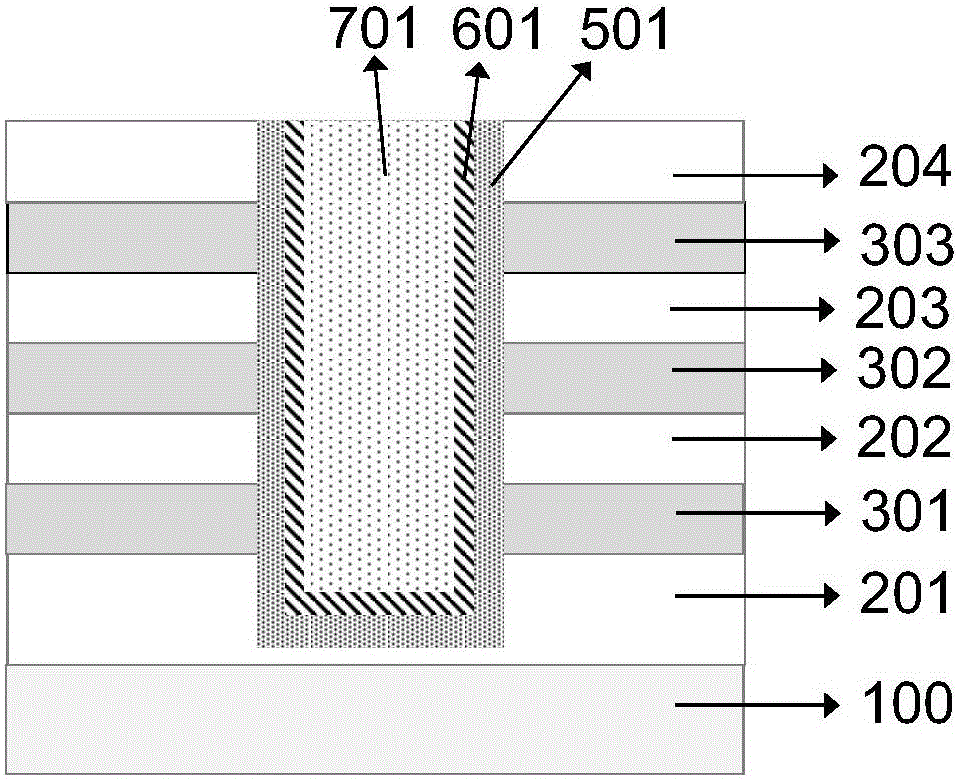

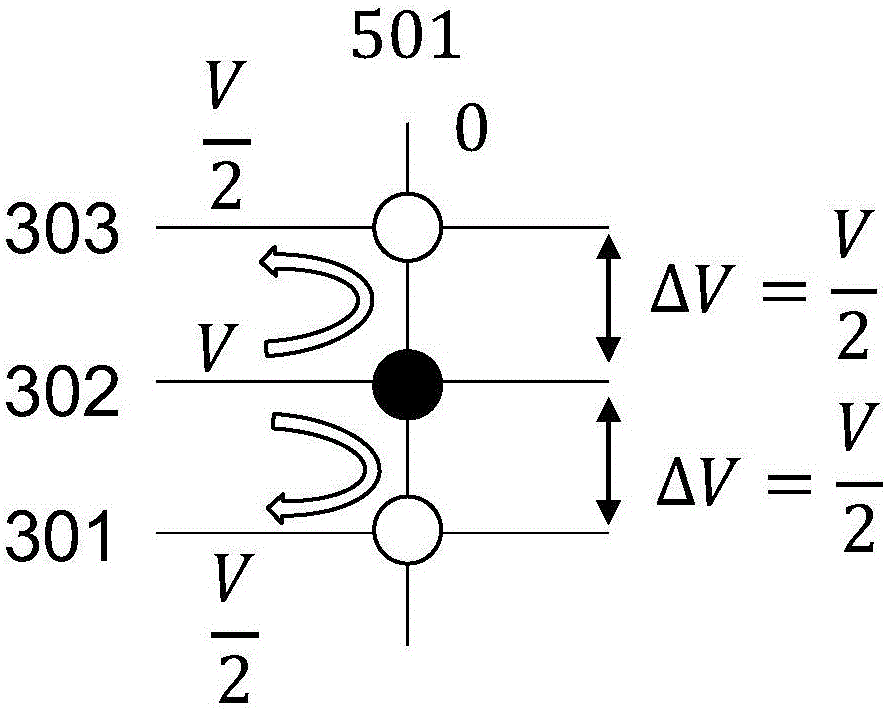

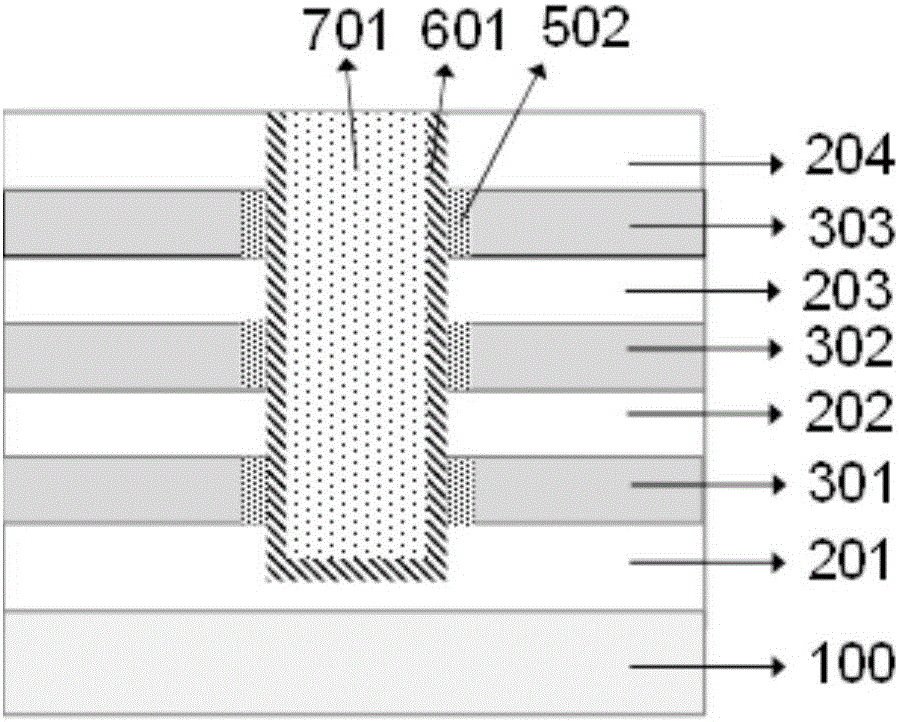

[0049] An embodiment of the present application provides a self-selectable on-resistive memory device, including:

[0050] lower electrode;

[0051] The insulating dielectric layer is vertically intersected with the lower electrode to form a stack structure, and a vertical groove is arranged in the stack structure;

[0052] The gating layer is grown on the lower electrode by self-alignment technology, wherein the interlayer leakage channel flowing through the gating layer is isolated by an insulating dielectric layer;

[0053] The resistance conversion layer is arranged in the vertical trench and connected to the insulating medium layer and the gate layer;

[0054] The upper electrode is arranged in the resistance conversion layer.

[0055] The self-selectable on-resistive memory device provided by the embodiment of the present application is illustrated below by taking the three-layer conductive lower electrode as an example, but the present invention does not limit the numbe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More