Overlay mark and method for forming the same

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

third embodiment

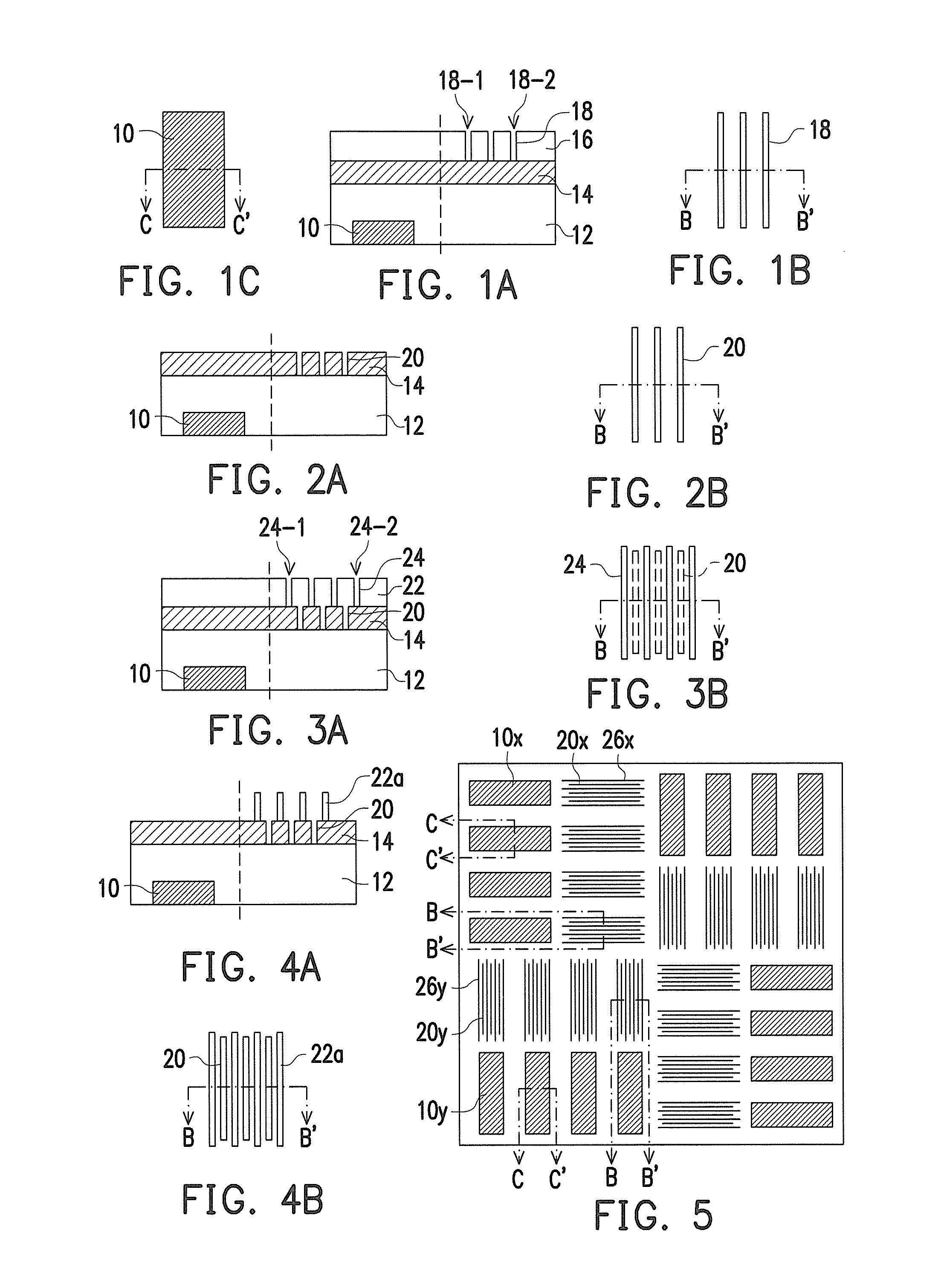

[0022]In addition, for the cases that each group of patterns has a linear shape for each pattern in the group, although there are a specific number of sets of alternately arranged linear patterns defined by the first lithography step and linear patterns defined by the second lithography step arranged in a particular manner in this invention, there may alternatively be a different number of such sets of linear patterns arranged in a different manner.

first embodiment

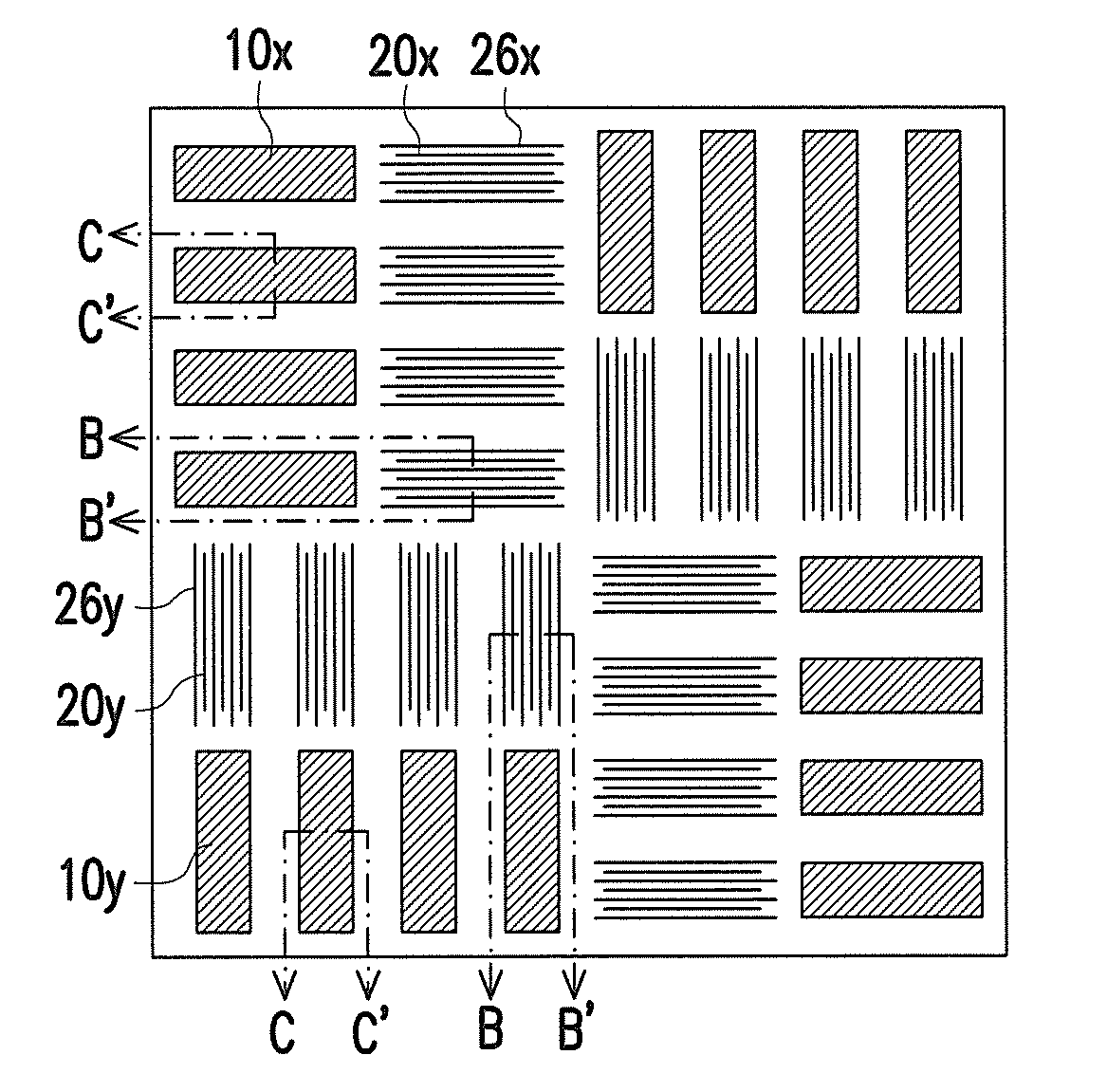

[0023]FIGS. 1A to 3A, 1B to 3B and 1C schematically illustrate a method for forming an overlay mark for a LELE-type DPL process according to this invention, wherein FIGS. 1A to 3A are cross-sectional views, FIGS. 1B to 3B are top views of linear patterns of the current layer with line B-B′ corresponding to the cross-sectional views, and FIG. 1C is a top view of a linear pattern of the previous layer in the overlay mark with line C-C′ corresponding to the cross-sectional views.

[0024]It is particularly noted that only one linear pattern of the previous layer is illustrated in the figures and described below for both of the x-directional linear pattern and the y-directional linear pattern of the previous layer, since both of them have the same basic shape. Similarly, only one set of parallel linear patterns of the current layer is illustrated in the figures and described below for both of the x-directional linear patterns and the y-directional linear patterns of the current layer defin...

second embodiment

[0030]Though the linear patterns of the current layer defined by the second lithography step are trenches (24) in the second photoresist layer (22), they may alternatively be solid line patterns form from the second photoresist layer, as described in this invention and schematically illustrated in FIGS. 4A and 4B, wherein FIG. 4A and FIG. 4B are a cross-sectional view and a top view, respectively.

[0031]Referring to FIGS. 4A and 4B, in the second lithography step of the DPL process in the second embodiment of this invention, a second photoresist layer is formed in the overlay mark region and the device area (not shown), and then a plurality of parallel solid line patterns 22a (the third x-directional patterns and the third y-directional patterns) of the current layer are formed from the second photoresist layer, simultaneously with the formation of a second part of the patterns of the current layer in the device area (not shown). The solid line patterns 22a defined by the second lith...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More