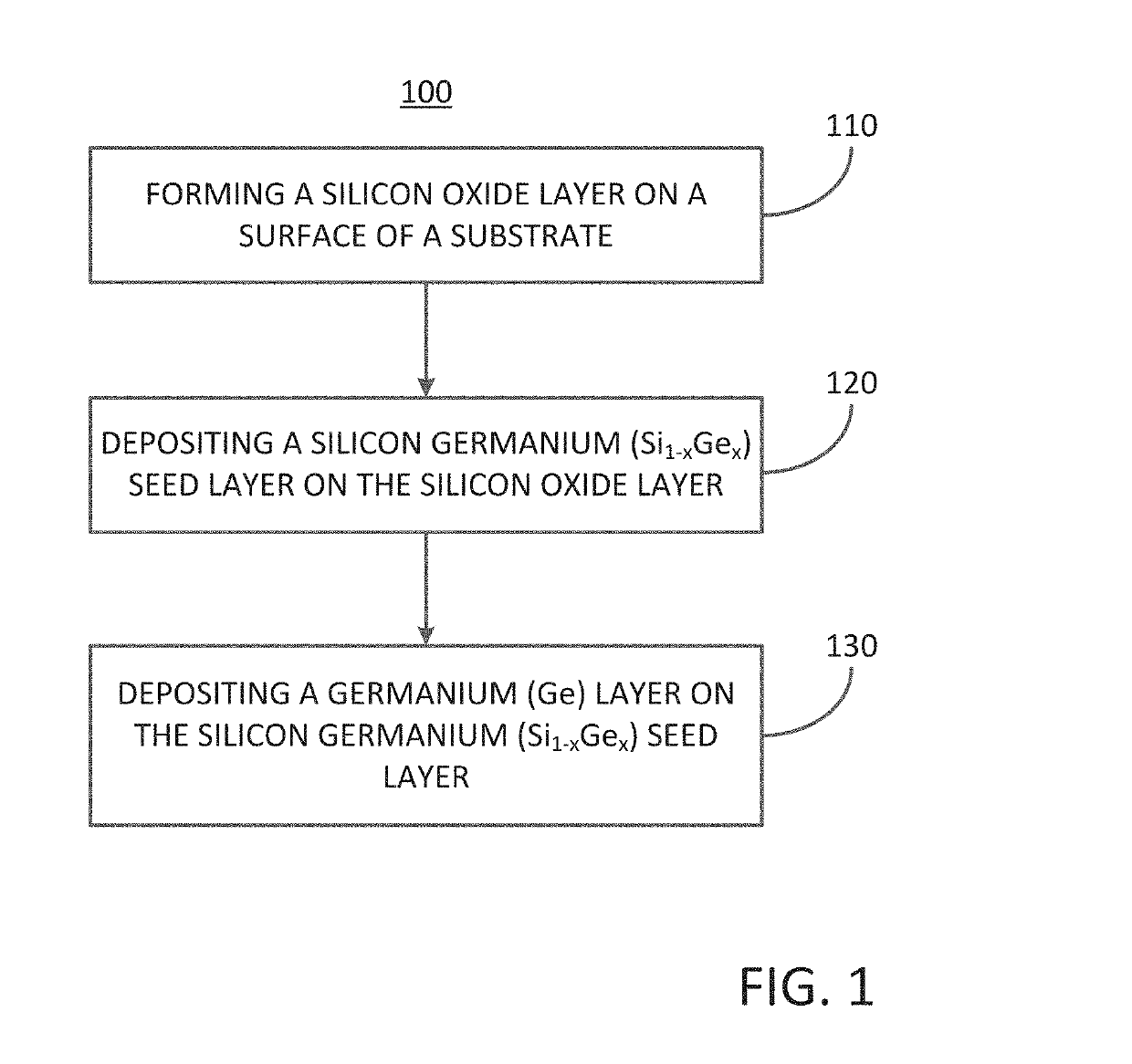

Methods for forming a semiconductor structure and related semiconductor structures

a semiconductor structure and semiconductor technology, applied in the direction of semiconductor devices, basic electric elements, electrical appliances, etc., can solve the problems of difficult to obtain advantageous ultra-shallow junctions, large integration and device design challenges, and use of bulk materials other than silicon

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

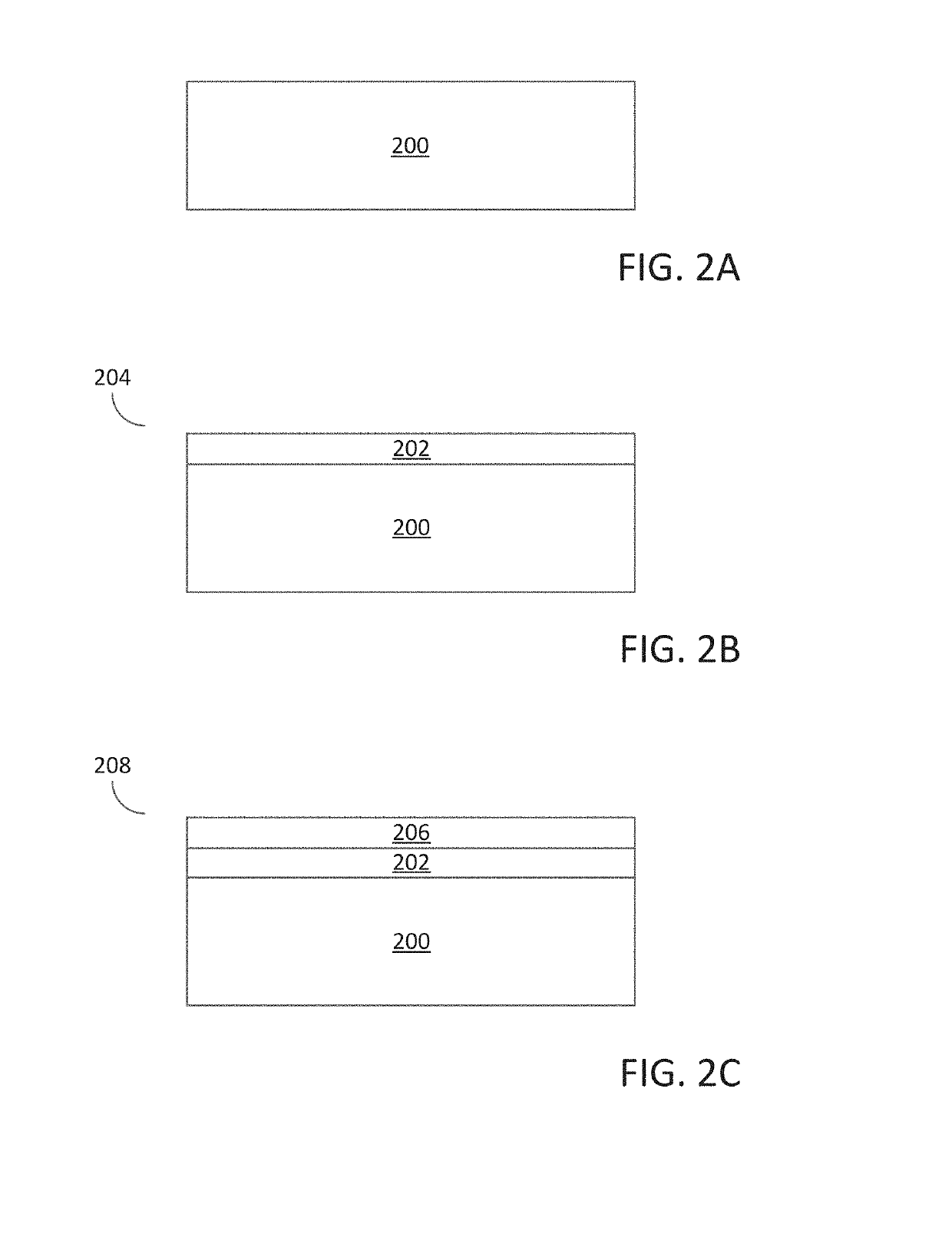

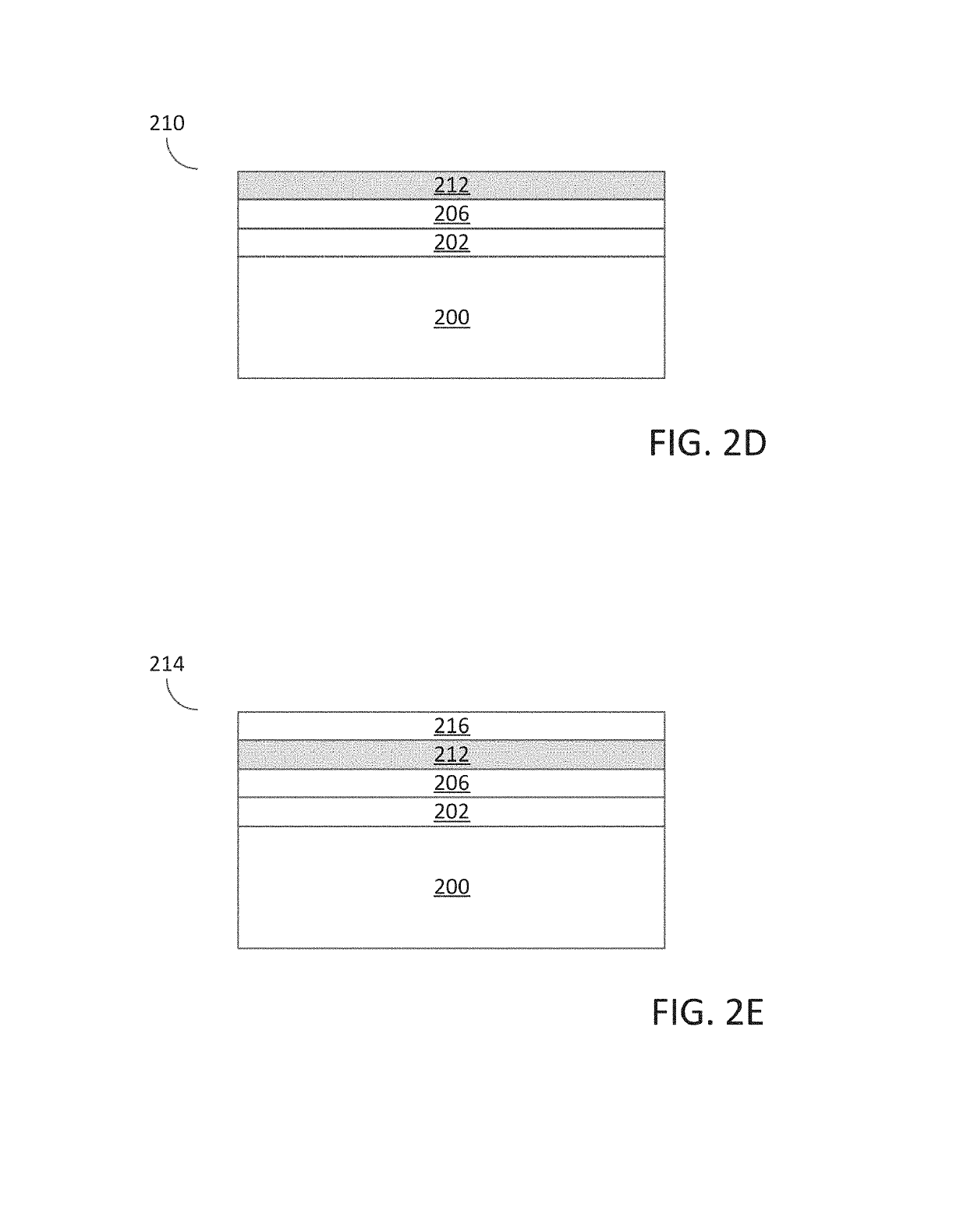

Embodiment Construction

[0014]Although certain embodiments and examples are disclosed below, it will be understood by those in the art that the invention extends beyond the specifically disclosed embodiments and / or uses of the invention and obvious modifications and equivalents thereof. Thus, it is intended that the scope of the invention disclosed should not be limited by the particular disclosed embodiments described below.

[0015]As used herein, the term “substrate” may refer to any underlying material or materials that may be used, or upon which, a device, a circuit or a film may be formed.

[0016]As used herein, the term “silicon germanium” and “Si1-xGex” may refer to an alloy of silicon and germanium, wherein the ratio of germanium to silicon may range as 1≥x≥0.

[0017]As used herein, the term “chemical vapor deposition” may refer to any process wherein a substrate is exposed to one or more volatile precursors, which react and / or decompose on a substrate surface to produce a desired deposition.

[0018]In the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More