Package substrate and flip-chip package circuit including the same

a technology of packaging substrate and flip-chip package circuit, which is applied in the direction of printed circuit non-printed electric components, semiconductor devices, semiconductor/solid-state device details, etc., can solve the problems of poor yield rate and reliability of products, insufficient affinity between primer materials and metal pillars or molding compounds, and high cost and restriction of primer materials

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

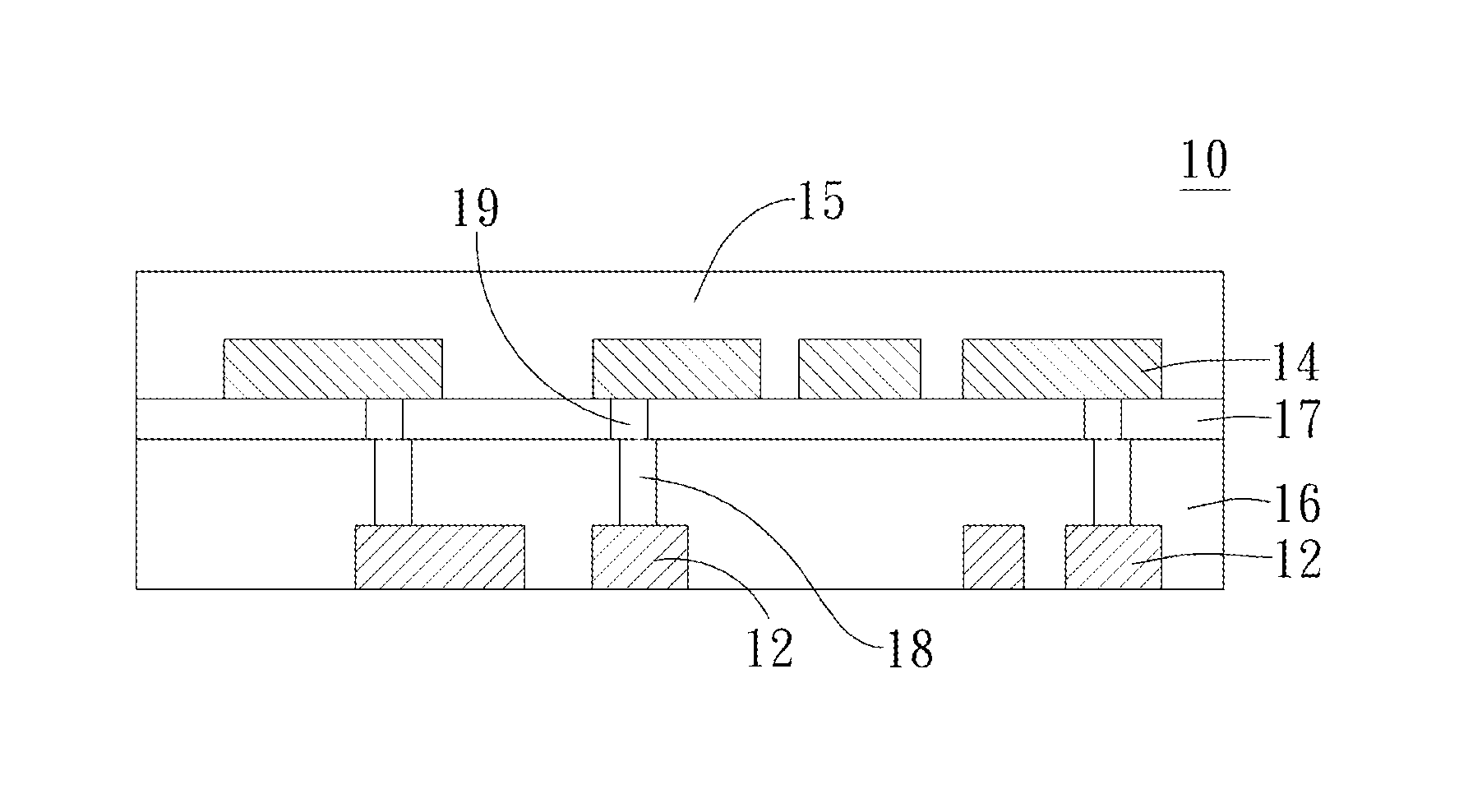

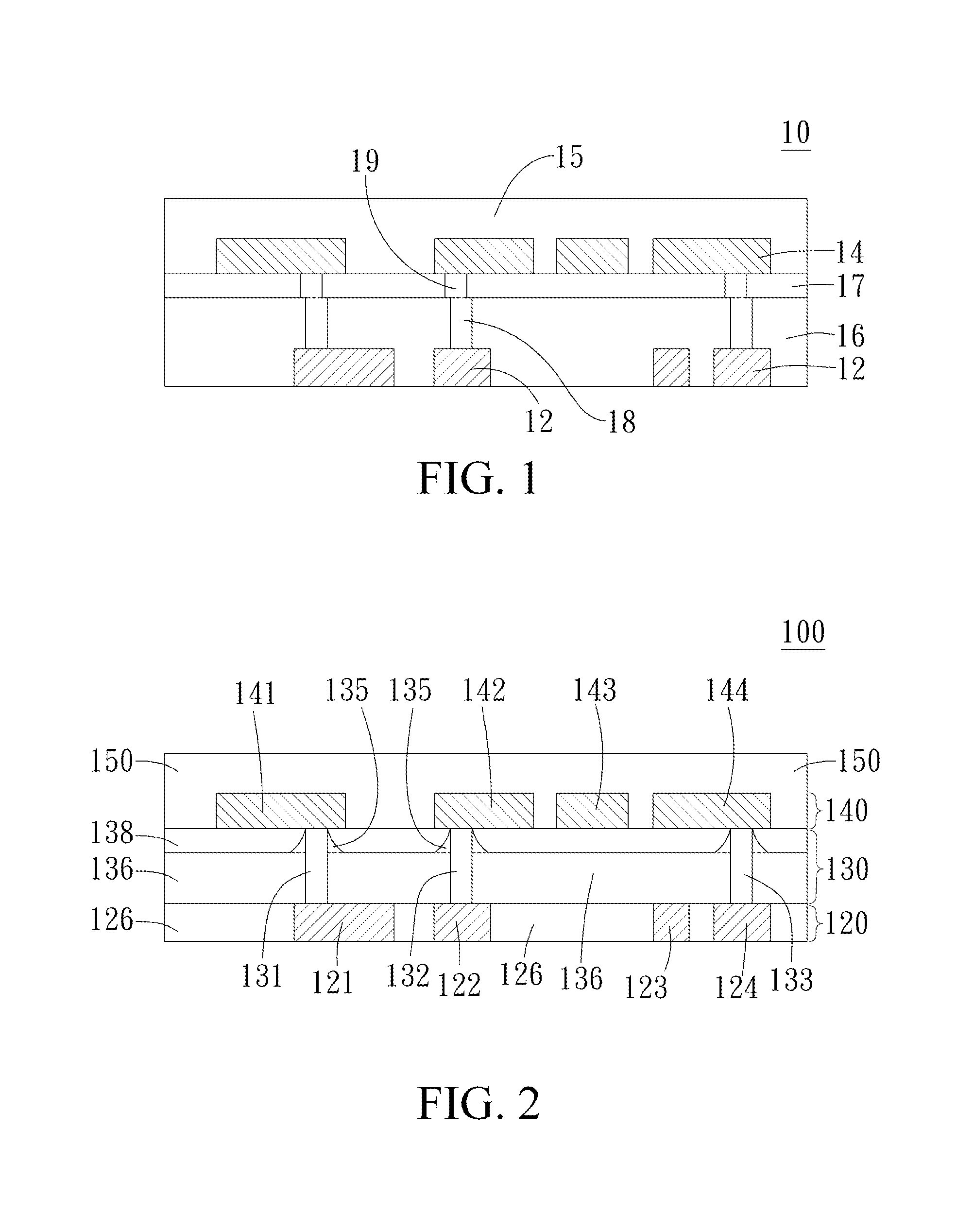

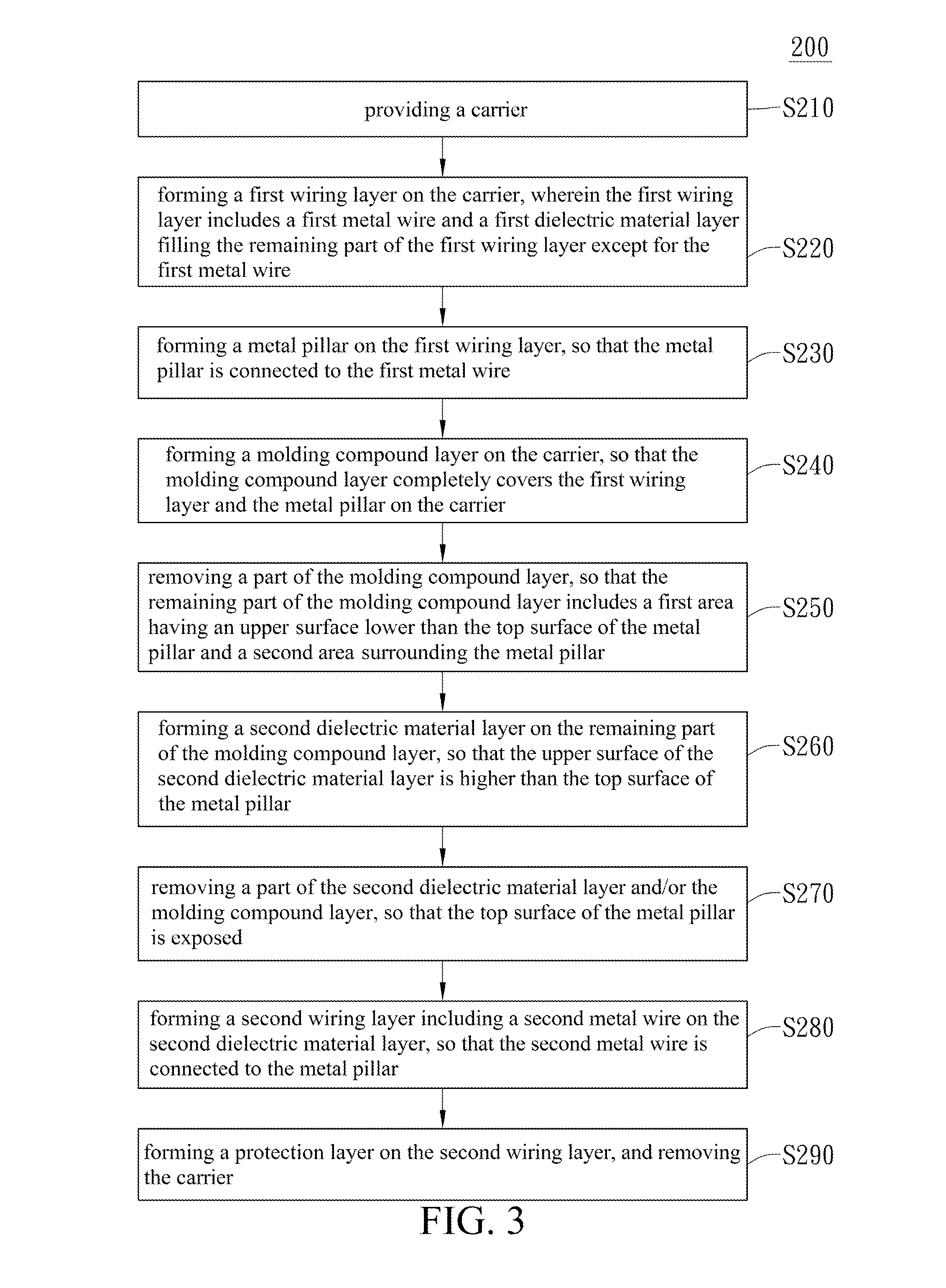

[0018]For further understanding and recognizing the fulfilled functions and structural characteristics of the disclosure, several exemplary embodiments cooperating with detailed description are presented as the following. Reference will now be made in detail to the preferred embodiments, examples of which are illustrated in the accompanying drawings.

[0019]In the following description of the embodiments, it is to be understood that when an element such as a layer (film), region, pattern, or structure is stated as being “on” or “under” another element, it can be “directly” on or under another element or can be “indirectly” formed such that an intervening element is also present. Also, the terms such as “on” or “under” should be understood on the basis of the drawings, and they may be used herein to represent the relationship of one element to another element as illustrated in the figures. It will be understood that this expression is intended to encompass different orientations of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More