Method to reduce power in a computer system with bus master devices

A technology of bus master control and equipment, applied in the field of power management

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

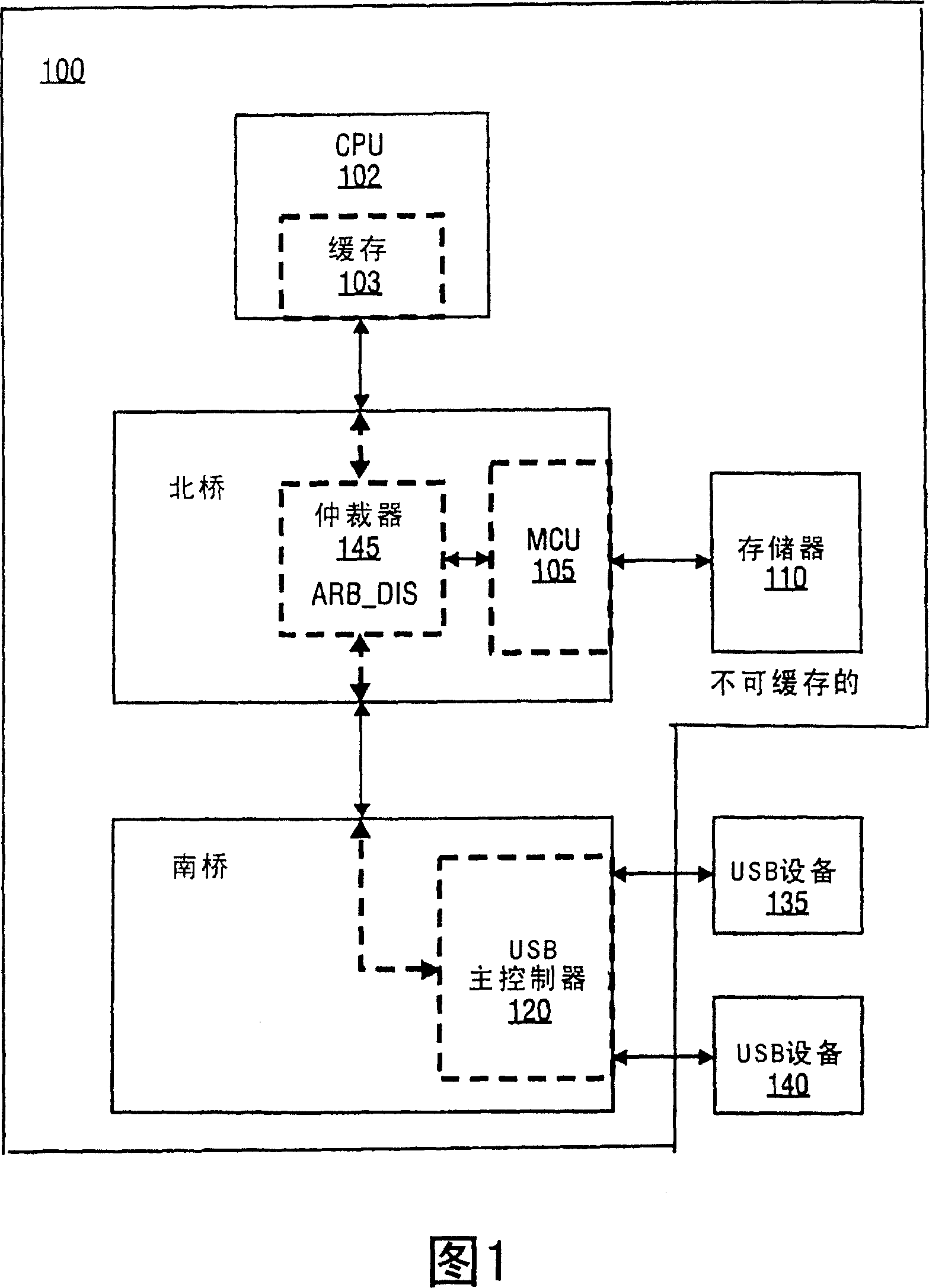

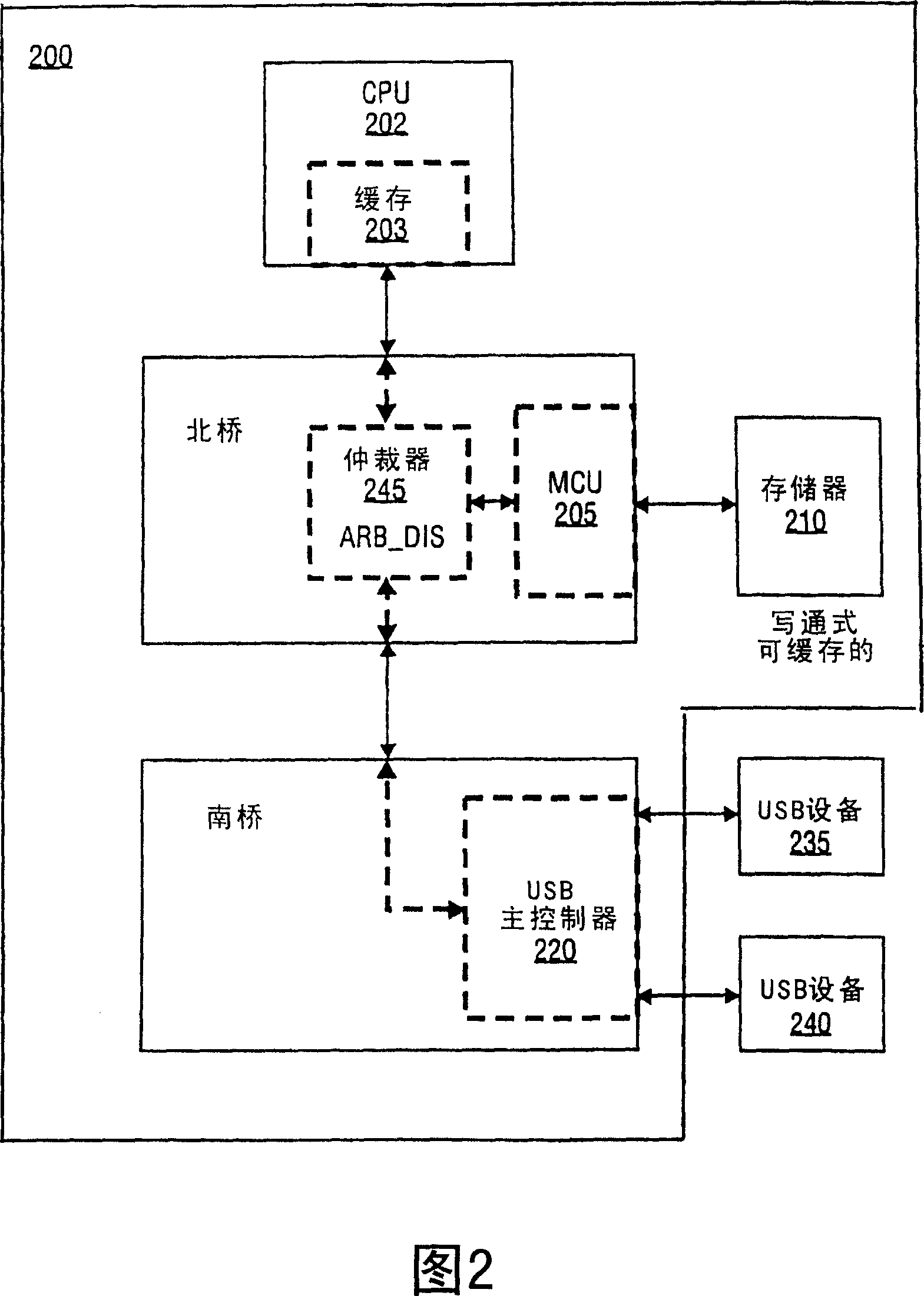

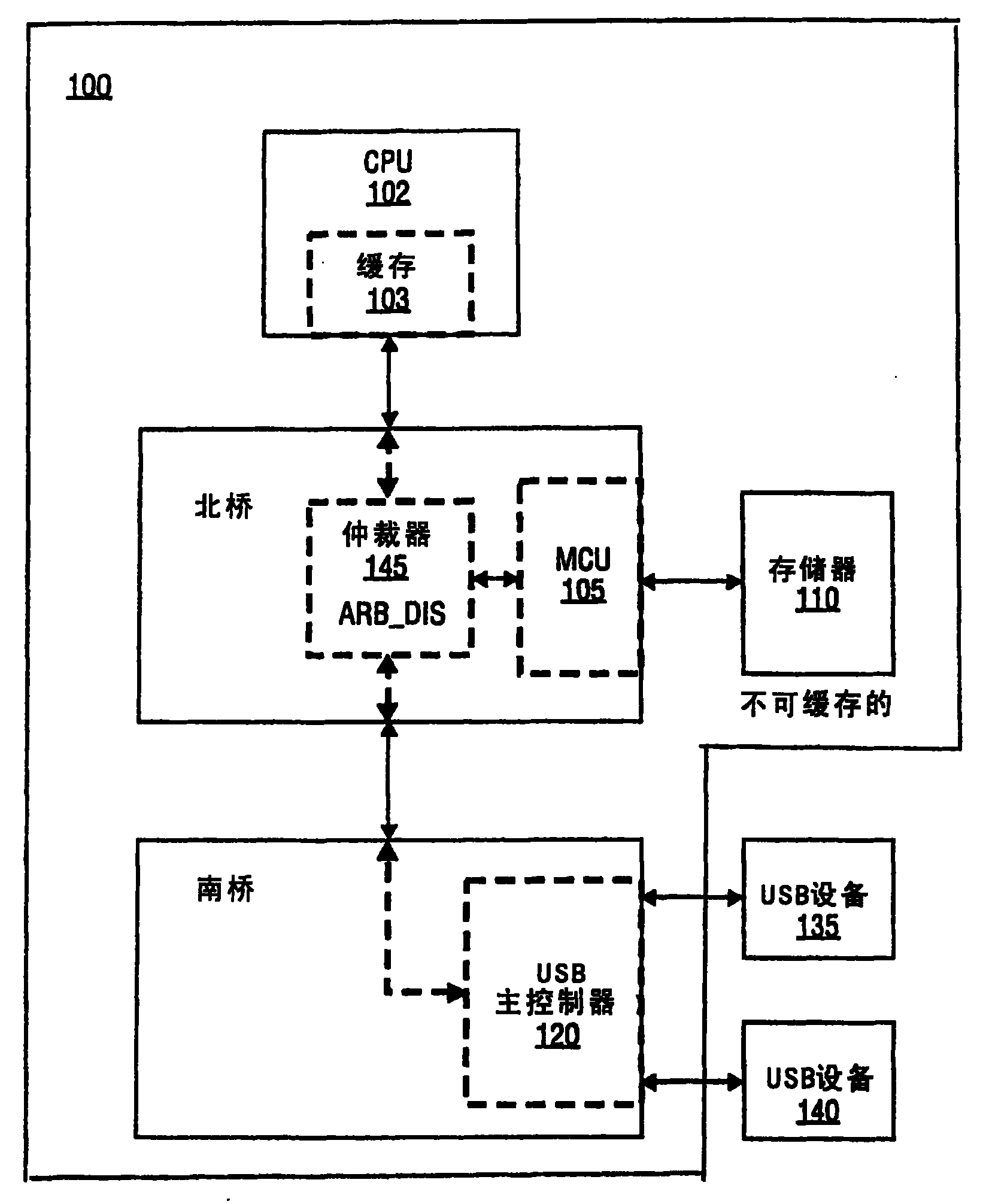

[0013] In one embodiment, a method is disclosed that avoids setting the BM STS bit to cause the processor to enter the C3 state while maintaining memory coherency. By changing the caching policy of the bus master buffer, many bus master activities can be done without cache coherency issues, thus eliminating the need for tracking of the BM_STS bit, allowing the processor to enter the C3 state more often.

[0014] In the following description, for purposes of explanation, numerous specific details are set forth in order to provide a thorough understanding of the present invention. It will be apparent, however, to one skilled in the art that the present invention may be practiced without these specific details. Also, in order to avoid unnecessary detail in the explanation, some well-known structures, procedures and devices are shown in block diagram form and are referenced in general terms.

[0015] Typically, a bus mastering status (BM_STS) bit is set with a bus mastering read ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More