Capacitor array for increasing memory capacitance on semiconductor base plate

A technology for capacitors and semiconductors, applied to the field of capacitor arrangement for increasing storage capacitance in semiconductor substrates

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

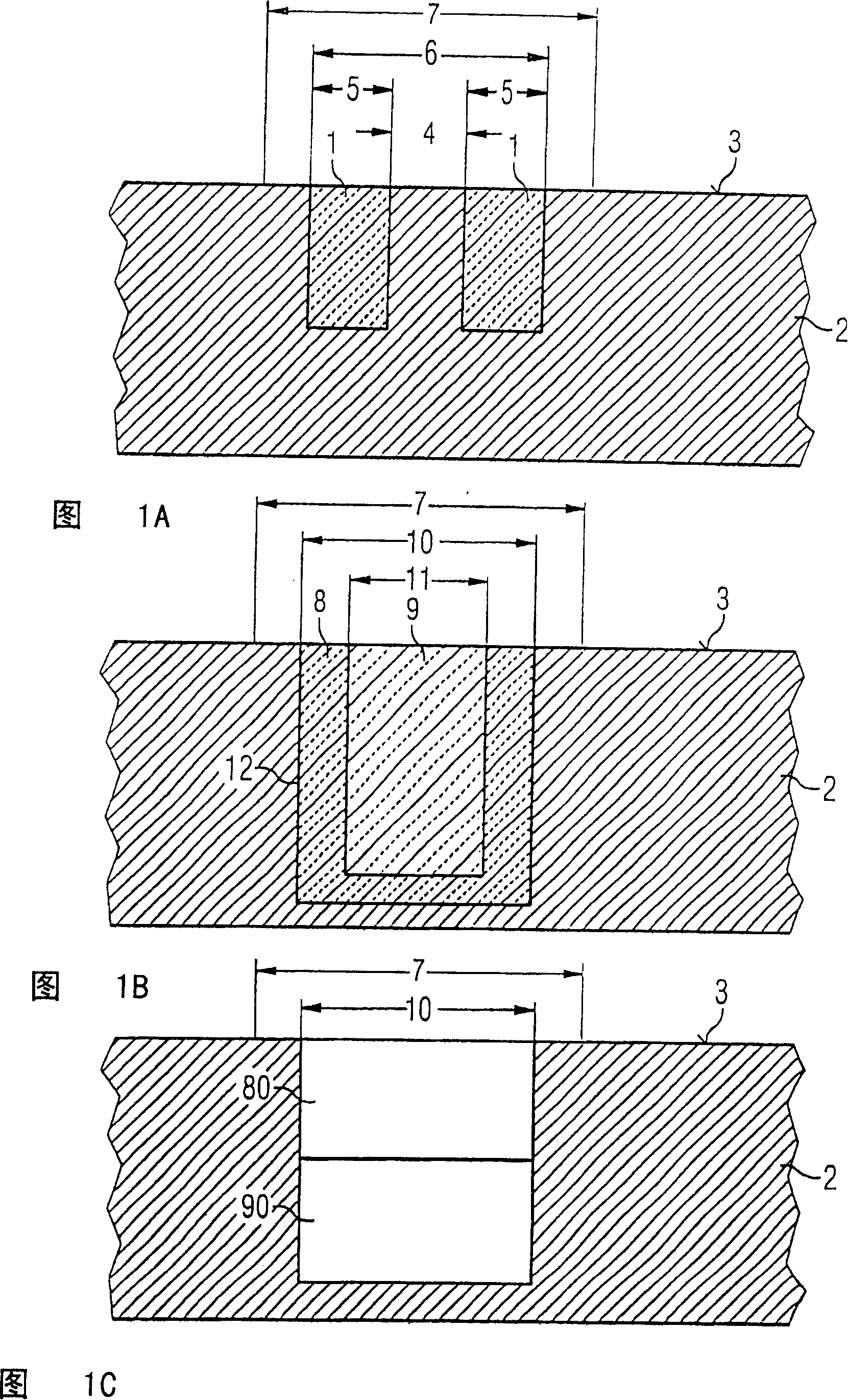

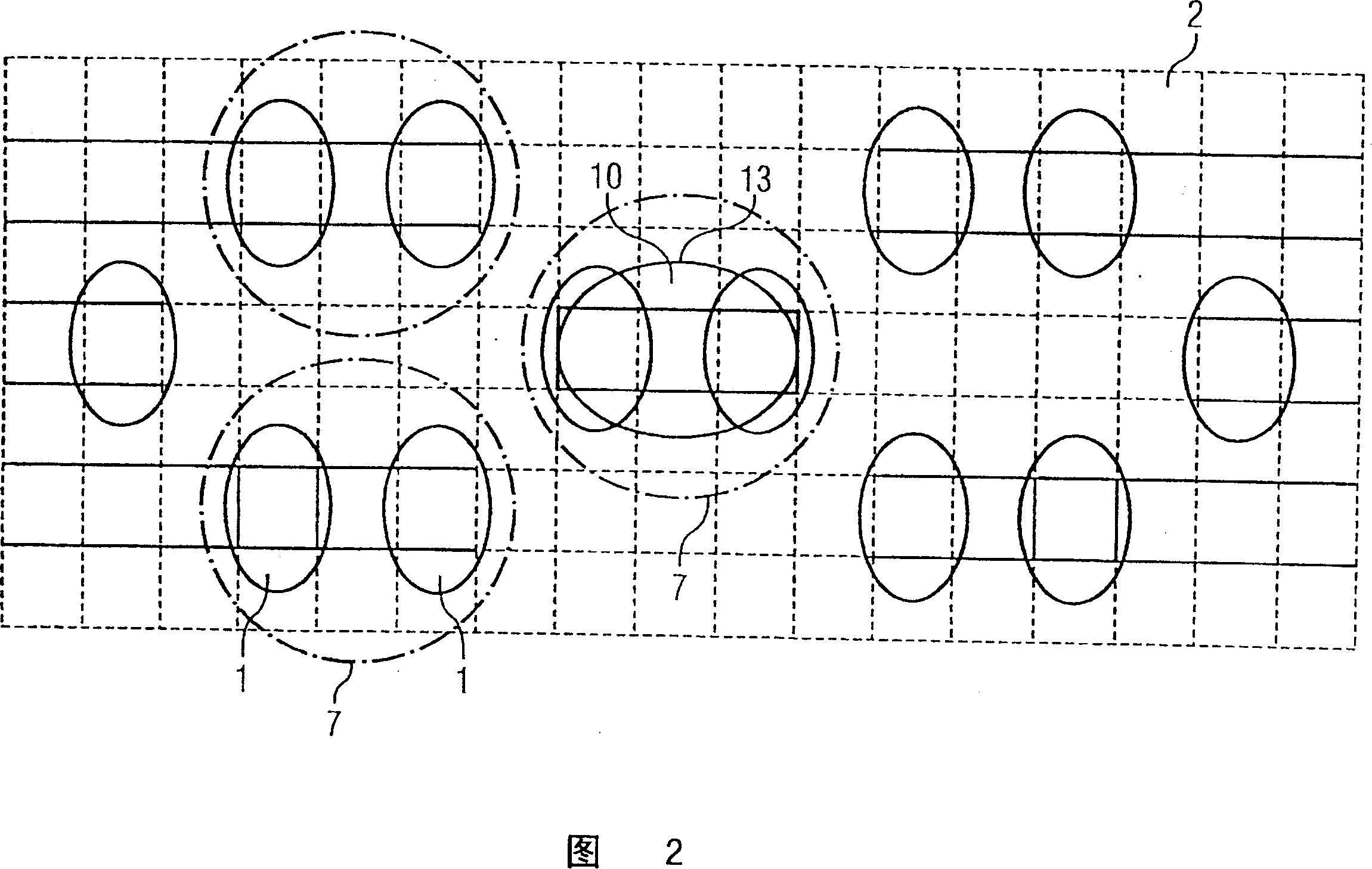

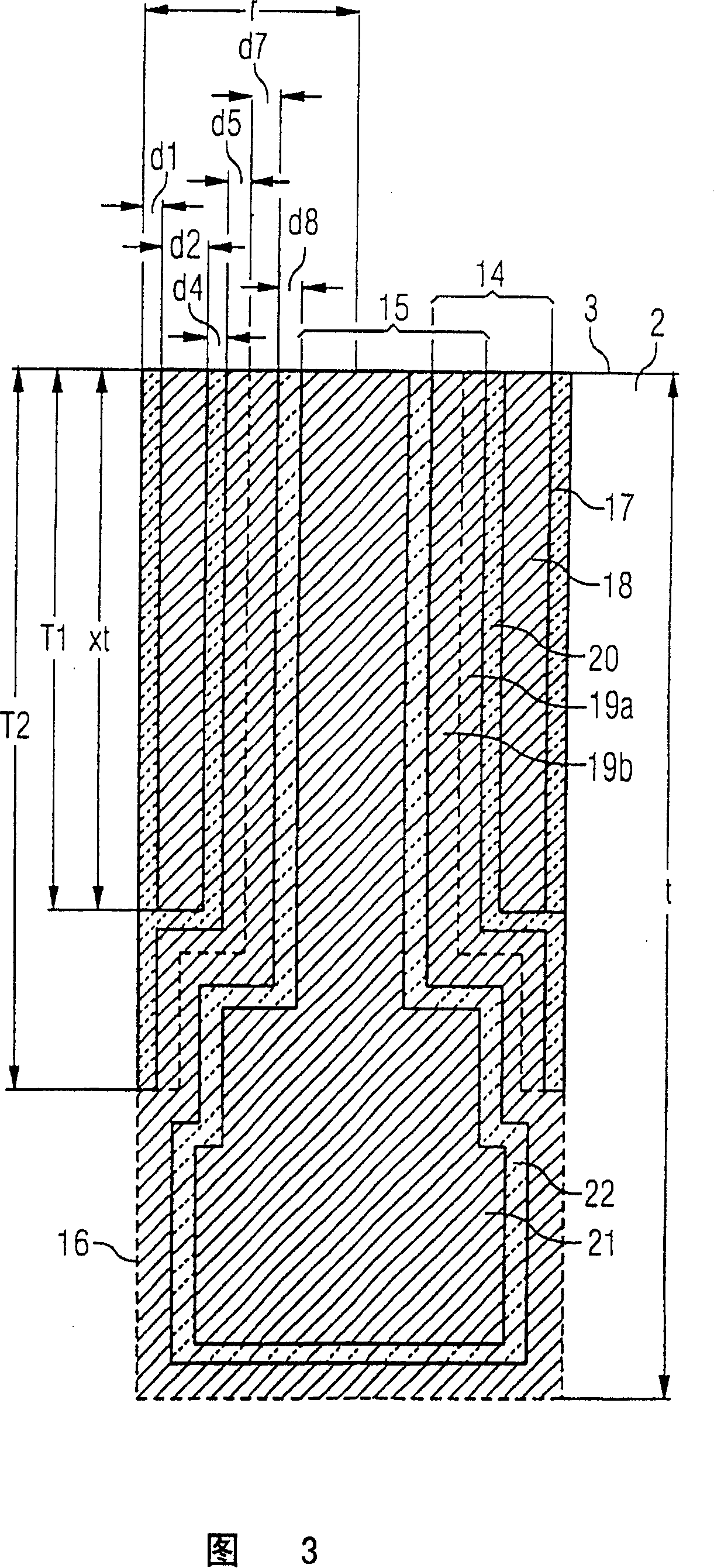

[0112]1A-1C show the arrangement of two capacitors 1 on a semiconductor substrate 2 , in this case the capacitors 1 are embodied as trench capacitors, ie they extend below the substrate surface 3 into the depth of the substrate 2 . For clarity of illustration, the description does not show the components required to drive the capacitor 1, such as selection transistors and corresponding intermediate connections. Likewise, without a detailed description of the individual layers of the capacitor 1, such as electrode layers and dielectric layers, the capacitor 1 has a distance 4 and also a diameter 5, which means that at least the area 6 occupied by two capacitors 1 results in the on the surface 3 of the substrate 2. In order to obtain the area requirement for the arrangement of the two capacitors 1, the minimum distance to the adjacent capacitor or the memory cell must also be taken into consideration, so the area 7 is obtained as the area requirement. If the area 7 is to be redu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More