Interface modular converter and method for configuration of FPGA

A technology for interface conversion and configuration data, which is applied to instruments, electrical digital data processing, etc., can solve problems such as increased software complexity, occupied bridge I/O resources, poor versatility, etc., and achieves improved flexibility and module compatibility Good performance, improved configuration speed and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

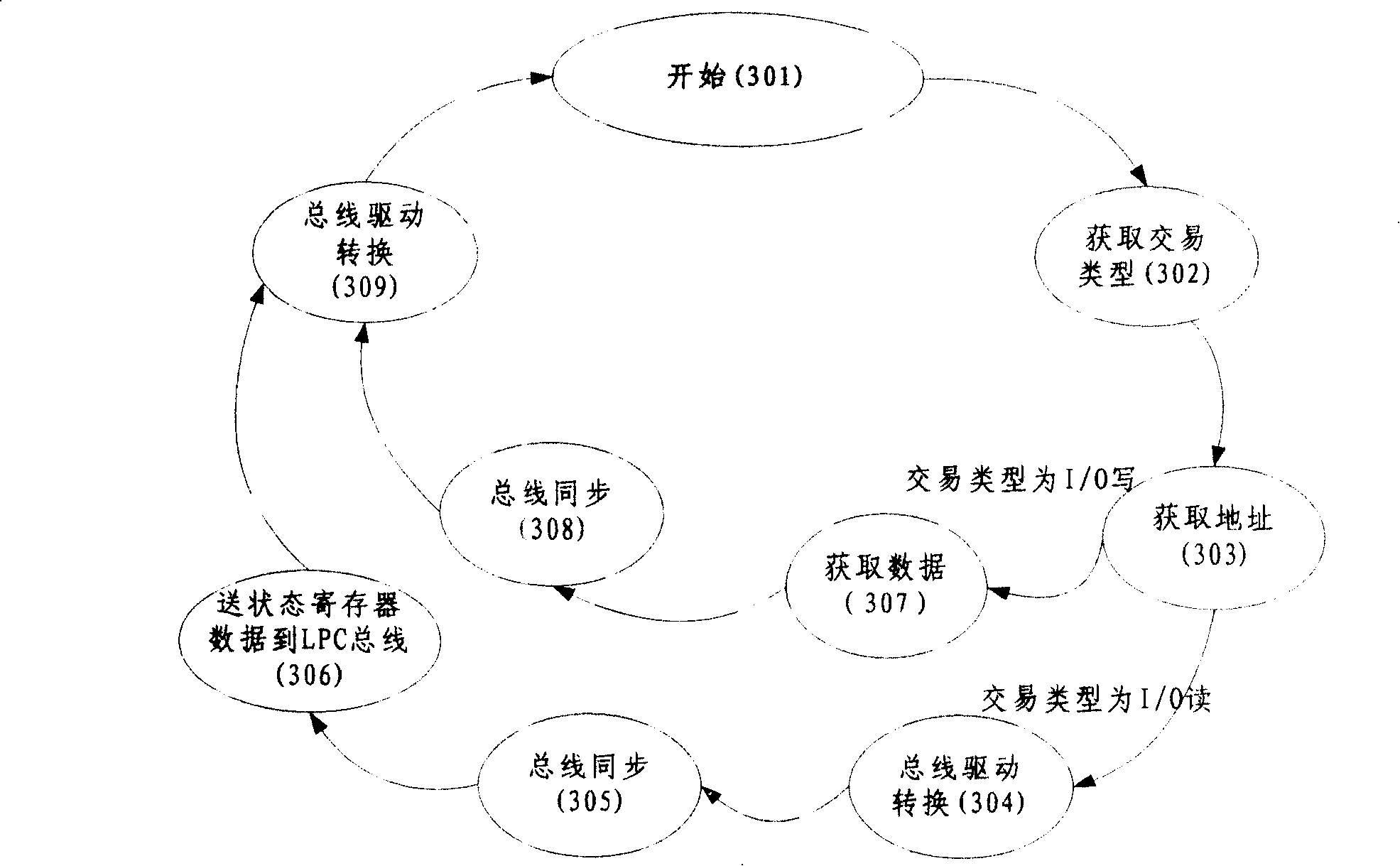

[0019] Below in conjunction with accompanying drawing, the implementation of technical scheme is described in further detail:

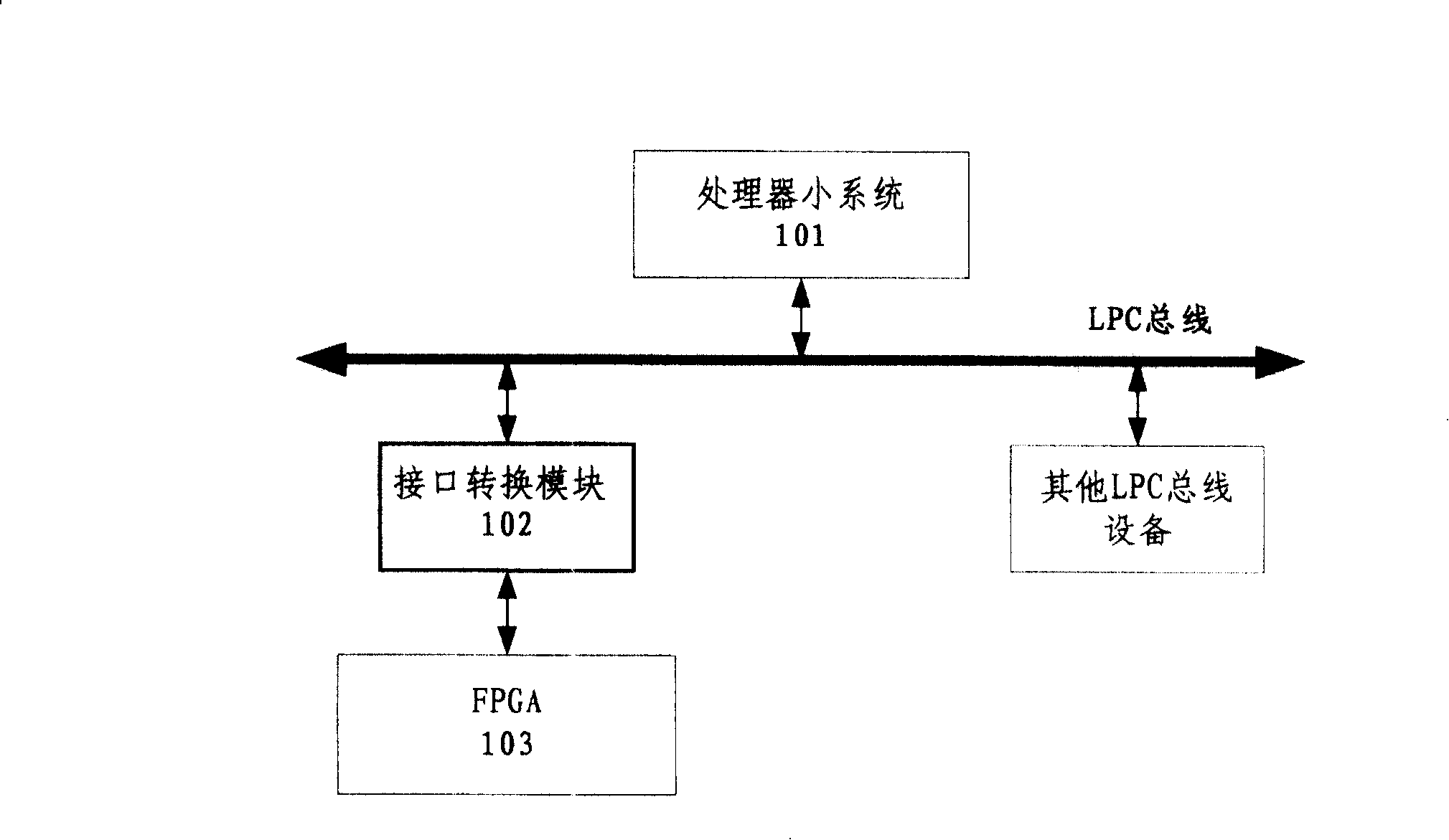

[0020] Such as figure 1 Shown, the structural block diagram of application environment system of the present invention, this system comprises:

[0021] The small processor system 101 may include a processor, a memory, a bridge chip, and a BIOS, etc., and is an independent processor system that can run programs, and can run an operating system and configuration programs in the present invention.

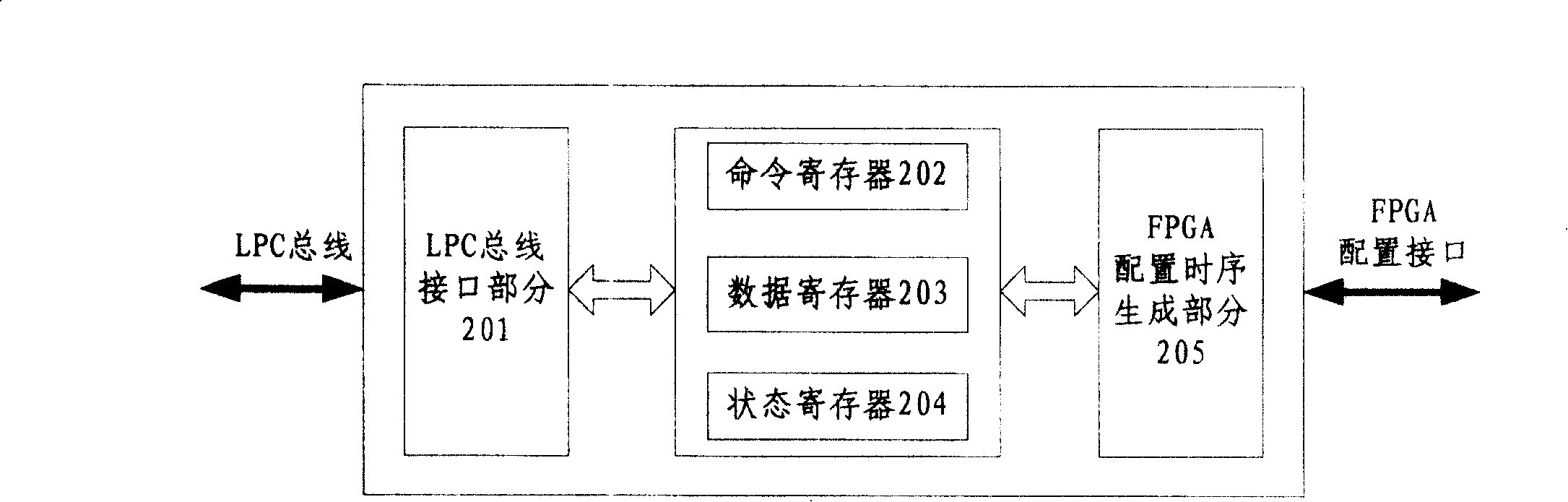

[0022] The interface conversion module 102, this module is hung on the LPC bus as an LPC bus device, and completes the timing conversion function from the LPC bus to the FPGA serial configuration, and the processor completes the online configuration of the FPGA through this module. The block diagram of the internal structure of the hardware module is as follows: figure 2 As shown, it mainly includes an LPC bus interface part 201, a register set (202-204) a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More