SIMD type parallel operation apparatus used for parallel operation of image signal

A technology for operating equipment and data, applied in the fields of electrical digital data processing, program control design, digital computer components, etc., and can solve problems such as complex programs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

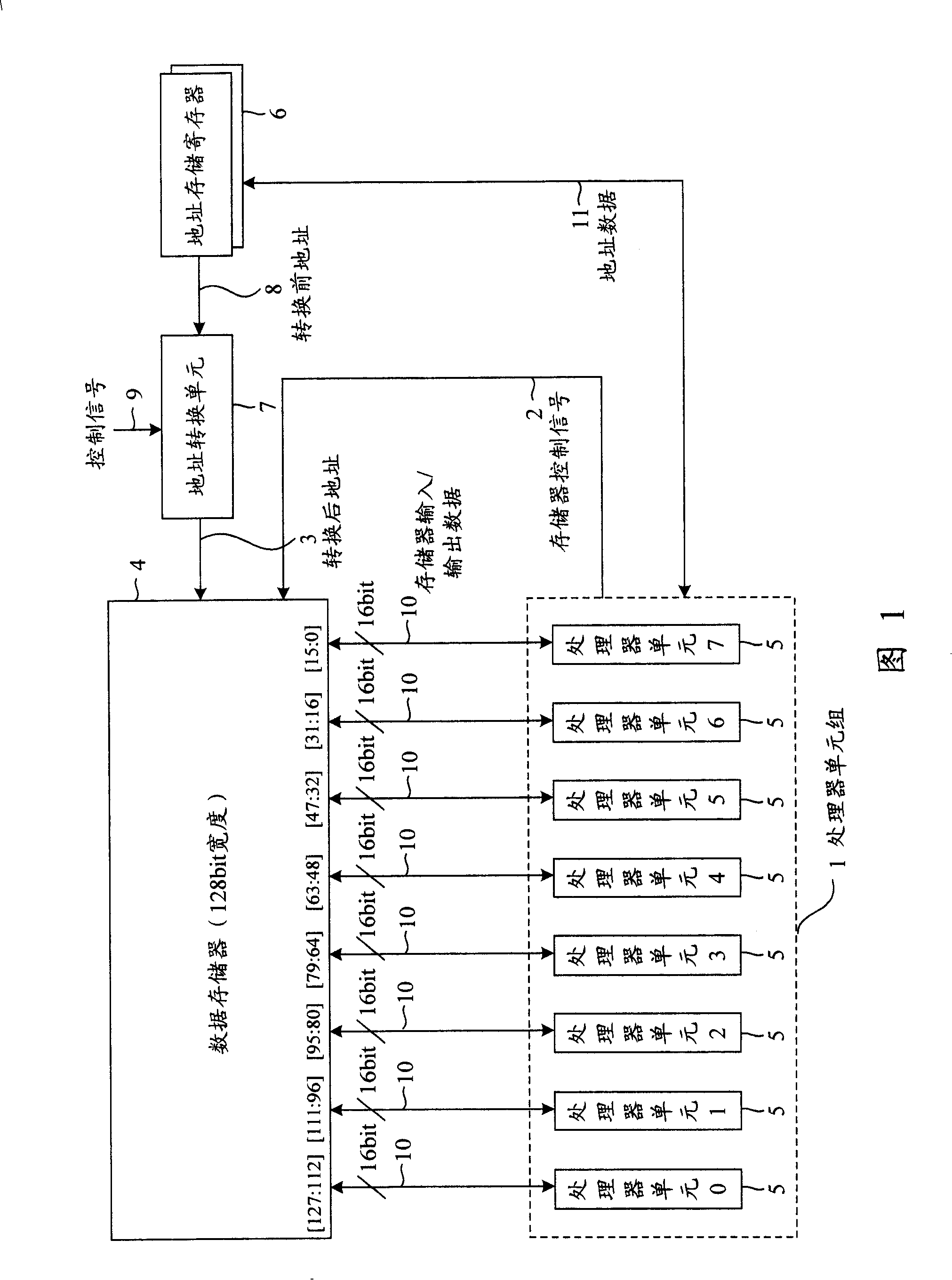

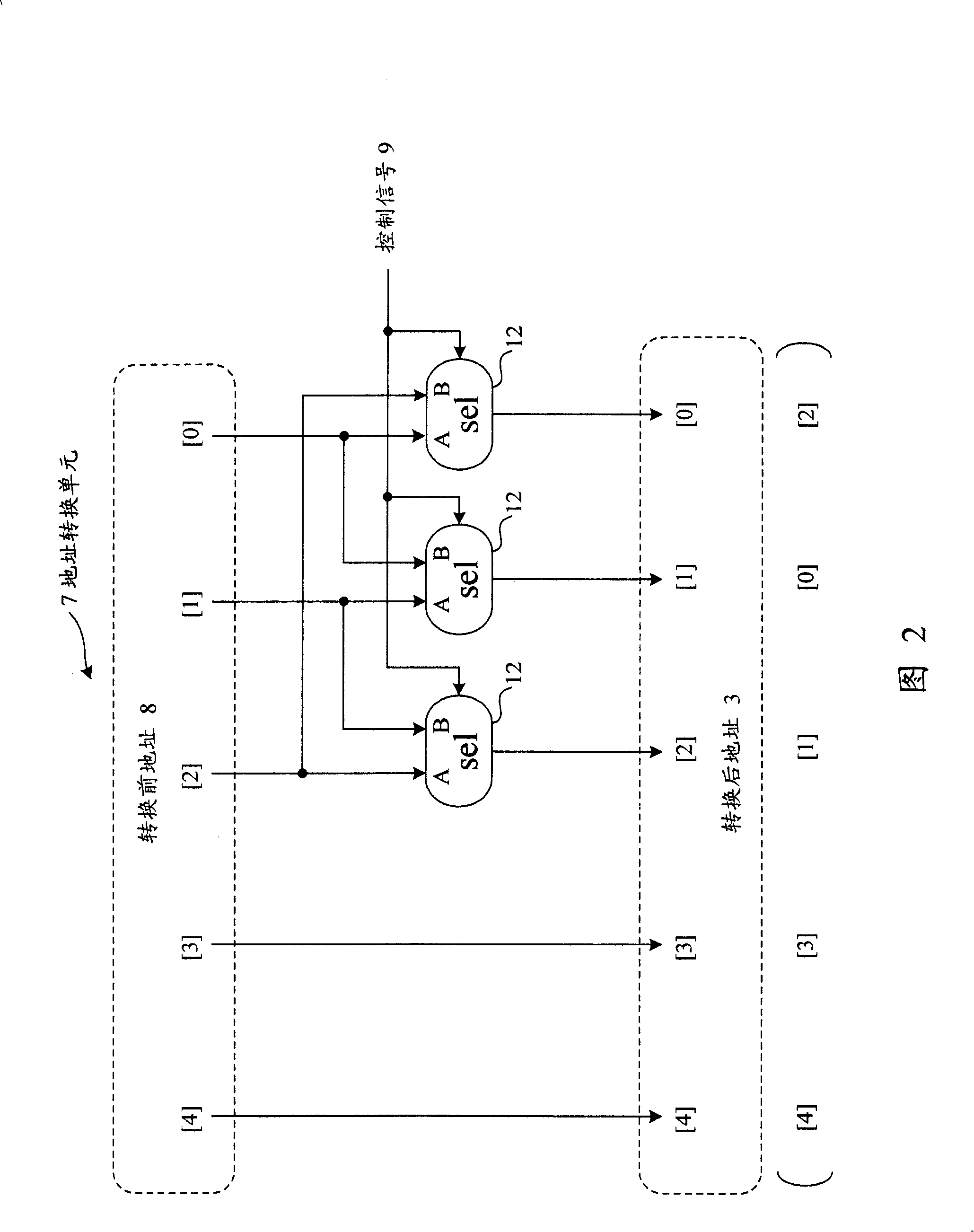

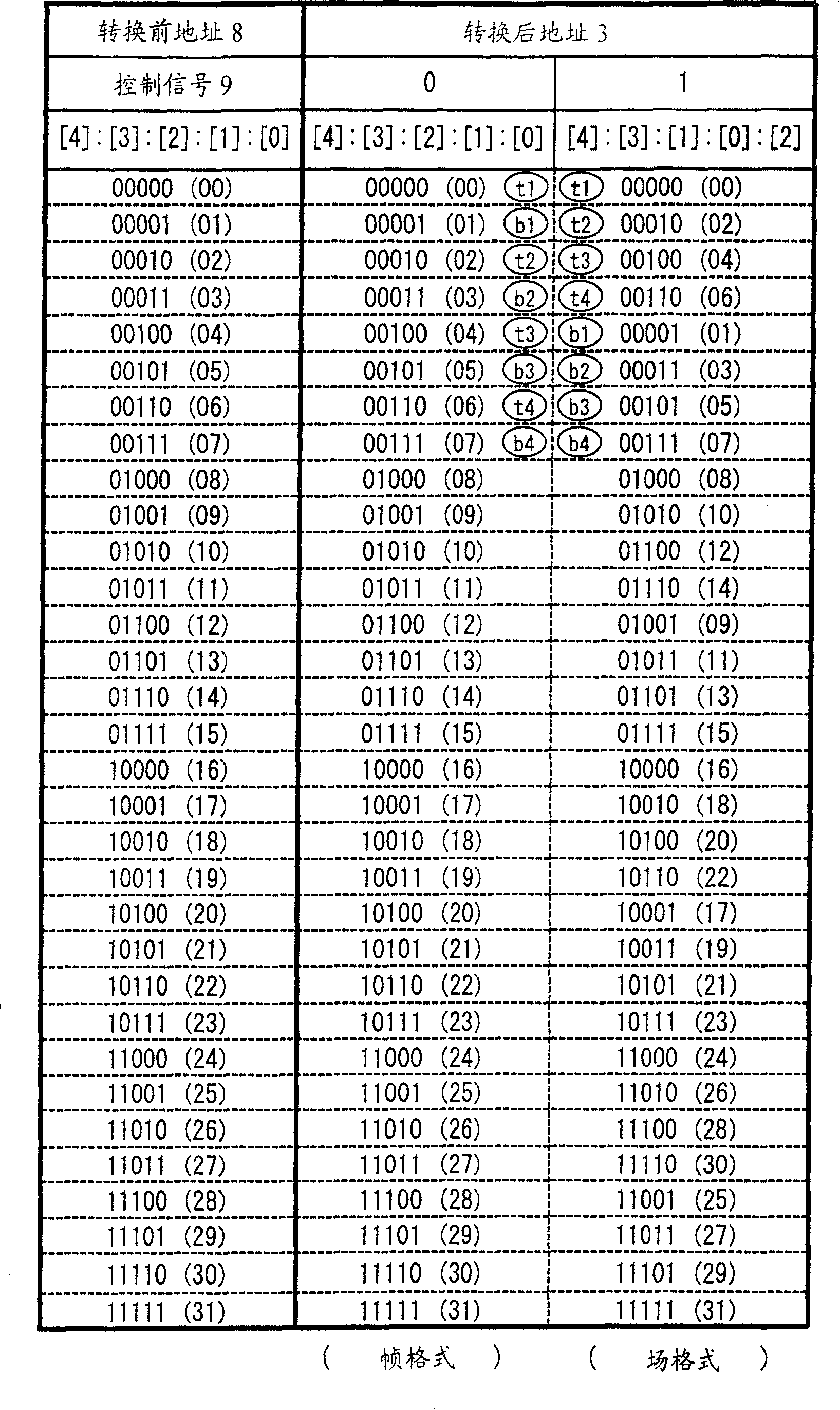

[0082] FIG. 1 illustrates the structure of a SIMD type parallel operation device according to Embodiment 1 of the present invention. Reference numeral 1 denotes a processor unit group utilizing a plurality of processor units 5 as an operation unit of SIMD type. The processor unit group 1 outputs a read request as a memory control signal 2 , whereby the data at the position indicated by the post-conversion address 3 at this time is read out from the data memory 4 . The processor unit group 1 also performs processing of outputting a write request as a memory control signal 2 , thereby writing the result at the position indicated by the converted address 3 at this time. In the SIMD type processor unit group 1, the respective processor units 5 simultaneously execute the same processing. More specifically, each processor unit 5 is constituted in such a manner that pixel values of an image signal of a horizontal period (equivalent to one line) are fetched to a memory circuit, the...

Embodiment 2

[0096] The structure of the SIMD type parallel operation device according to Embodiment 2 of the present invention is the same as that shown in FIG. 1 according to Embodiment 1 except for the structure of address conversion unit 7 . FIG. 5 illustrates the structure of the address conversion unit 7 according to Embodiment 2. As shown in FIG. Image 6 The operation of the address conversion unit 7 is shown.

[0097] Figure 7 A case is shown in which an image consisting of 8 horizontal pixels×8 vertical pixels and having 16 bits per pixel is set in the data memory 4 in a field format.

[0098] In the above case, it is assumed that sequential addresses are supplied to the address conversion register 6 and then Image 6 For the conversion operation shown in, control signal 9 is set to "1". With this operation, the sequential addresses are converted to the effective address sequence, and the read is performed using the converted address 3. Therefore, the image can be obtained i...

Embodiment 3

[0103] The structure of the SIMD type parallel operation device according to Embodiment 3 of the present invention is the same as that shown in FIG. 1 according to Embodiment 1 except for the structure of address conversion unit 7 . FIG. 8 illustrates the structure of the address conversion unit 7 according to Embodiment 3. As shown in FIG. Figure 9 The operation of the address conversion unit 7 is shown.

[0104] Figure 10 A case is shown in which an image consisting of 16 horizontal pixels×16 vertical pixels and having 16 bits per pixel is set in the data memory 4 in a frame format. Since one row of the image cannot be arranged in one row of the memory, the remainder of the image of the row is arranged in the next row of the memory. Fig. 11 shows the relationship between images and the arrangement of images in memory.

[0105] In the above case, it is assumed that sequential addresses are supplied to the address translation register 6 and then Figure 9 For the convers...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More