Chip algorithm simulating platform and method

An algorithm and platform technology, which is applied in the field of chip algorithm simulation platform, can solve problems such as slow execution speed, a large number of pseudo codes in hardware codes, and a large amount of resources occupied, so as to ensure correctness, easy to learn, and simple to achieve.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0055] In order to make the objectives, technical solutions, and advantages of the present invention clearer, the following further describes the present invention in detail with reference to the accompanying drawings and embodiments.

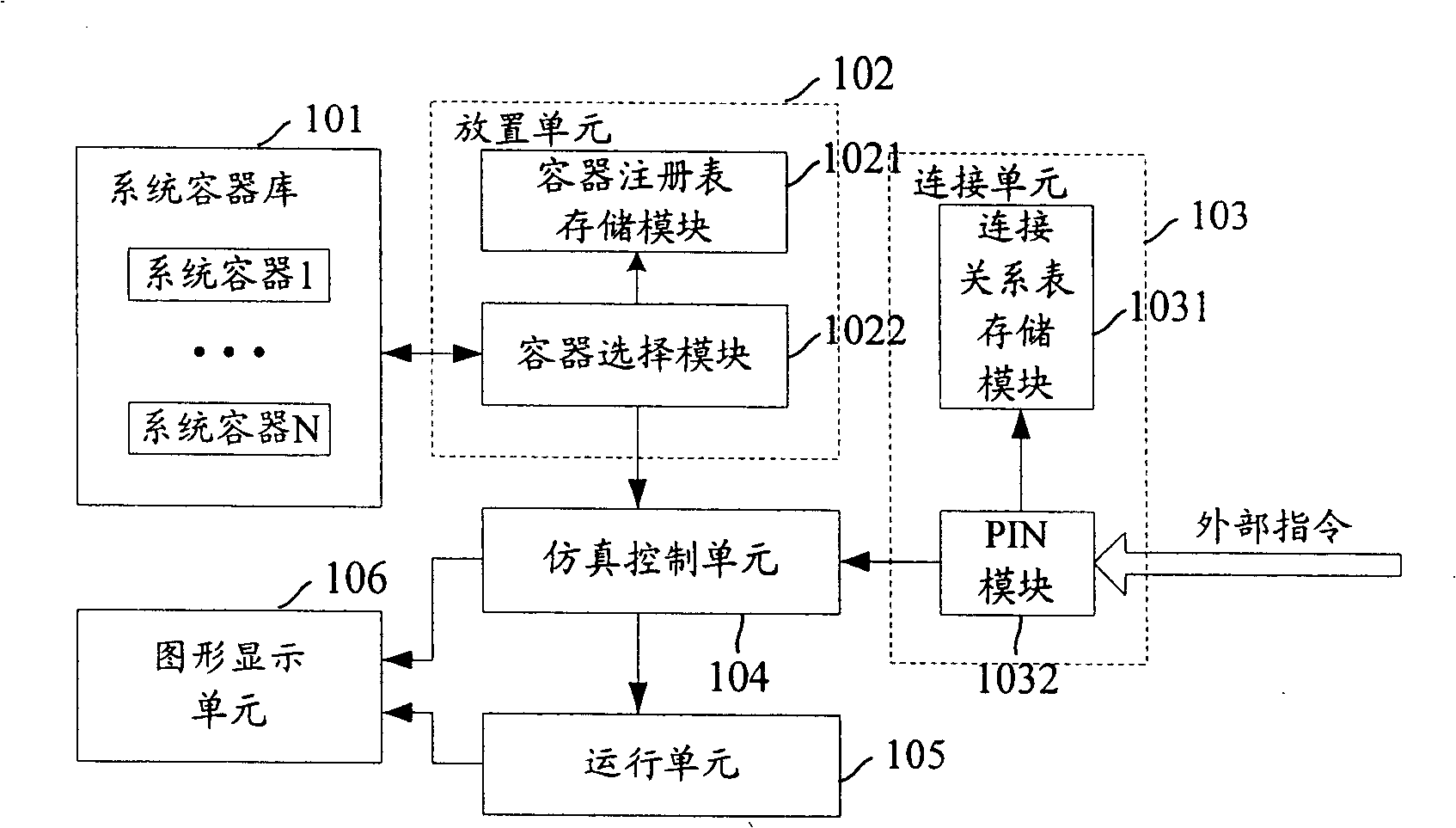

[0056] figure 1 Shown is the composition structure of the chip algorithm simulation platform of the present invention, including: a system container library 101, a placement unit 102, a connection unit 103, a simulation control unit 104, and an operation unit 105.

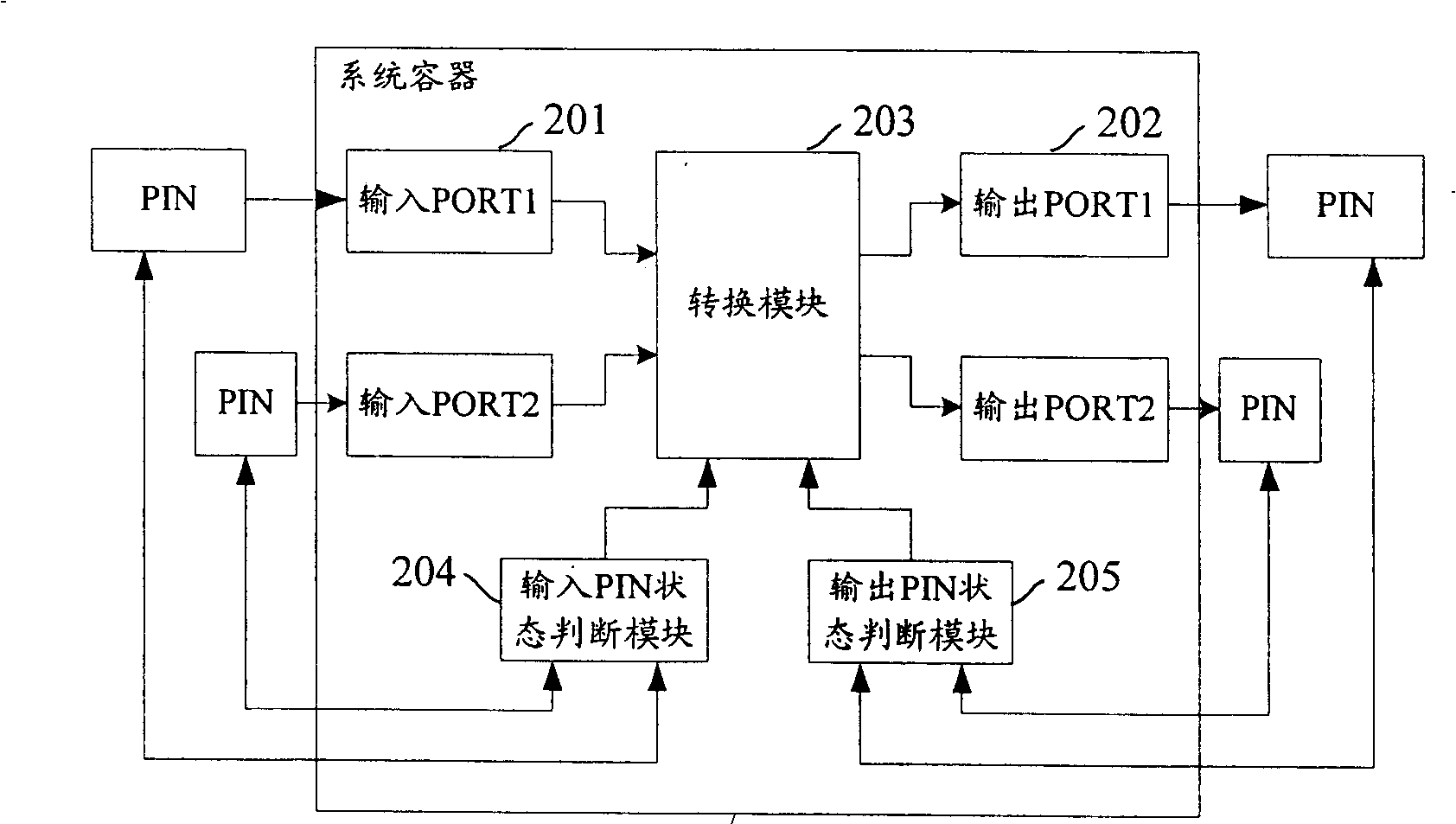

[0057] The system container library 101 stores one or more system containers in advance, and each system container is provided with a unique container number. The system container is used to implement a predetermined algorithm, and is designed in compliance with the actual hardware usage habits. For example, each system container is set with input and / or output ports (Port) as required, and the function division between system containers is also different from the actual The hardware ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More