Method of manufacturing NAND flash memory device

A memory device and flash technology, applied in the field of NAND flash memory devices, can solve problems such as unit coupling rate and programming speed drop

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

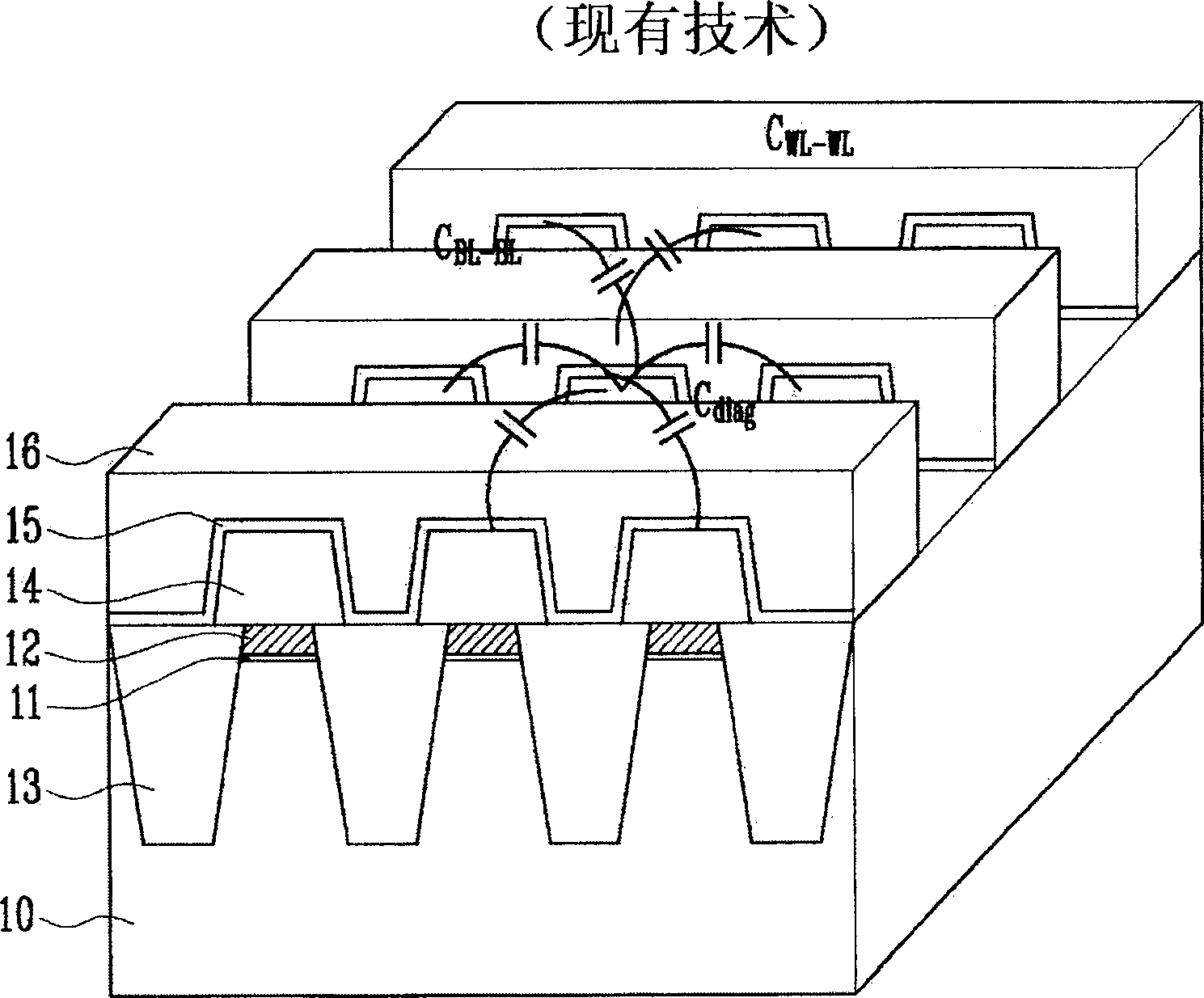

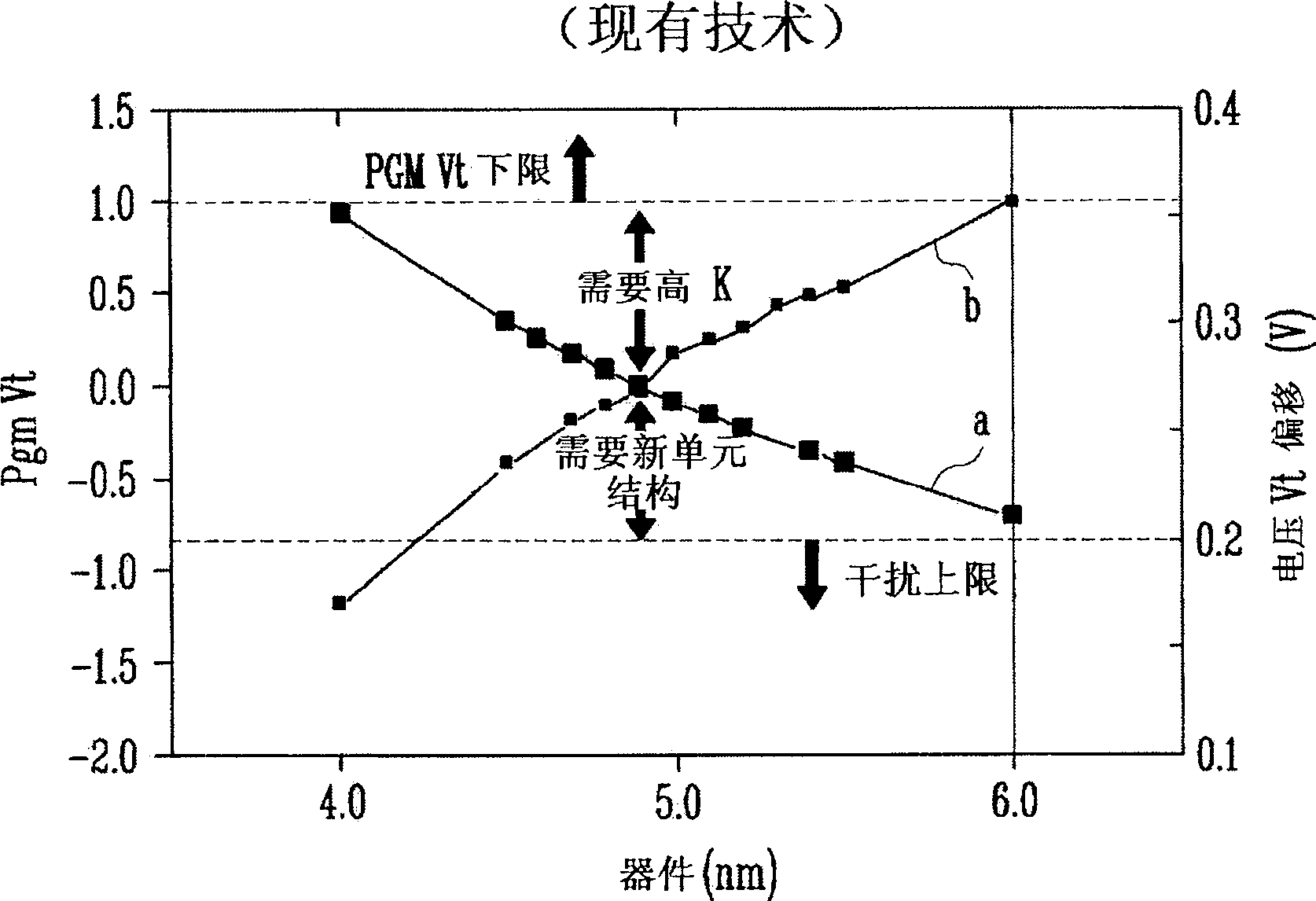

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] Specific embodiments according to the present invention are described below with reference to the drawings.

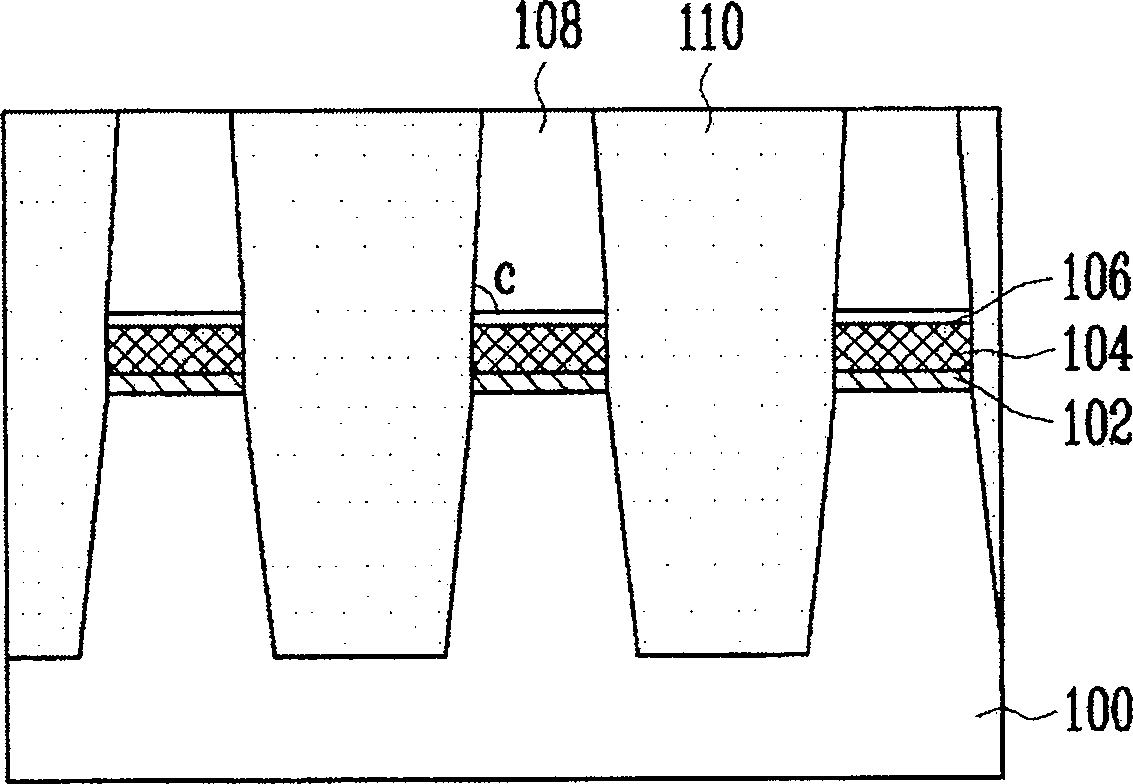

[0017] Figures 3A-3F is a cross-sectional view illustrating a method of manufacturing a NAND flash memory device according to an embodiment of the present invention. FIG. 3 shows a self-aligned shallow trench isolation (SA-STI) structure applying a self-aligned floating gate (SA-FG) scheme. refer to Figure 3A A channel oxide layer 102 , a first polysilicon layer 104 for a floating gate, a buffer oxide layer 106 and a nitride layer 108 are sequentially formed on a semiconductor substrate 100 . The first polysilicon layer 104 is preferably formed 300 -500 The thickness of the buffer oxide layer 106 is preferably formed 30 -80 thickness, the nitride layer 108 is preferably formed 600 -1200 thickness of.

[0018] Portions of the nitride layer 108, the buffer oxide layer 106, the first polysilicon layer 104, the channel oxide layer 102, and the semic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More