X87 structural microprocessor

A technology of microprocessor and architecture, applied in the direction of electrical digital data processing, digital data processing parts, data processing according to predetermined rules, etc., can solve the problems that do not include floating-point fusion multiplication and addition instructions, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

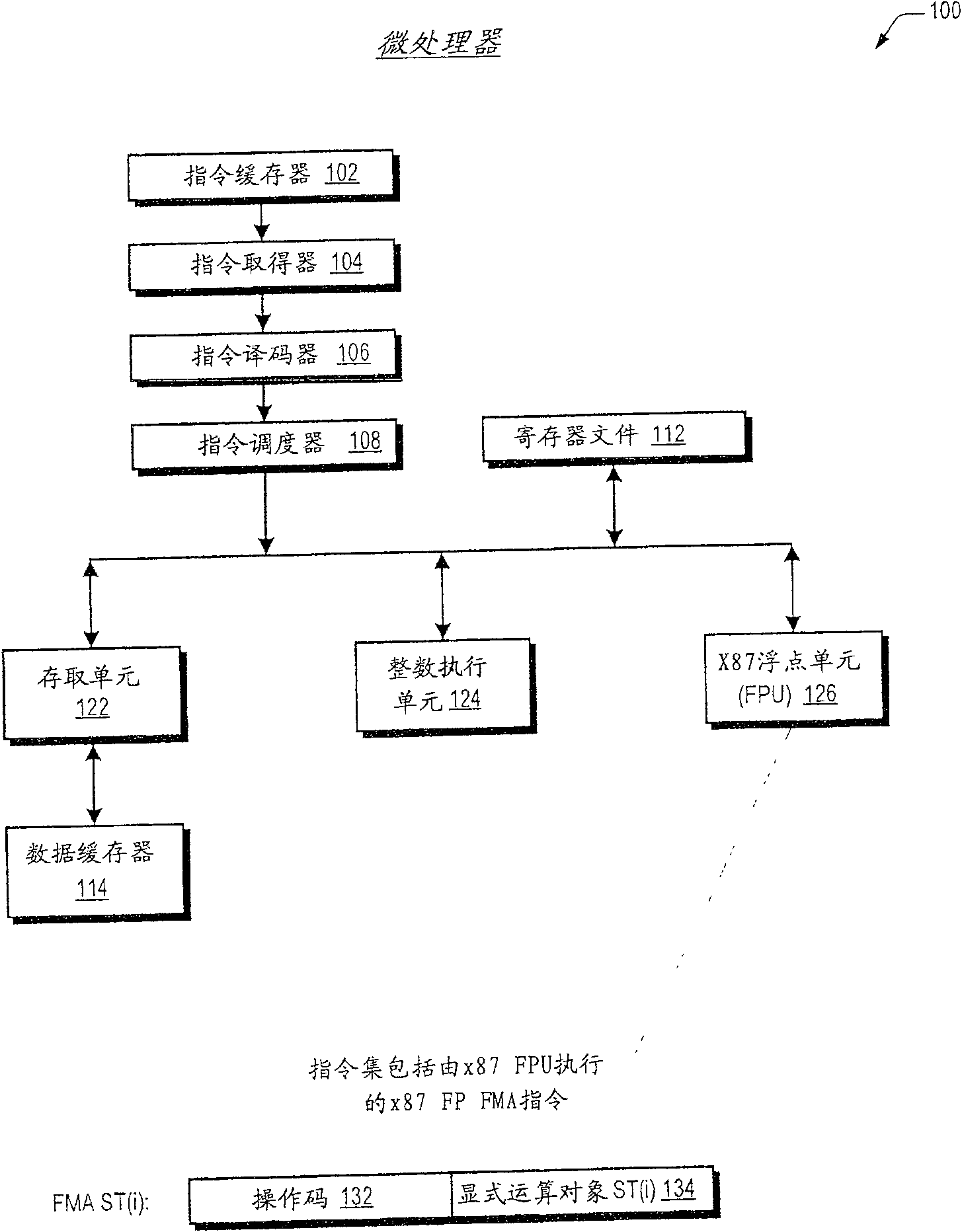

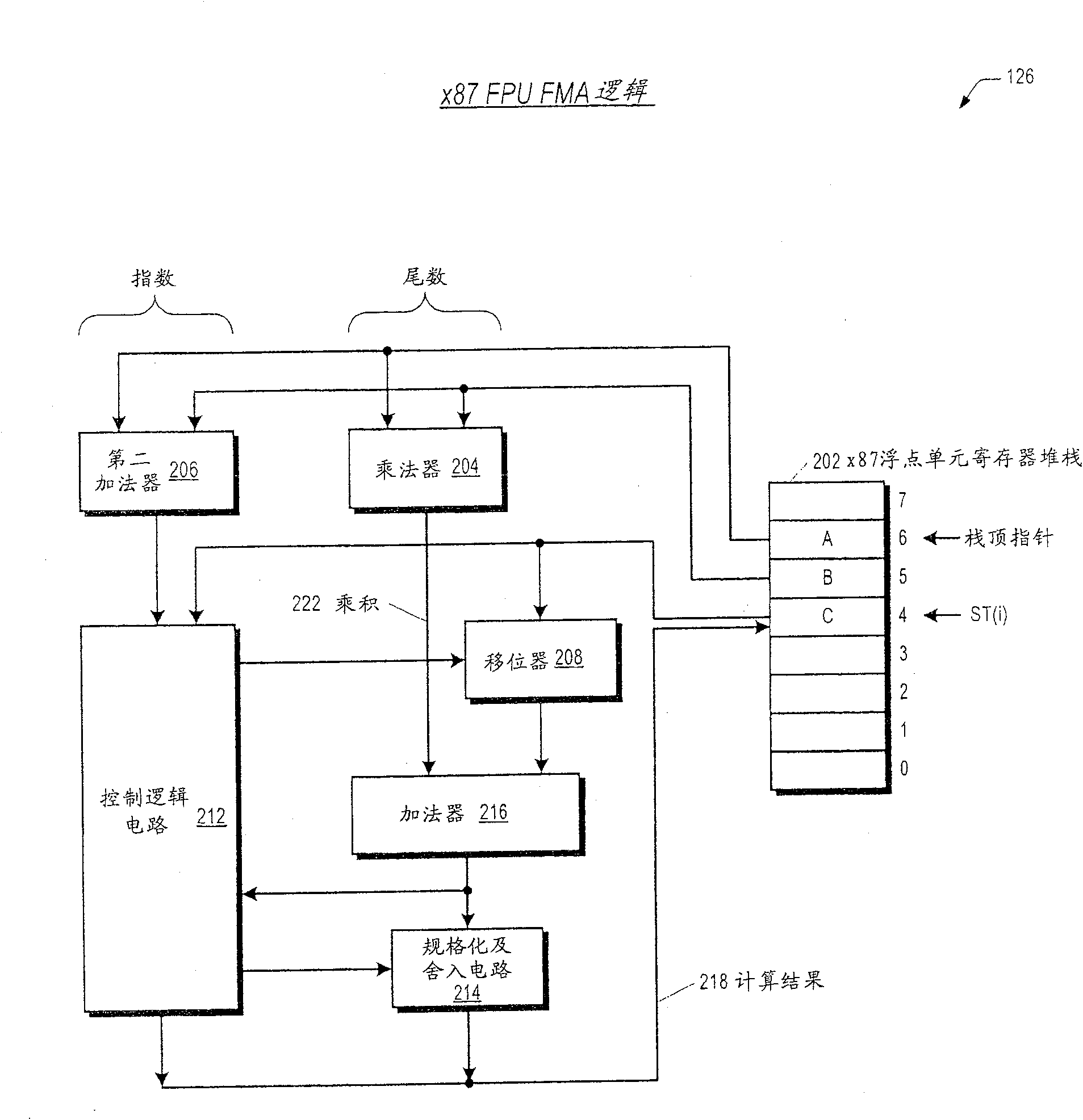

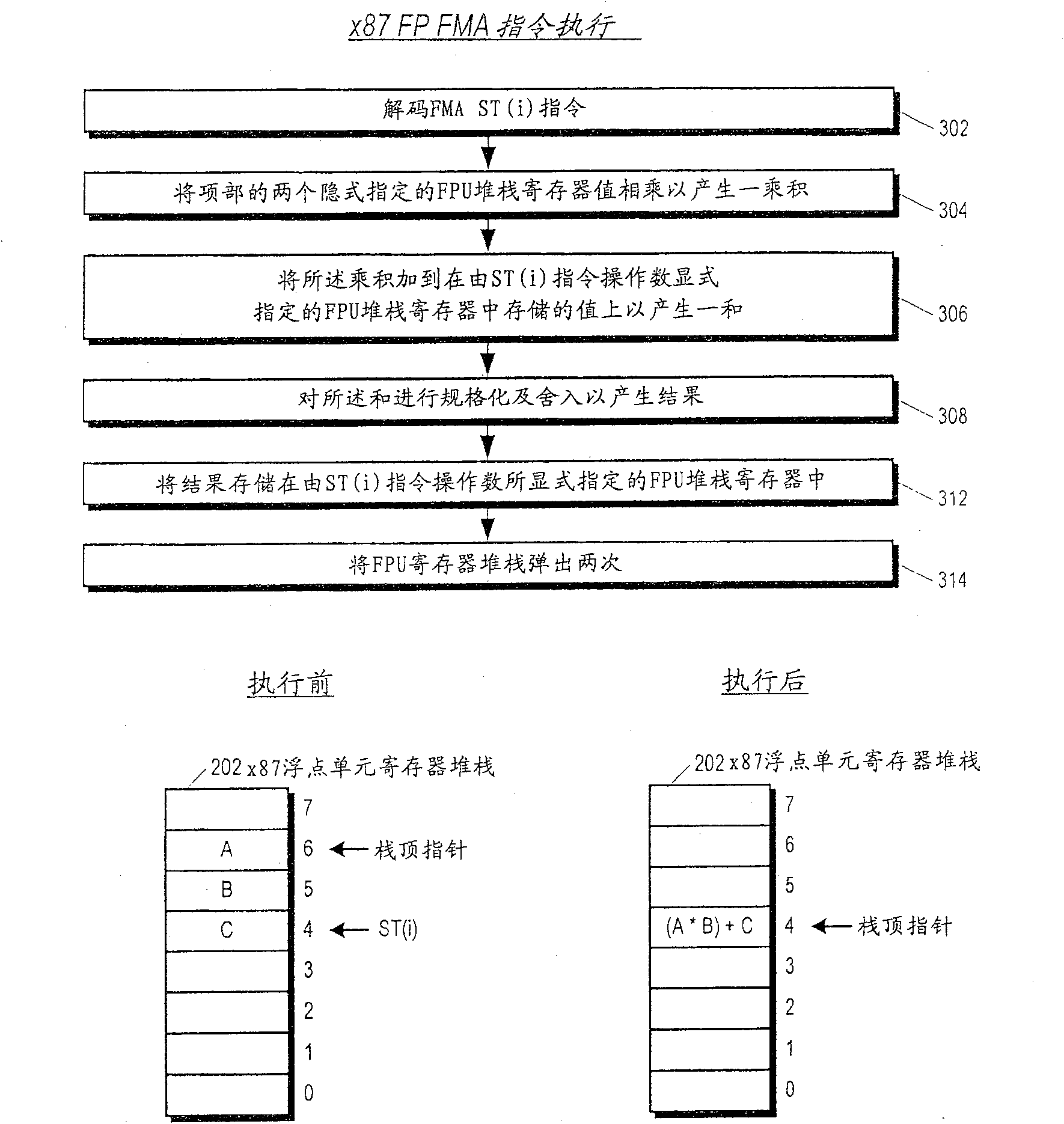

[0019] refer to figure 1 , the structural block diagram shows a microprocessor 100 of X86 architecture whose instruction set includes X87 Fused Multiply-Add (FMA) instruction. The microprocessor 100 includes an instruction register 102, which caches program instructions fetched from a system memory coupled to the microprocessor 100. According to the present invention, the program instructions include X87 fused multiply-add instructions. The microprocessor 100 further includes an instruction fetcher 104 coupled to the instruction register 102 for fetching program instructions from the instruction register 102 and the system memory. The microprocessor 100 also includes an instruction decoder 106, coupled to the instruction fetcher 104, which decodes the obtained program code of the instruction set of the microprocessor 100, such as the X87 fusion multiply-add instruction described in the present invention. . The instruction scheduler 108 is coupled to the instruction decoder 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More