Memory and method for refreshing memory array

A memory array and memory technology, applied in static memory, digital memory information, information storage, etc., can solve the problems of high refresh rate and high power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

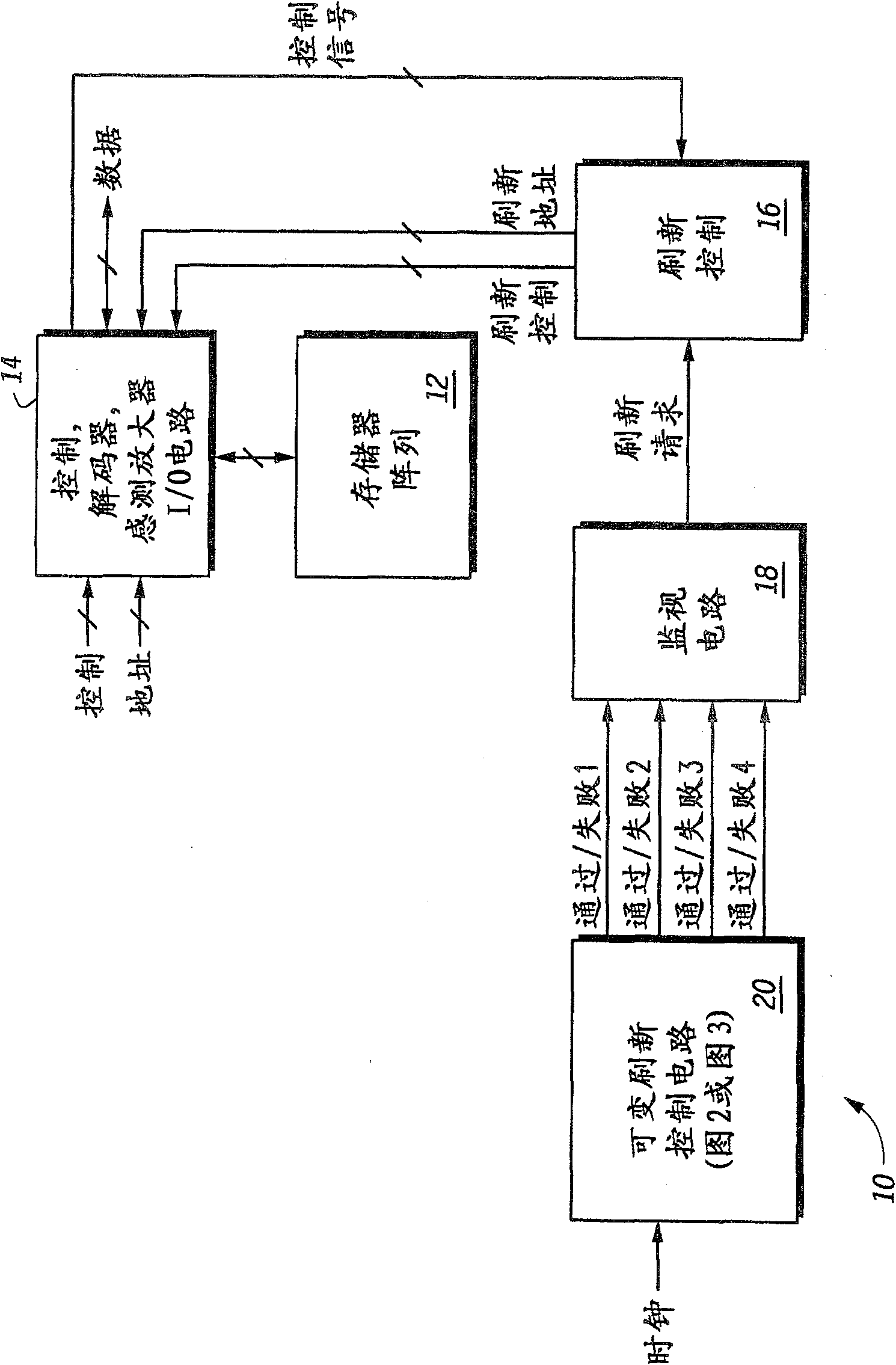

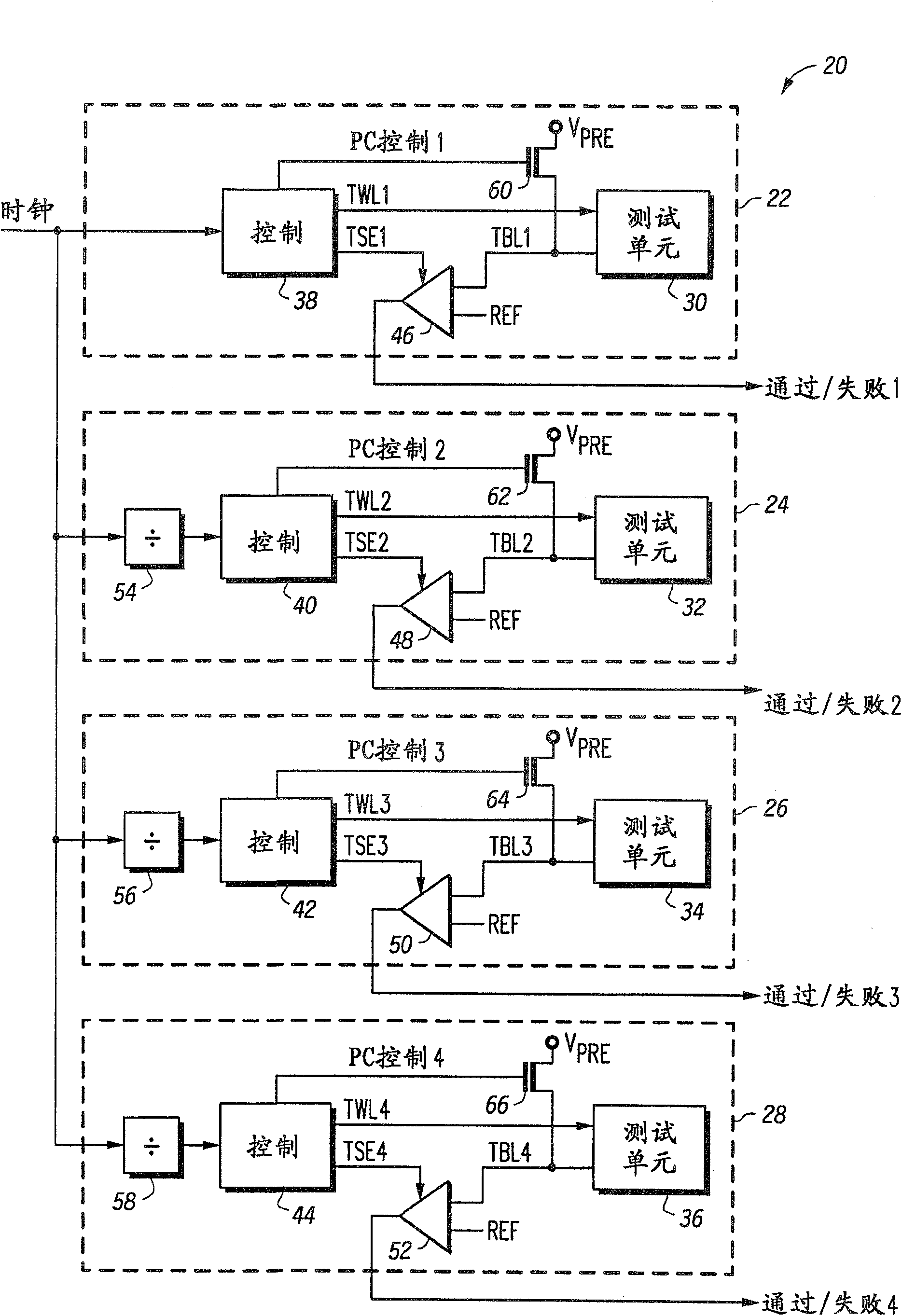

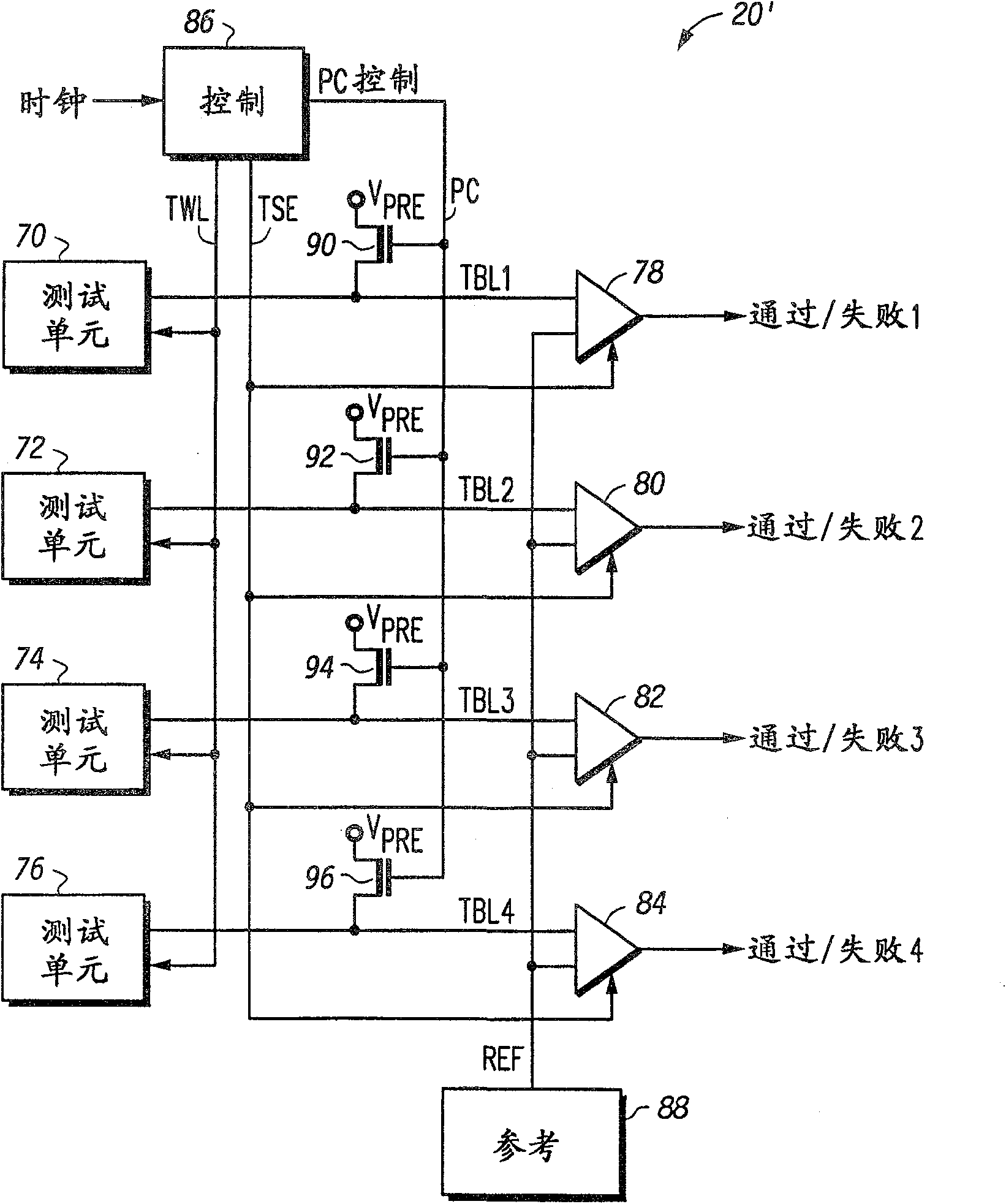

[0014] In general, the present invention provides a memory with a variable refresh control circuit that includes a plurality of test memory cells in order to determine an optimal refresh speed for the memory that gives reliable performance and lower power consumption. A variable refresh control circuit includes a plurality of test memory cells. In one embodiment, each of the plurality of substantially identical test memory cells includes a capacitance for storing a charge representing a stored logic state, and each of the plurality of test memory cells is connected to the other test memory cells Refresh at different speeds. A monitoring circuit is provided for monitoring a stored logic state of each of the plurality of test memory cells, and in response, a refresh rate of the plurality of memory cells is adjusted.

[0015] In another embodiment of the present invention, the variable refresh control circuit includes a plurality of test memory cells, wherein each of said test m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More