Chip package structure and manufacturing method thereof

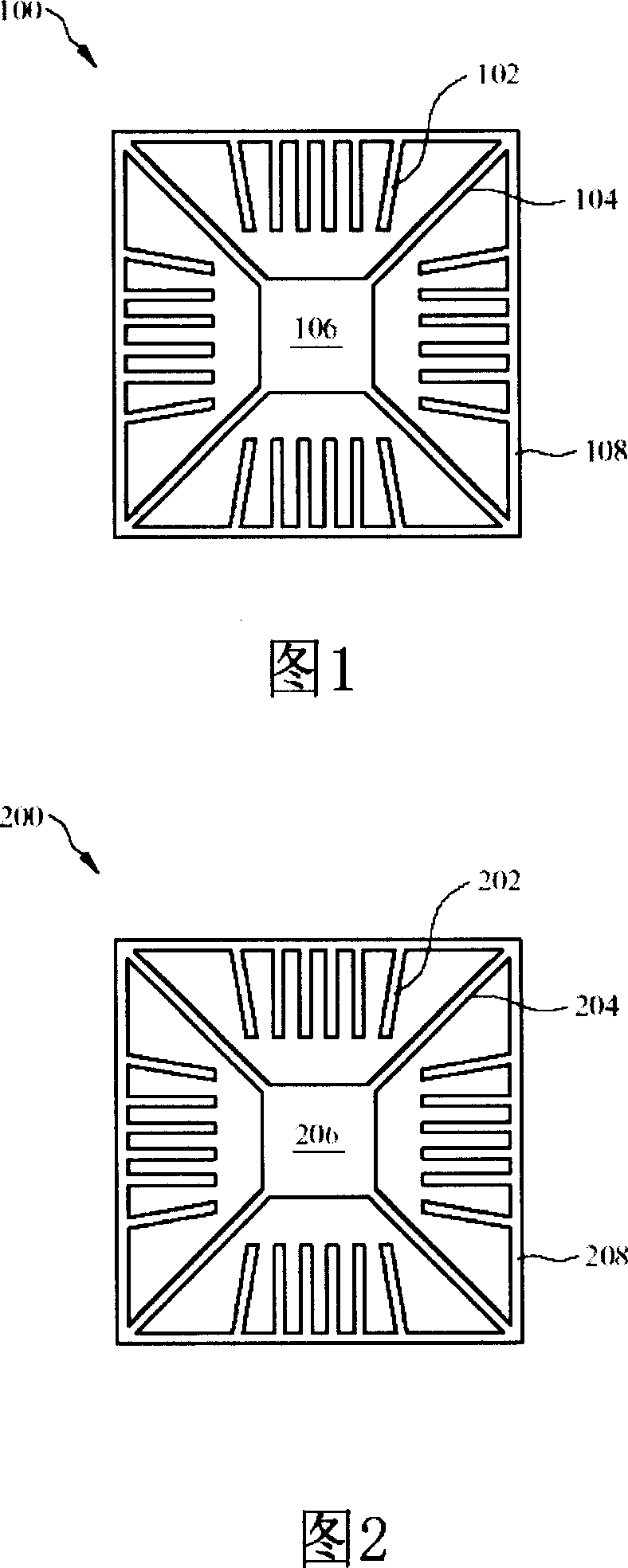

A technology of chip packaging and manufacturing methods, applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problems of occupying space, space waste of the lead frame 100, and design restrictions of the lead frame 100, and achieve effective utilization , to avoid restrictive effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] Relevant detailed description and technical contents of the present invention are as follows now in conjunction with the accompanying drawings:

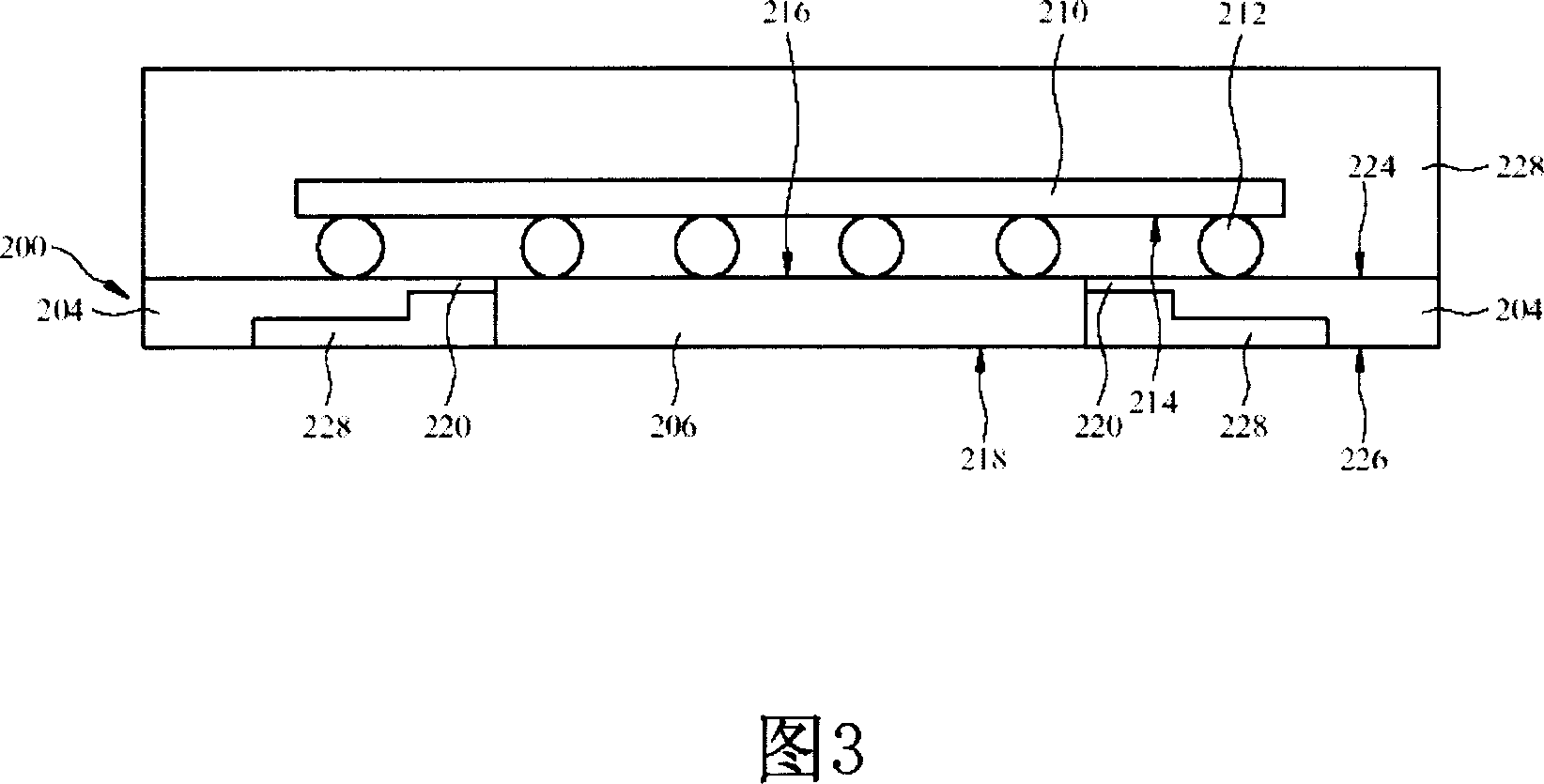

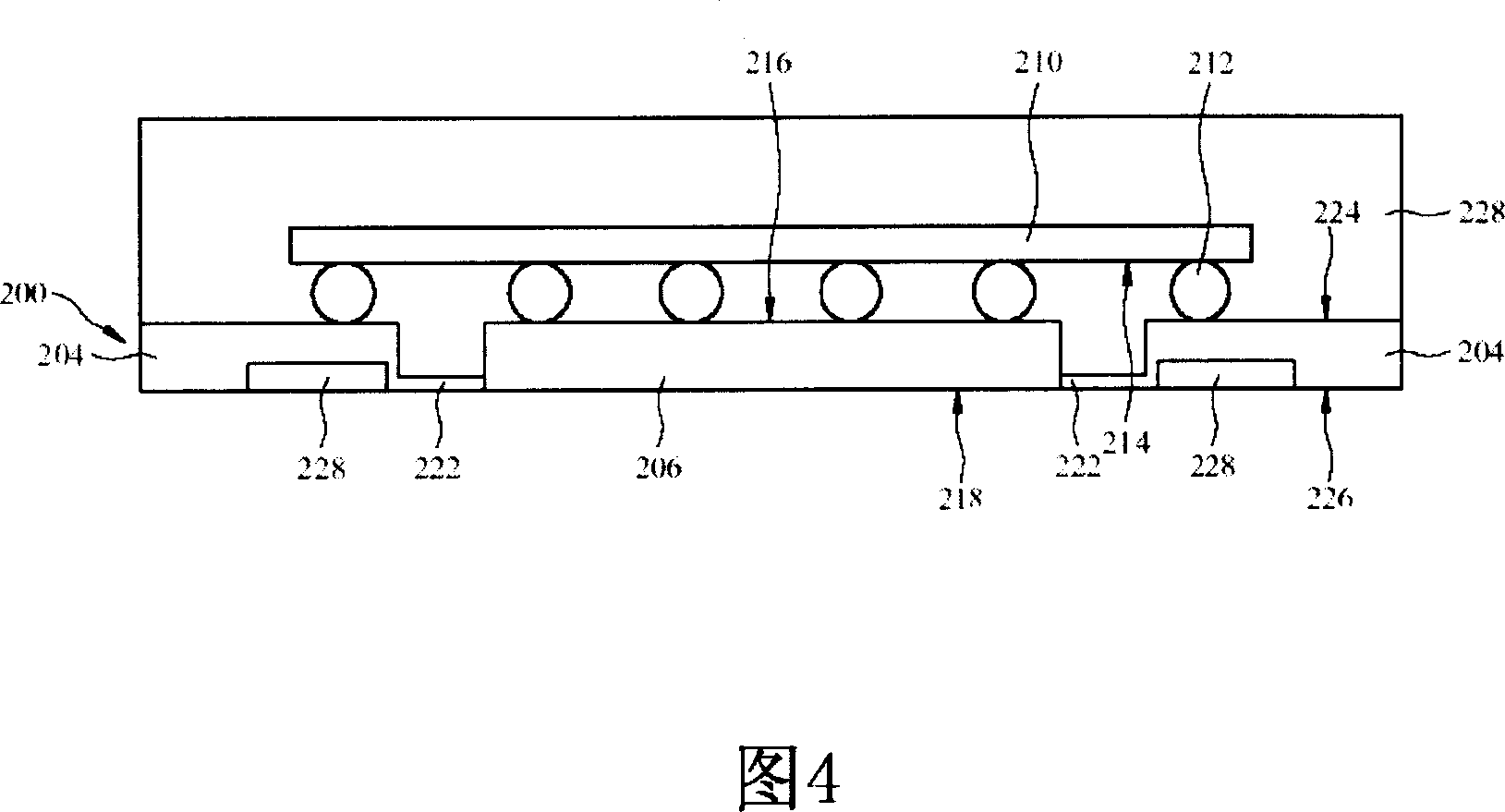

[0018] The invention discloses a chip package structure and a manufacturing method thereof. The chip package structure is a four-sided flat package structure without leads. In order to make the description of the present invention more detailed and complete, reference may be made to the following description together with the illustrations in FIGS. 2 to 4 .

[0019] Please refer to FIGS. 2 to 4 , wherein FIG. 2 is a top view of a lead frame according to a preferred embodiment of the present invention, and FIGS. 3 and 4 are two different chip packaging structures according to a preferred embodiment of the present invention. sectional view. The chip packaging structure of the present invention has a carrier, such as a lead frame 200 , whose main function is to carry a chip 210 , as shown in FIGS. 3 and 4 . In the chip packagin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More