Implementation method for in-Turbo code interweaver

An implementation method and interleaver technology, applied in the field of channel codecs, can solve problems such as waste of hardware resources, excessive hardware resources, and a large number of ROMs, and achieve the effect of simplifying implementation steps and saving storage resources.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The technical solutions of the present invention will be further described below in conjunction with the accompanying drawings and through specific implementation methods.

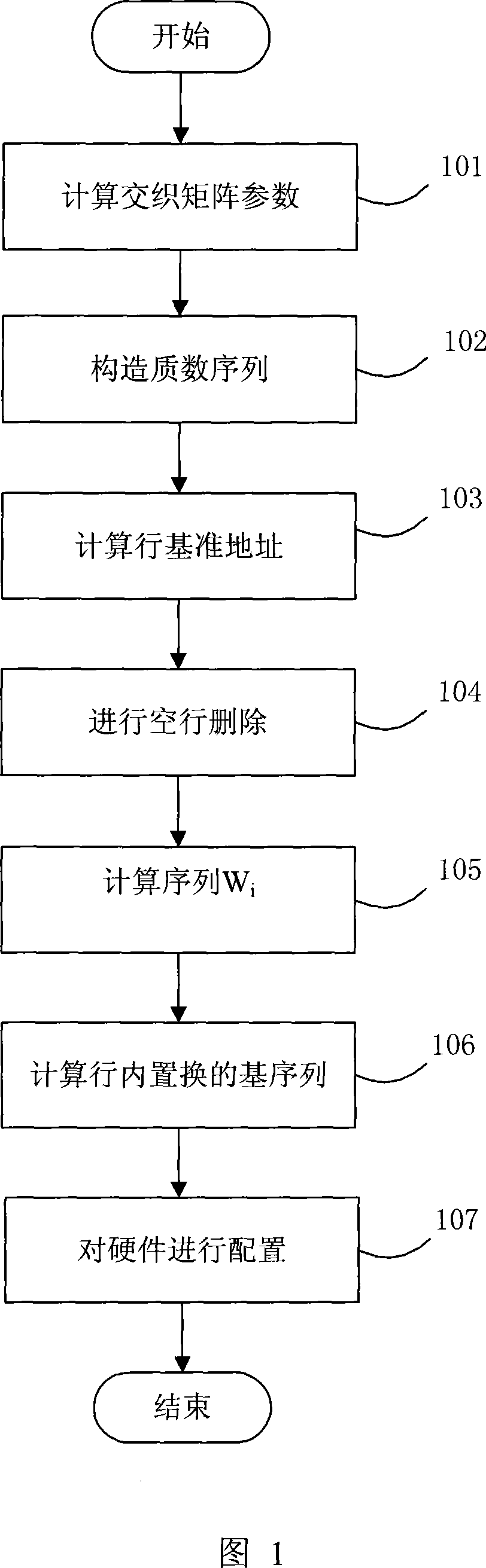

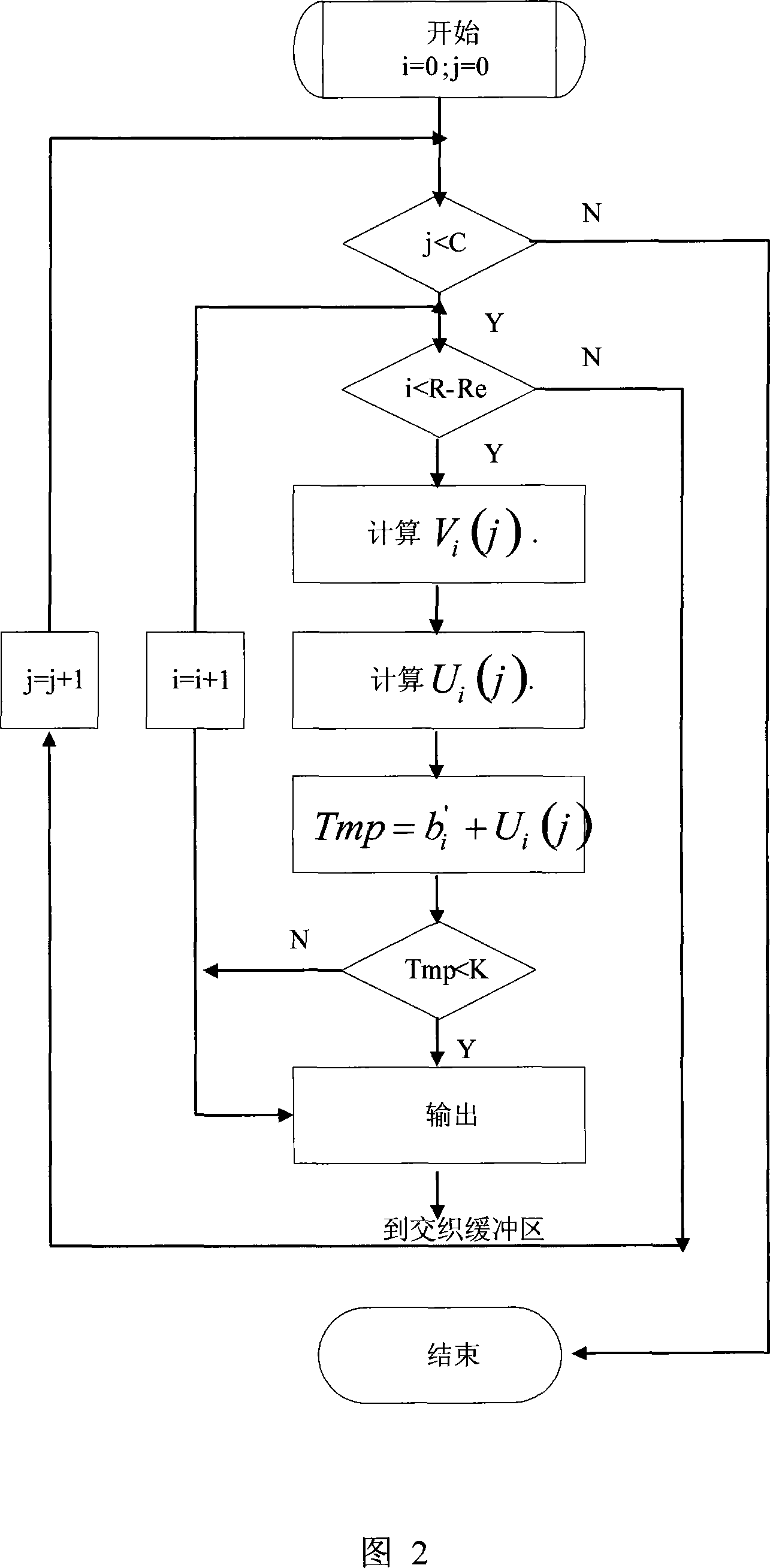

[0045] The present invention adopts the realization method that combines software and hardware, under the situation of using less resources, generates interleaving or deinterleaving address in real time, and its core idea is to divide the code interleaver with length between 40-5114 bits at first into A number of mother interleavers with different lengths are used to construct corresponding sub-interleavers through blank line pre-deletion technology, and on this basis, a turbo code internal interleaver with a given length is realized by deleting redundant half-line blanks. The interleaving and deinterleaving method in Turbo code of the present invention, its implementation device is divided into two parts of software and hardware, the software mainly realizes the calculation of one-time initializatio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More