A double-fin channel wrap gate field-effect transistor and its manufacture method

A field effect transistor, double fin technology, applied in the field of metal oxide semiconductor field effect transistors, can solve the problems of reduced device switching speed, limited effective channel width, increased gate capacitance, etc., so as to improve device switching speed, device Switching speed advantage, effect of reducing parasitic gate capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

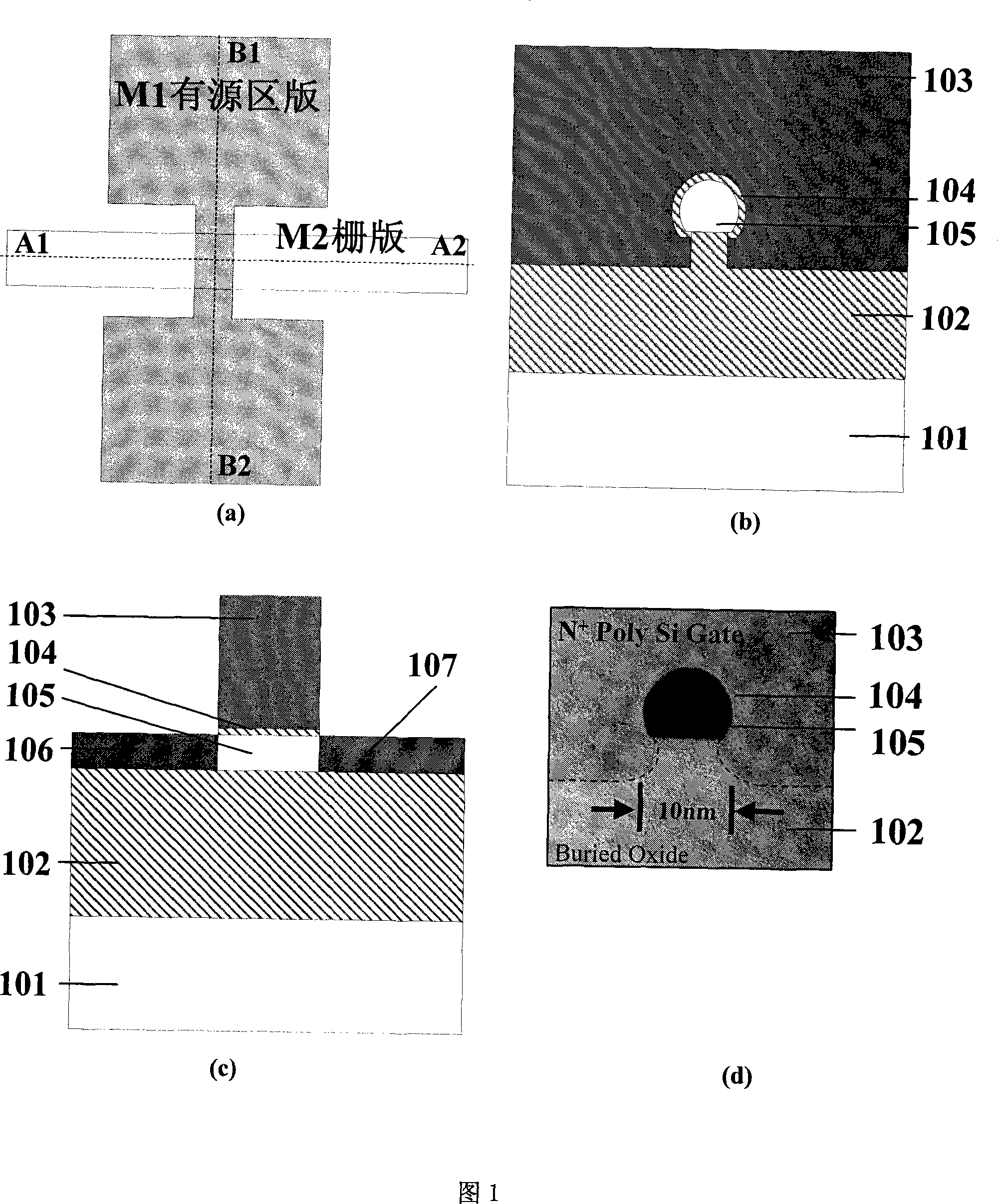

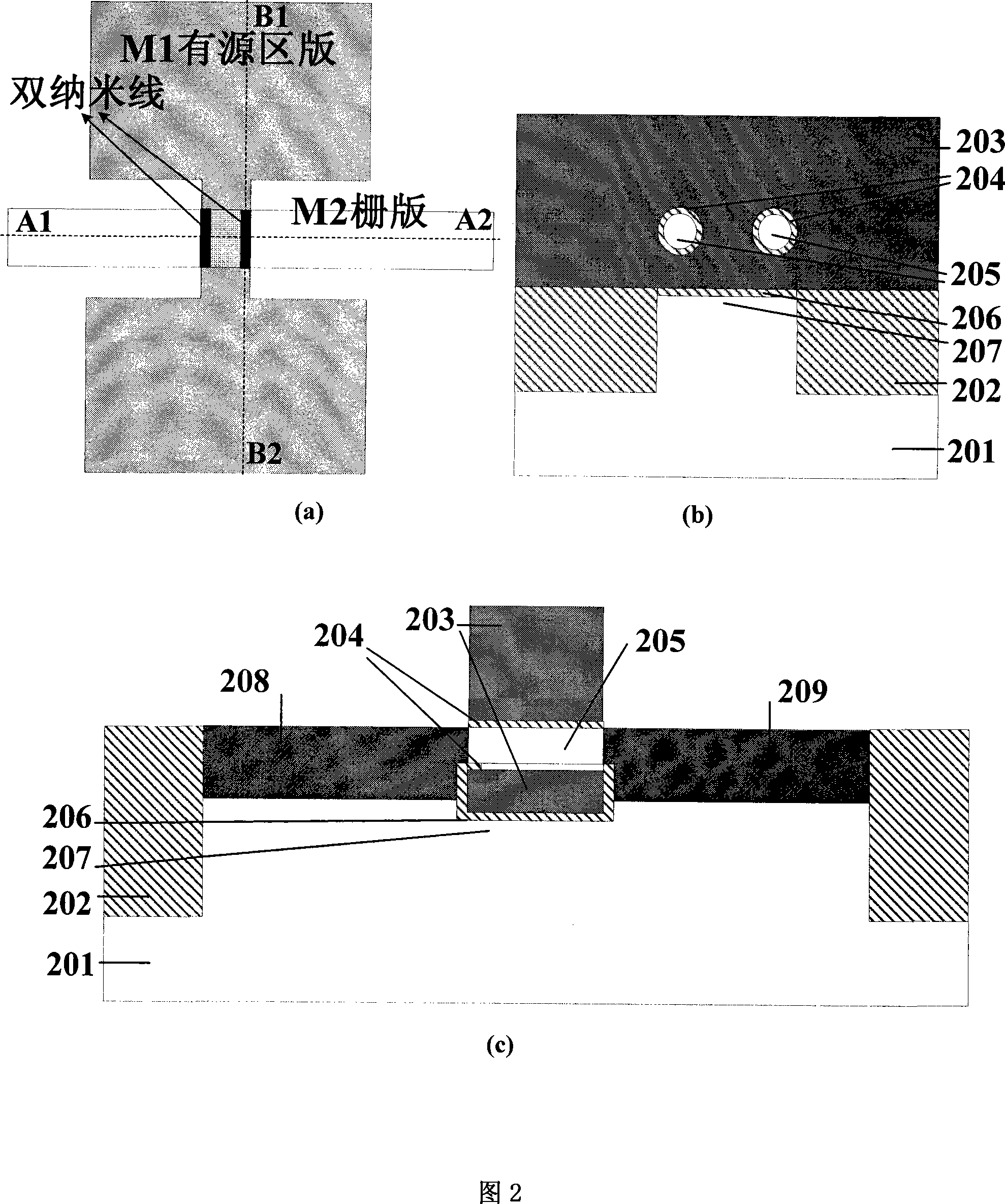

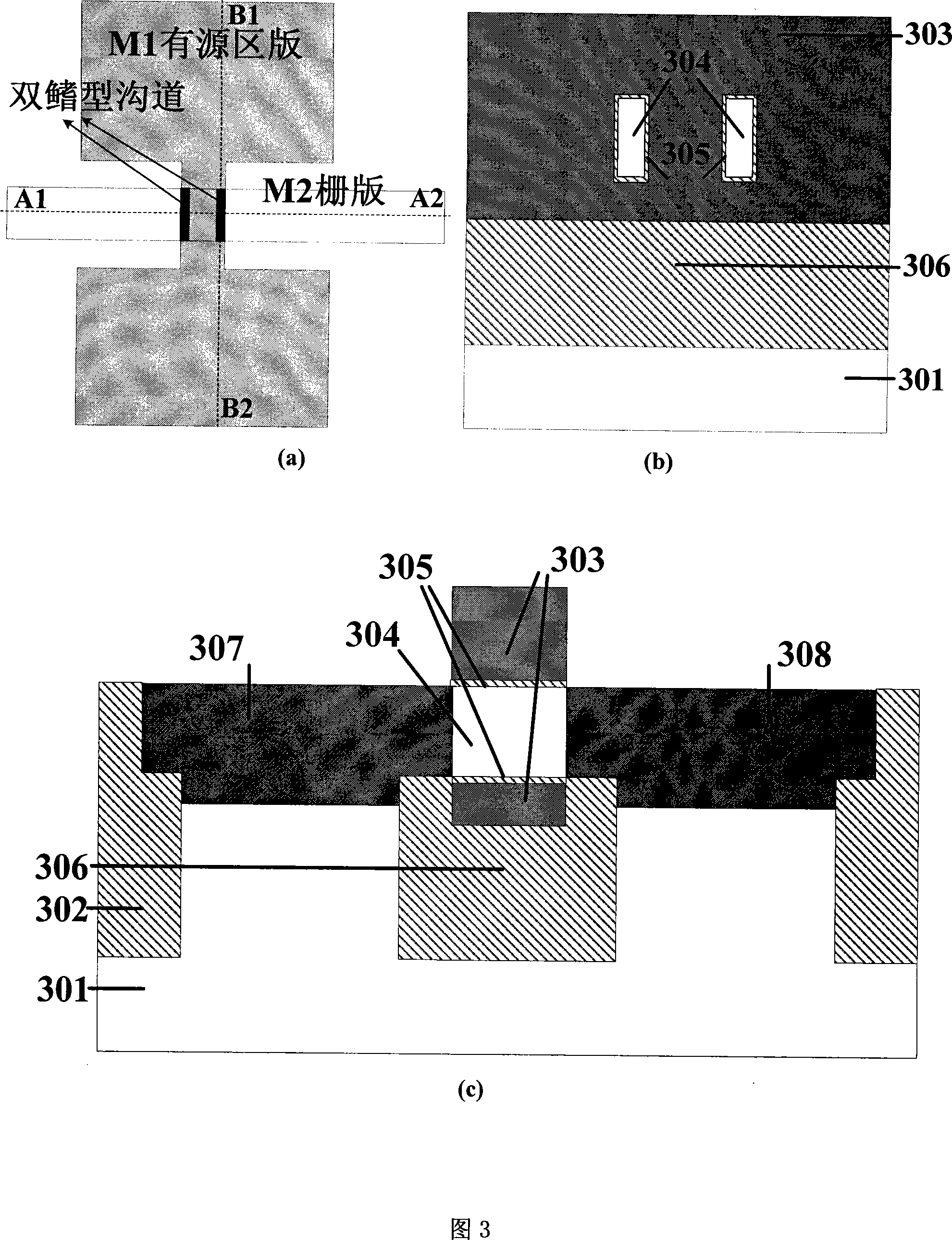

[0060] The double-fin trench-around-gate field effect transistor provided by the present invention and its manufacturing method will be described in detail below in conjunction with the accompanying drawings, but this does not constitute a limitation to the present invention.

[0061] As shown in FIG. 3 , it is a double-fin channel-around-gate device of this embodiment. The device is based on a bulk silicon substrate. From the cross-sectional structure along the vertical direction of the channel, the channel is two identical rectangular fins (Twin Fin), that is, a double-fin channel with a width ≤ 10nm and a height of 30-50nm. The channel width can reach 160-240nm; the double-fin channel is surrounded by gate oxide (Gate Oxide), and then by the gate (Gate), forming a gate-enclosed device; directly below the double-fin channel and between the substrate , there is a silicon dioxide insulating layer with a thickness of 150-250nm, forming a structure (Body-on-Insulator, BOI struc...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width w | aaaaa | aaaaa |

| Height | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap