Method and circuit for sampling data

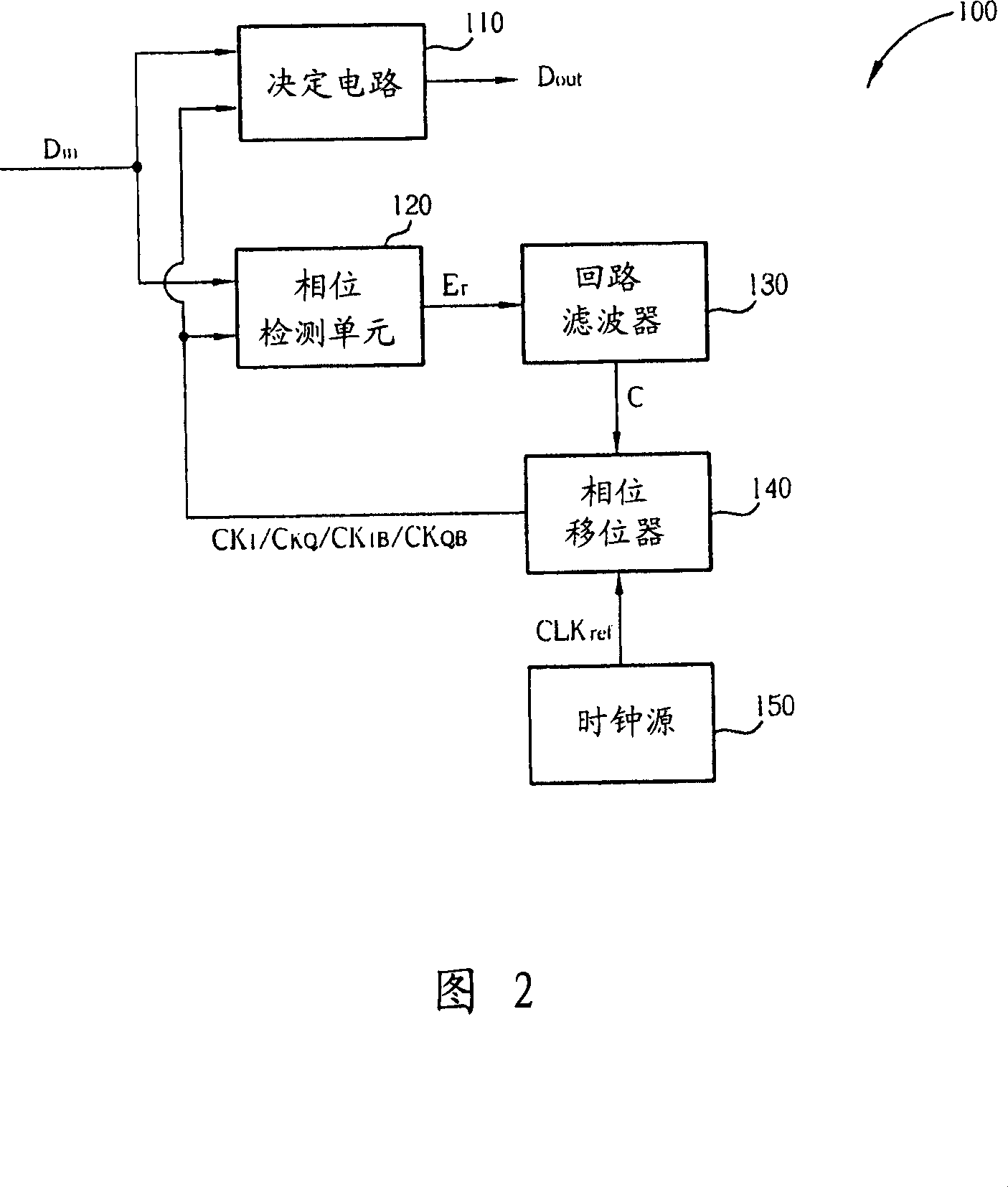

A data and circuit technology, applied in the field of data recovery circuits, can solve the problems of increasing the design difficulty of clock and data recovery circuits 100

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

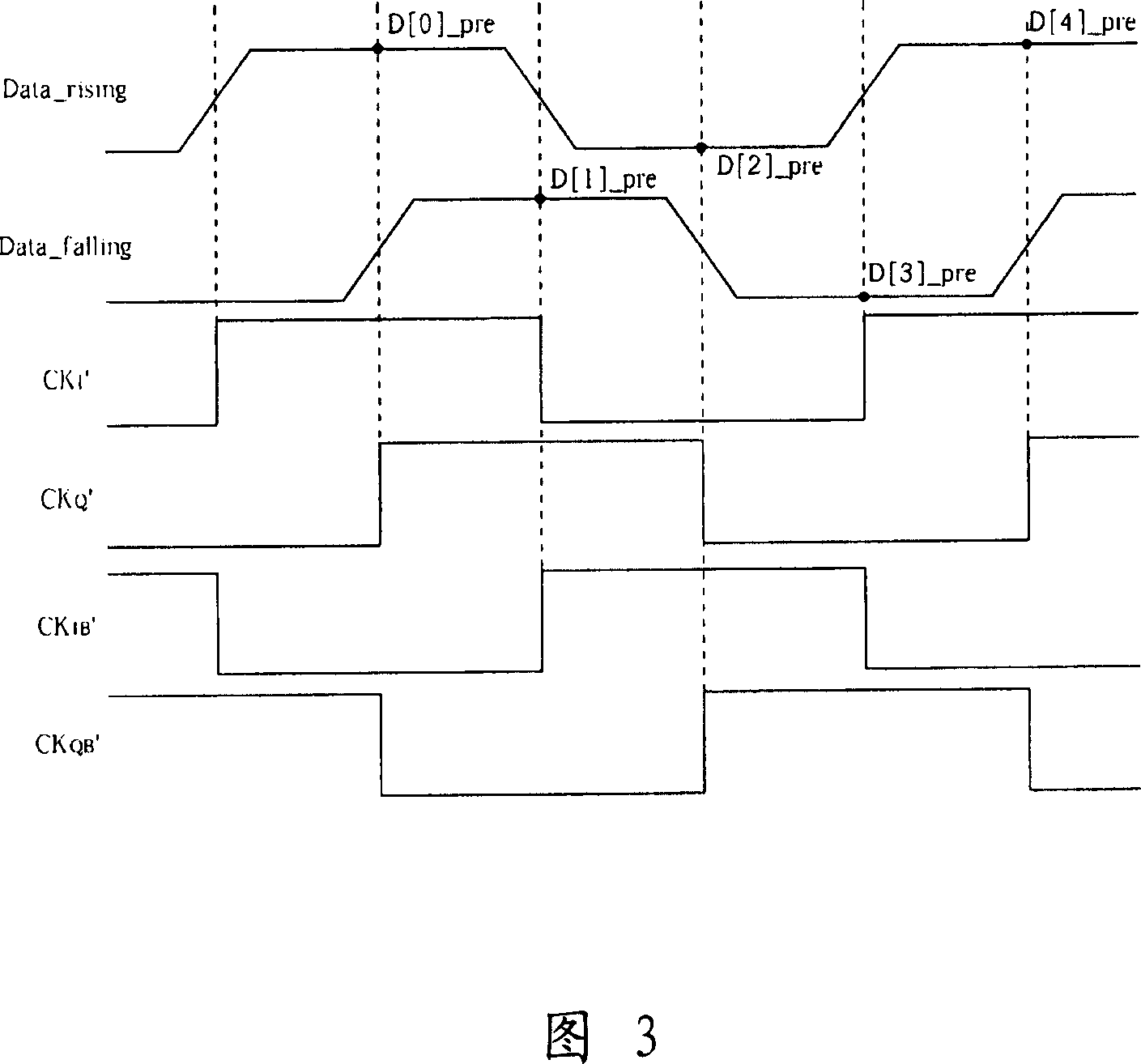

[0019] Please refer to FIG. 3 . FIG. 3 is a schematic diagram illustrating the clock and data recovery of the present invention. In this embodiment, all recovered clocks CK I ’, CK Q ’, CK IB ’, CK QB 'Used to detect the recovery clock CK I ’, CK Q ’, CK IB 、CK QB ' and the phase relationship between the first adjusted data Data_rising and the second adjusted data Data_falling. where the recovered clock CK I ’ with CK IB 'Used to detect the phase error of the first adjusted data Data_rising, and recover the clock CK Q ’ with CK QB ' is used to detect the phase error of the second adjusted data Data_falling. In addition, all recovered clock CK I ’, CK Q ’, CK IB 、CK QB ’ are used for data recovery operations to generate recovery data D out'. In short, compared with the prior art, which only uses part of the recovered clock, the present invention utilizes the recovered clock more efficiently. In addition, in this embodiment, the first adjusted data Data_rising ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More