Chip packing structure, chip structure and method for forming chip

A chip packaging and chip technology, applied in the fields of semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problem of chip 120 pollution, etc., to prevent primer from creeping, control quality and cost, chip structure and chip Create simple effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

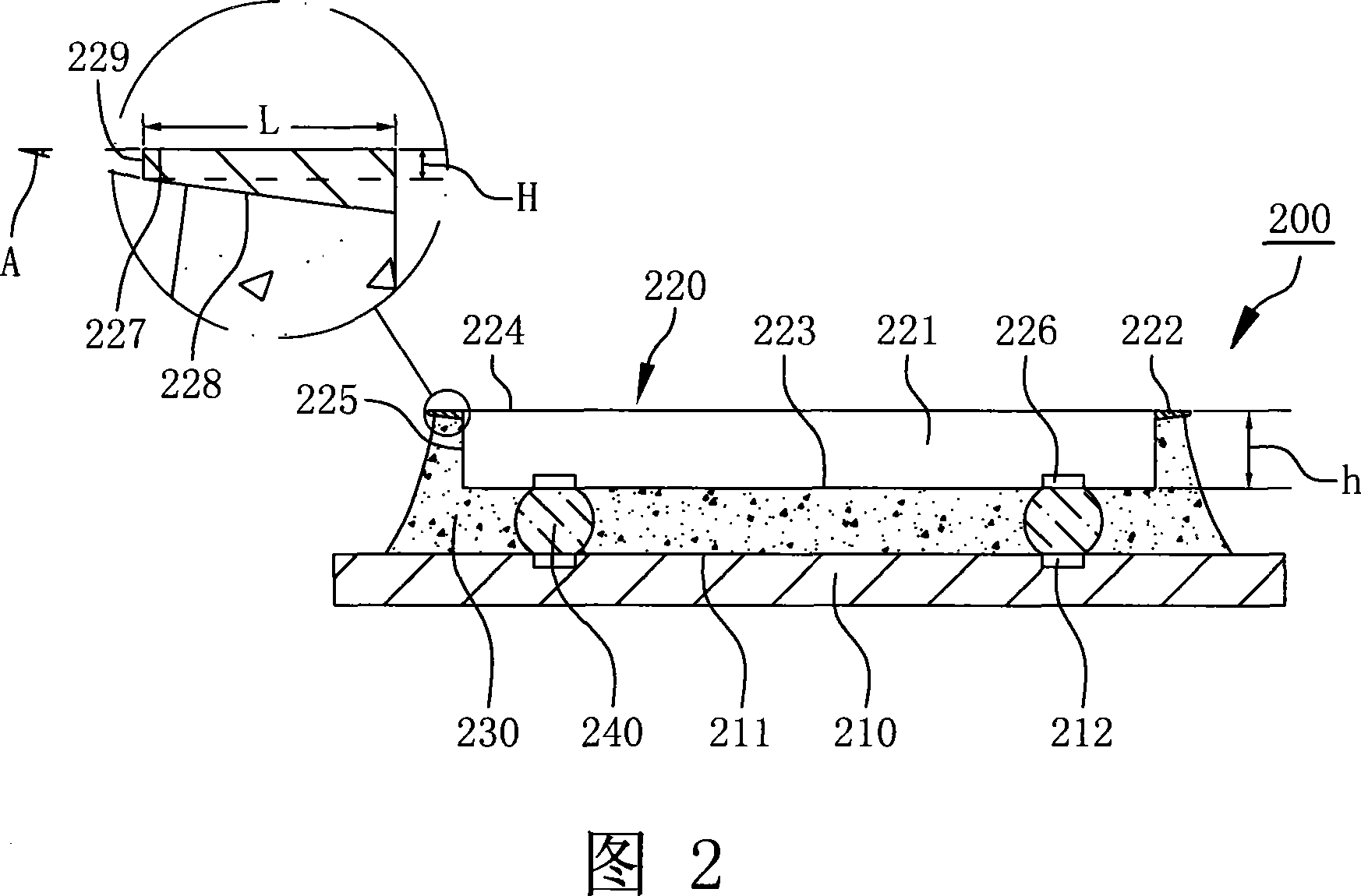

[0014] Please refer to FIG. 2 , a specific embodiment of the present invention discloses a chip packaging structure 200 , which includes a carrier 210 , a chip 220 and a primer 230 . The carrier 210 has a surface 211 on which a plurality of connection pads 212 are formed. The chip 220 is disposed on the surface 211 of the carrier 210 and electrically connected to the carrier 210. The chip 220 includes a chip Body 221 and a rubber blocking portion 222. The chip body 221 has an active surface 223, a back surface 224 and at least one side 225 between the active surface 223 and the back surface 224. Several solder joints are formed on the active surface 223. Pads 226, in addition, the chip 220 also includes several bumps 240, these bumps 240 are arranged on the pads 226 of the active surface 223, the active surface 223 of the chip body 221 faces the carrier 210 surface 211, and are bonded to the connection pads 212 of the carrier 210 through the bumps 240, the glue stop 222 can be...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More