Hierarchical low density check code decoder and decoding processing method

A low-density check code and decoder technology, which is applied to the application of error detection coding of multiple parity bits, error correction/detection using block codes, data representation error detection/correction, etc., can solve the problem of information nodes Information and check node information update, multi-memory resources, and decoder structure cannot be performed at the same time, so as to improve throughput, reduce delay, and reduce hardware resource consumption.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The embodiments of the present invention are described in detail below in conjunction with the accompanying drawings: this embodiment is implemented on the premise of the technical solution of the present invention, and detailed implementation methods and specific operating procedures are provided, but the protection scope of the present invention is not limited to the following the described embodiment.

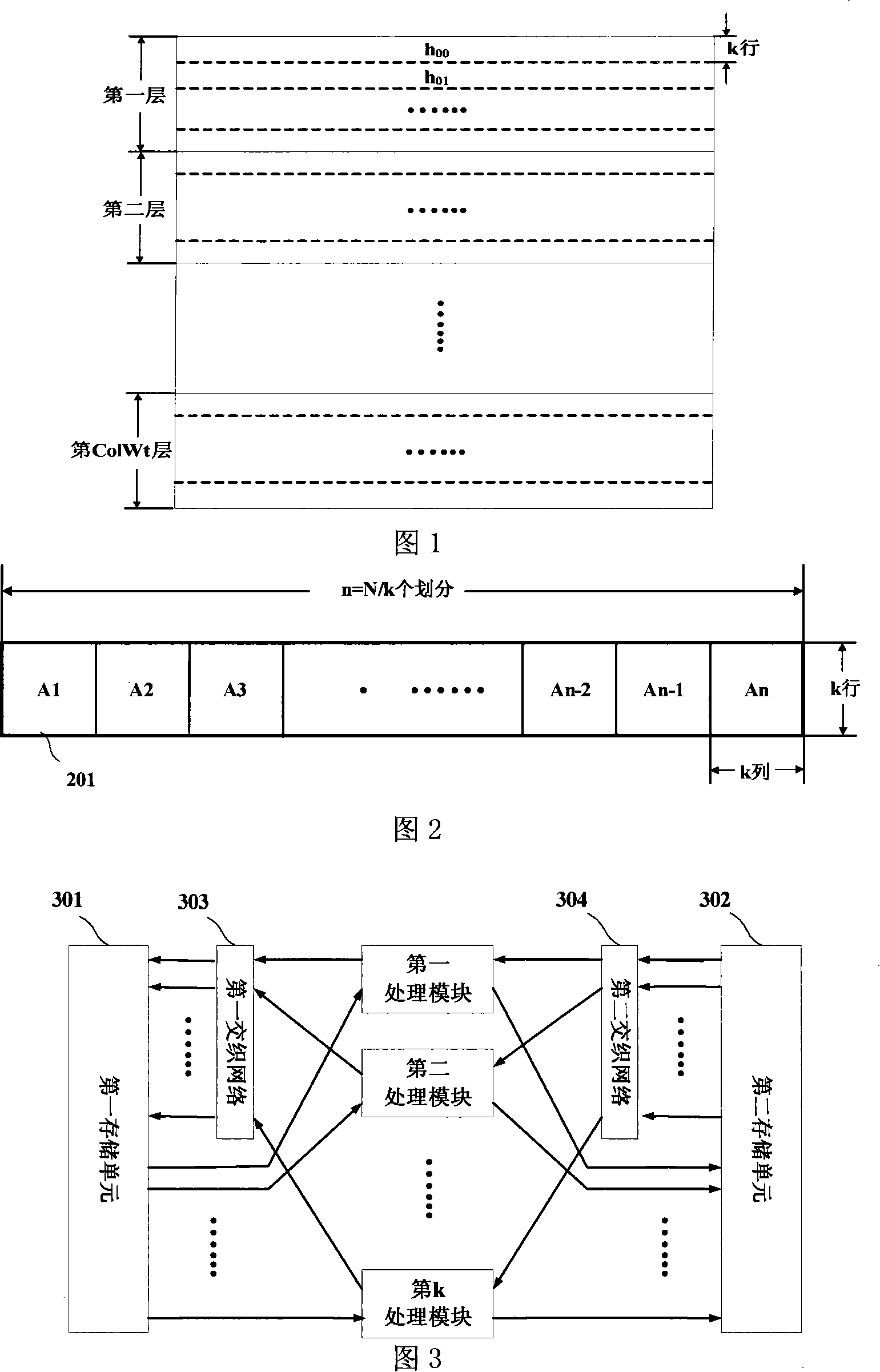

[0038] Accompanying drawing 1 is the structural diagram of the LDPC check matrix (H matrix) of the decoder that is applicable to the degree of parallelism k at present, and the row of H matrix is rewritten as RowWt, and the column is rewritten as ColWt. The H matrix contains ColWt layers, each layer has the same number of rows, and the column weight of each layer is 1; each layer is divided into several units in the row direction, and each unit contains k rows. Such units are called sub-matrixes. h 00 or h 01 is an example of a sub-matrix.

[0039] Accompanying d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More