Method for manufacturing isolation structure

A manufacturing method and isolation structure technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as increasing manufacturing costs and increasing process complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

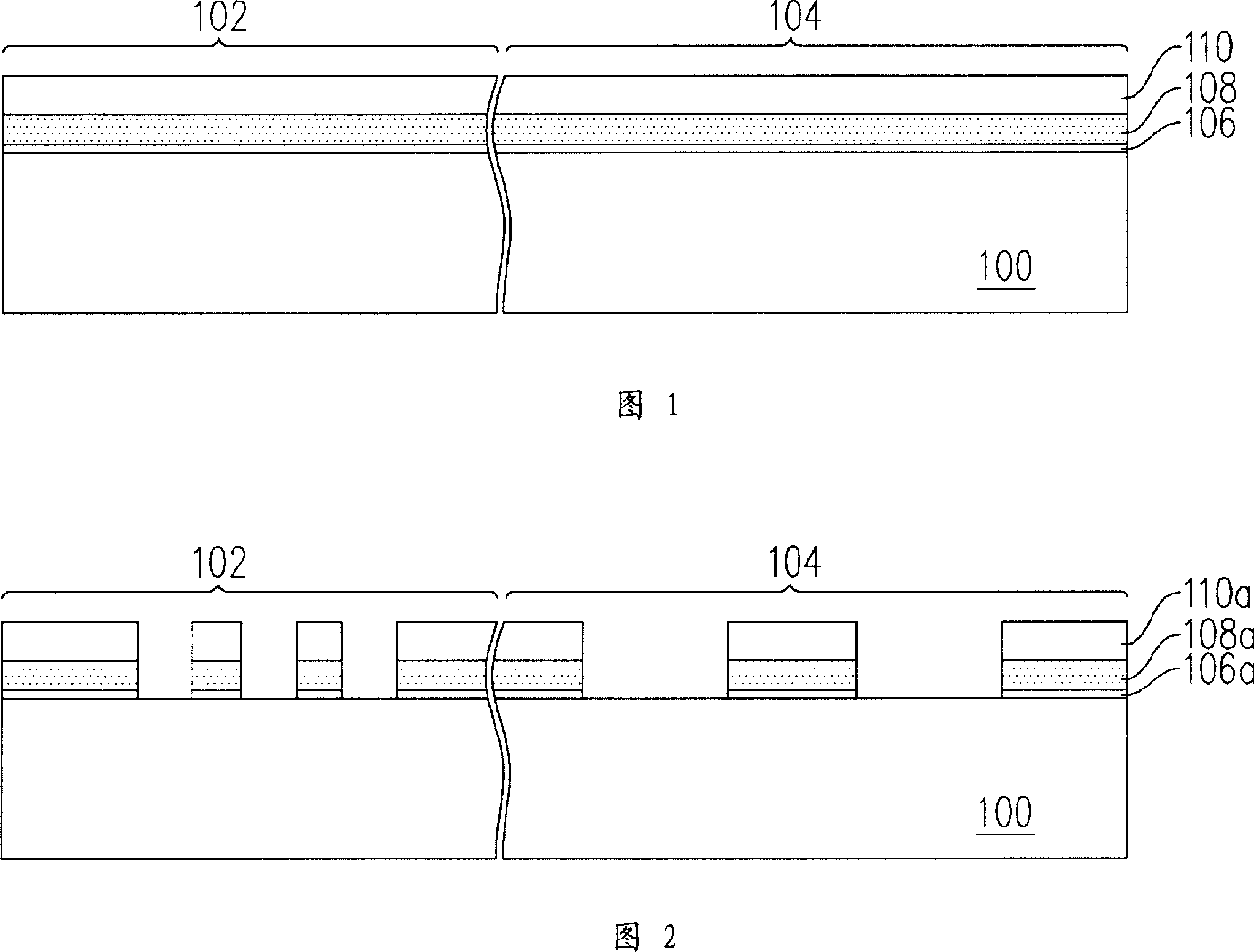

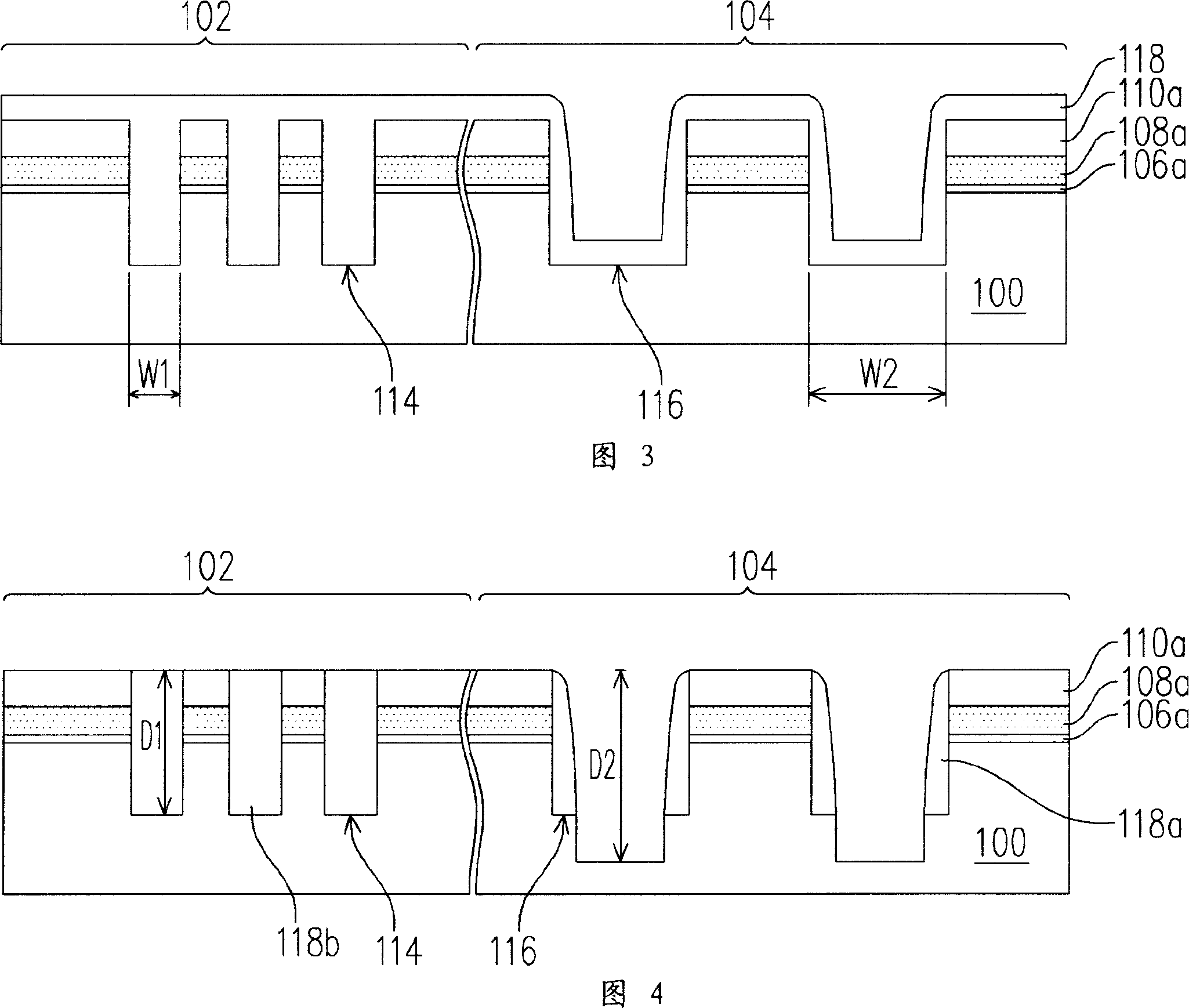

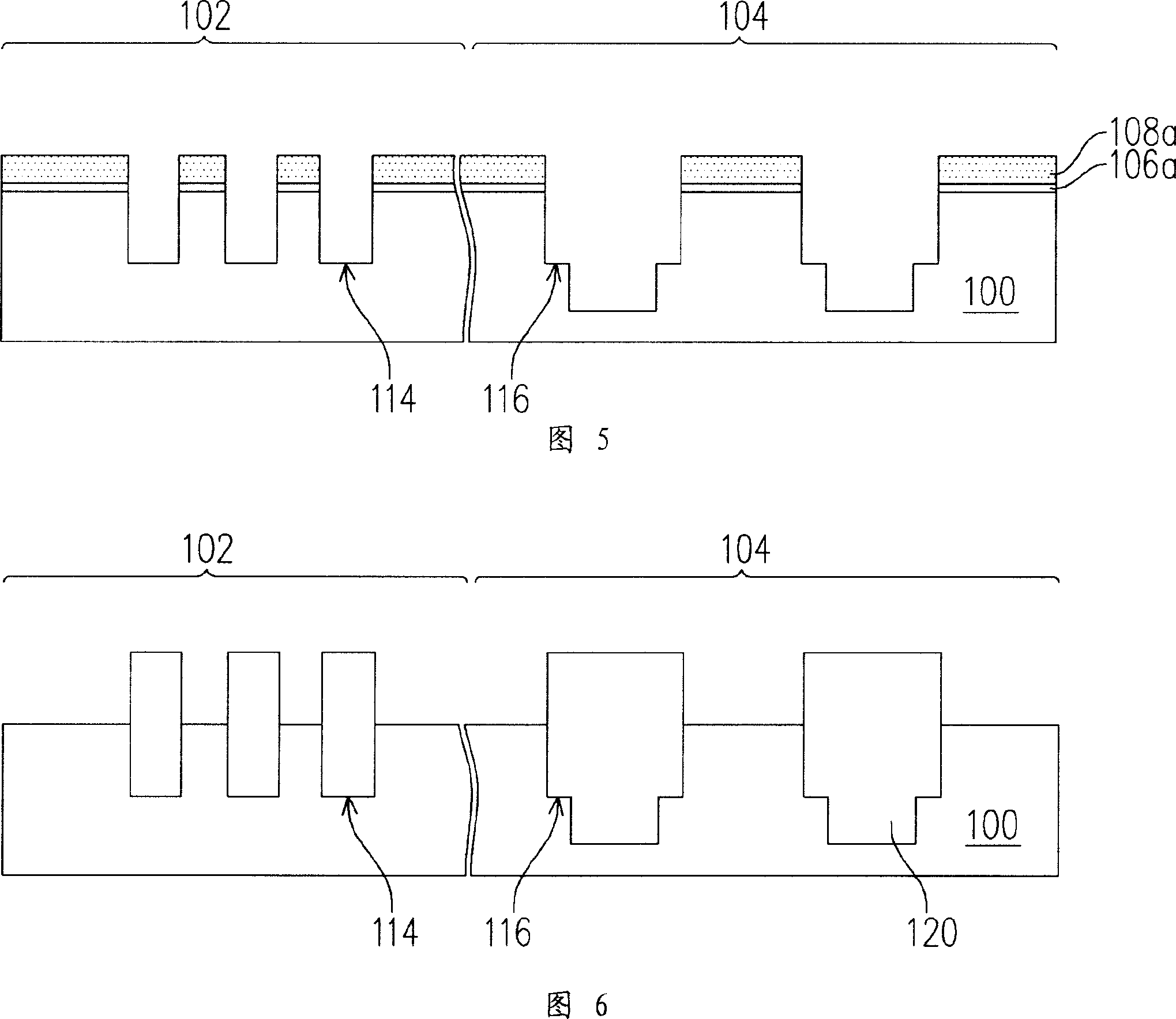

[0035] In view of the shortcomings of the prior art, the present invention provides a method for manufacturing an isolation structure. In this manufacturing method, two groups of grooves with different widths are firstly formed on the substrate. Afterwards, a spacer is formed on the sidewall of the wider trench, and at the same time, the material of the spacer fills up the narrower trench. Then, using the self-aligned principle, the part of the substrate exposed by the spacer is removed by using the spacer as a mask, so as to deepen the depth of the trench. Afterwards, a dielectric layer is formed in the two groups of trenches to form an isolation structure.

[0036] 1 to 6 are cross-sectional flowcharts of a method for manufacturing an isolation structure according to an embodiment of the present invention.

[0037] Referring to FIG. 1 , firstly, a substrate 100 is provided. The substrate 100 is, for example, a silicon substrate. The substrate 100 can be divided into a fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More