Data processing system and method for memory defragmentation

A data processing system and memory technology, applied in memory systems, electrical digital data processing, instruments, etc., can solve the problem of memory becoming fragmented

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

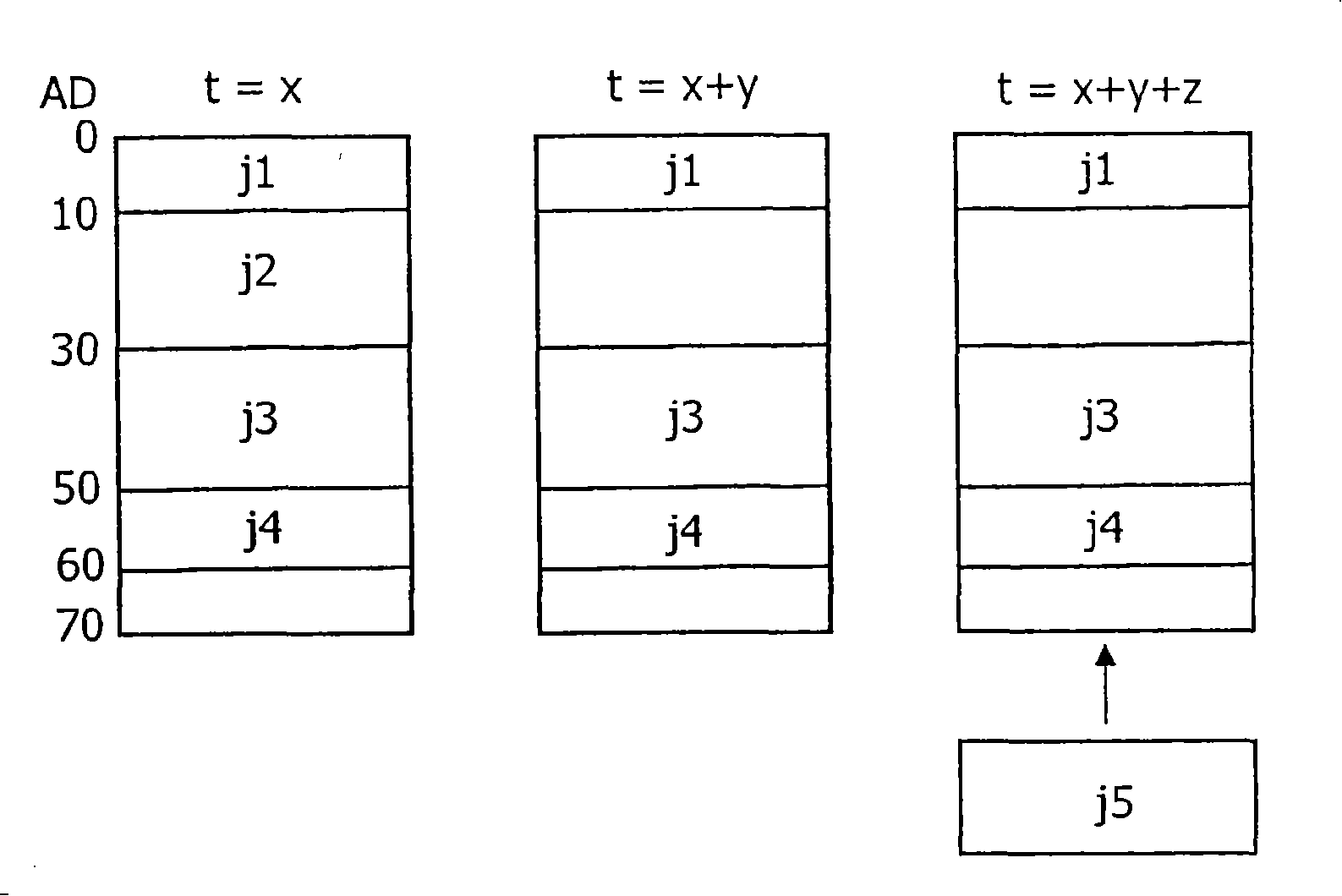

[0021] The architecture of the preferred embodiment of the present invention is specifically designed to handle continuous media streams in a multi-processing environment, ie, the architecture is designed for media processing applications and can be reconfigured at runtime without significant performance degradation. Signal processing for such media applications includes stream-based processing utilizing FIFO periodic communication behavior. Effective logical FIFO implementations require that the address range of a FIFO be contiguous such that the next word in the FIFO can be found by incrementing the pointer in the FIFO.

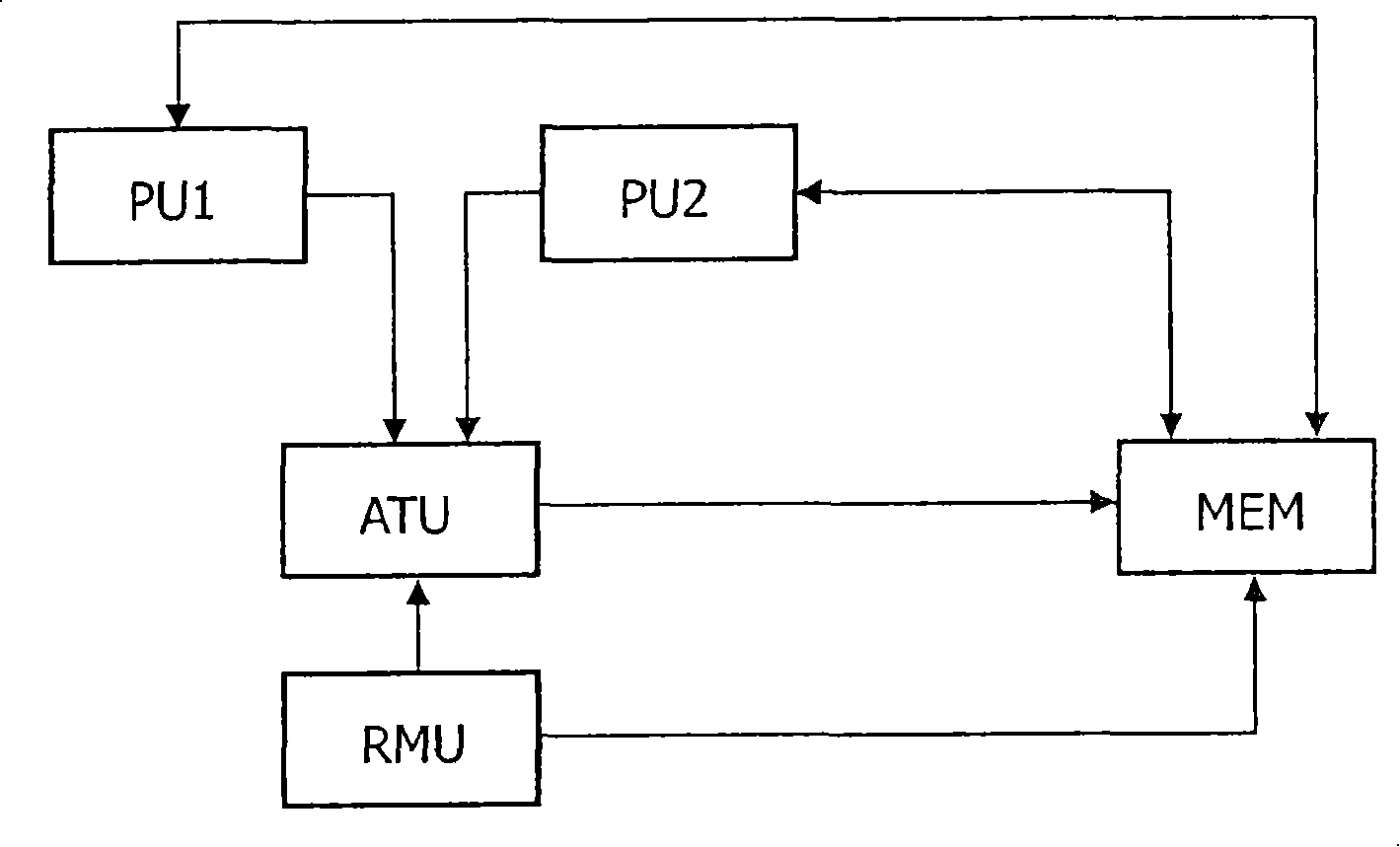

[0022] figure 1 A block diagram showing the construction of a system on chip according to a preferred embodiment of the present invention. The system comprises a first and a second processing unit PU1, PU2, a memory means MEM and an address translation unit ATU. The first and second processing units PU1, PU2 are each connected to a memory and to an addres...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More