High speed bit flat surface decoding method and circuit suitable for Jpeg2000 standard

A bit-plane, standard technology, applied in the field of bit-plane decoding methods and circuit implementations, can solve problems such as low decoding efficiency, failure to start, and high hardware complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

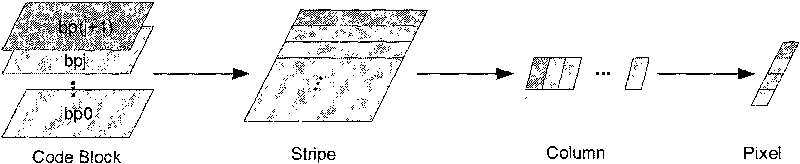

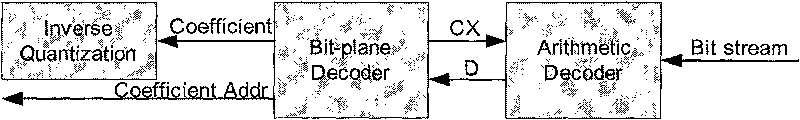

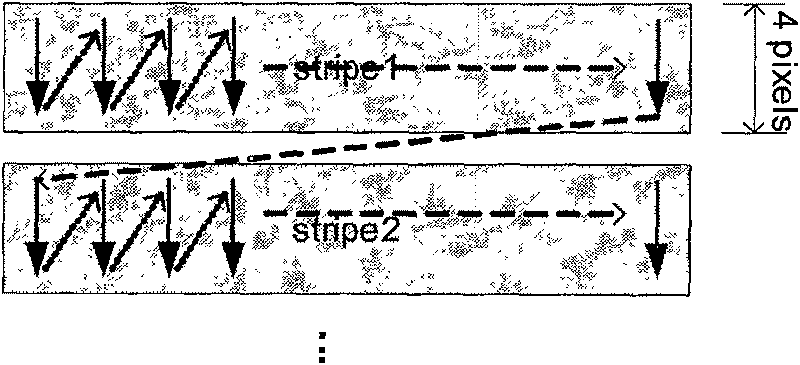

Method used

Image

Examples

Embodiment Construction

[0042] The present invention will be further described in detail below in combination with three decoding processes.

[0043] The decoding of the entire EBCOT is completed with the cooperation of BPD and MQD. The two complete the communication through two handshake signals: bpd_rely and mqd_ready signals. The generation of CX and D is completed in one clock cycle, that is, each generation of a decoding coefficient bit requires two clock cycles. The timing diagram is shown in Figure 9. In this way, the work of "pixel guidance" needs to be completed within one clock cycle, that is, to find the coefficient bit to be solved in the current window. After the coefficient is solved, the update of the register is completed, and the corresponding bit_index The bit becomes "zero", so the decoding engine is guided to decode the next bit, that is, the first non-zero bit from the high bit of bit_index. If bit_index is all zero, it indicates that all coefficients of the current window have b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More