Special arithmetic unit ALU

A computing unit and arithmetic technology, applied in the direction of calculation, program control design, instrument, etc., can solve the problems of poor compatibility and achieve the effect of simple structure, fast speed, fast arithmetic and logic operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

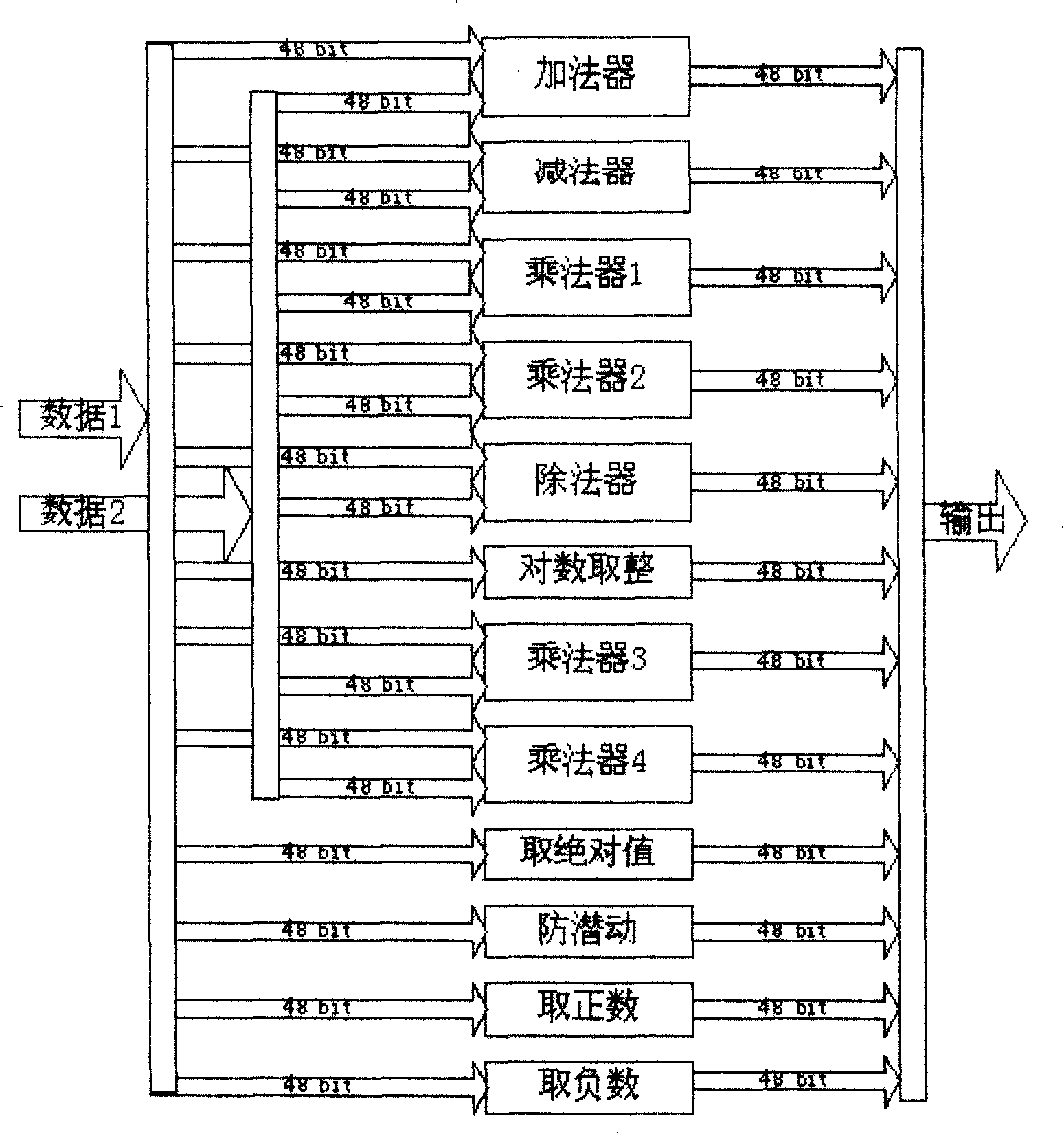

[0011] See figure 1 As shown, this is a schematic diagram of the structure of the dedicated arithmetic unit ALU. The dedicated arithmetic unit ALU has two 48bit data input terminals and one 48bit data output terminal.

[0012] The main modules included in the special operation unit ALU are adder, subtractor, multiplier 1, multiplier 2, divider, logarithm rounding, multiplier 3, multiplier 4, absolute value, anti-creep, positive Counting and taking negative numbers, a total of 12 arithmetic or logic operation modules. The main functions of each module are as follows:

[0013] (1) Adder (48bit+48bit): output the result of adding "data 1" and "data 2";

[0014] (2) Subtractor (48bit-48bit): output the subtraction result of "data 1" and "data 2";

[0015] (3) Multiplier (48bit*48bit): output the result of multiplying "data 1" and "data 2" and dividing by 240;

[0016] (4) Multiplier (48bit*48bit): output the result of multiplying "data 1" and "data 2" and dividing by 228;

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More