A non-integer frequency difference eliminator and phase-lock loop that can product non-integer real-time clock signal

A clock signal, non-integer technology, applied in the direction of pulse processing, pulse technology, power automatic control, etc., can solve the problem of unable to change multiple frequency division modes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

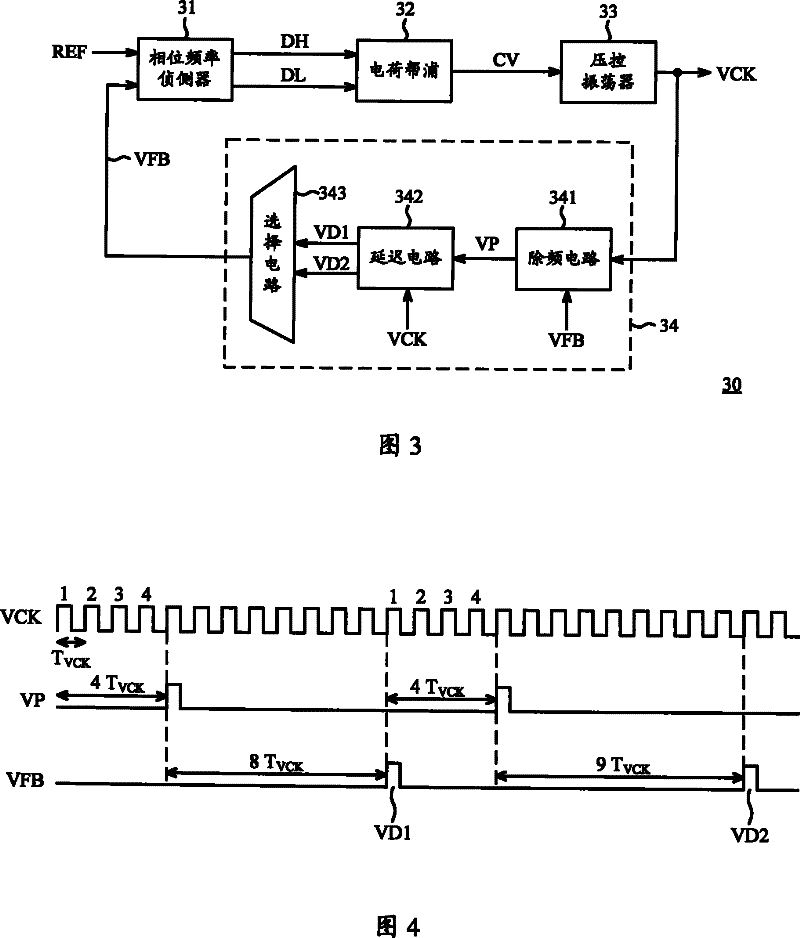

[0024] FIG. 3 is a circuit block diagram of a phase-locked loop 30 according to an embodiment of the present invention. Please refer to FIG. 3 , the PLL 30 includes a phase frequency detector 31 , a charge pump 32 , a voltage controlled oscillator 33 , and a non-integer frequency divider 34 . The non-integer frequency divider 34 includes a frequency dividing circuit 341 , a delay circuit 342 , and a selection circuit 343 . The coupling relationship among all components in the phase-locked loop 30 of this embodiment is shown in FIG. 3 . In addition, the following labels are also marked in FIG. 3 , which are respectively: the reference signal REF received by the phase frequency detector 31, the clock signal VCK output by the voltage-controlled oscillator 33, and the frequency division signal output by the frequency division circuit 341. The frequency pulse VP, the first delay pulse VD1 and the second delay pulse VD2 output by the delay circuit 342 , and the output pulse VFB fed...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More