Enabling multiple instruction stream/multiple data stream extensions on microprocessors

A processor and multi-processor system technology, applied to the architecture with multiple processing units, multi-program device, program startup/switching, etc., can solve the problems of not being able to provide protection for objects or units, not knowing AMS, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

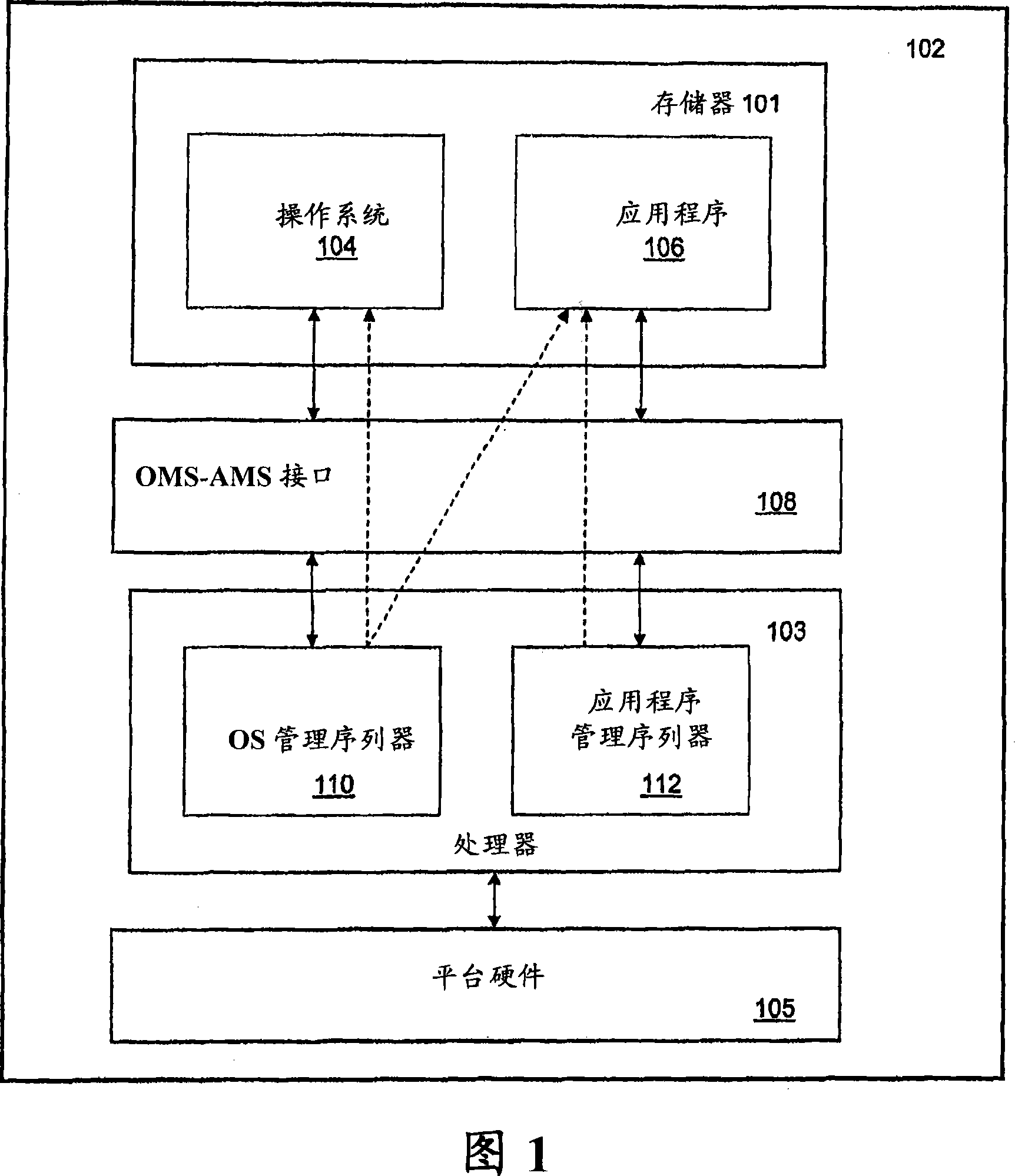

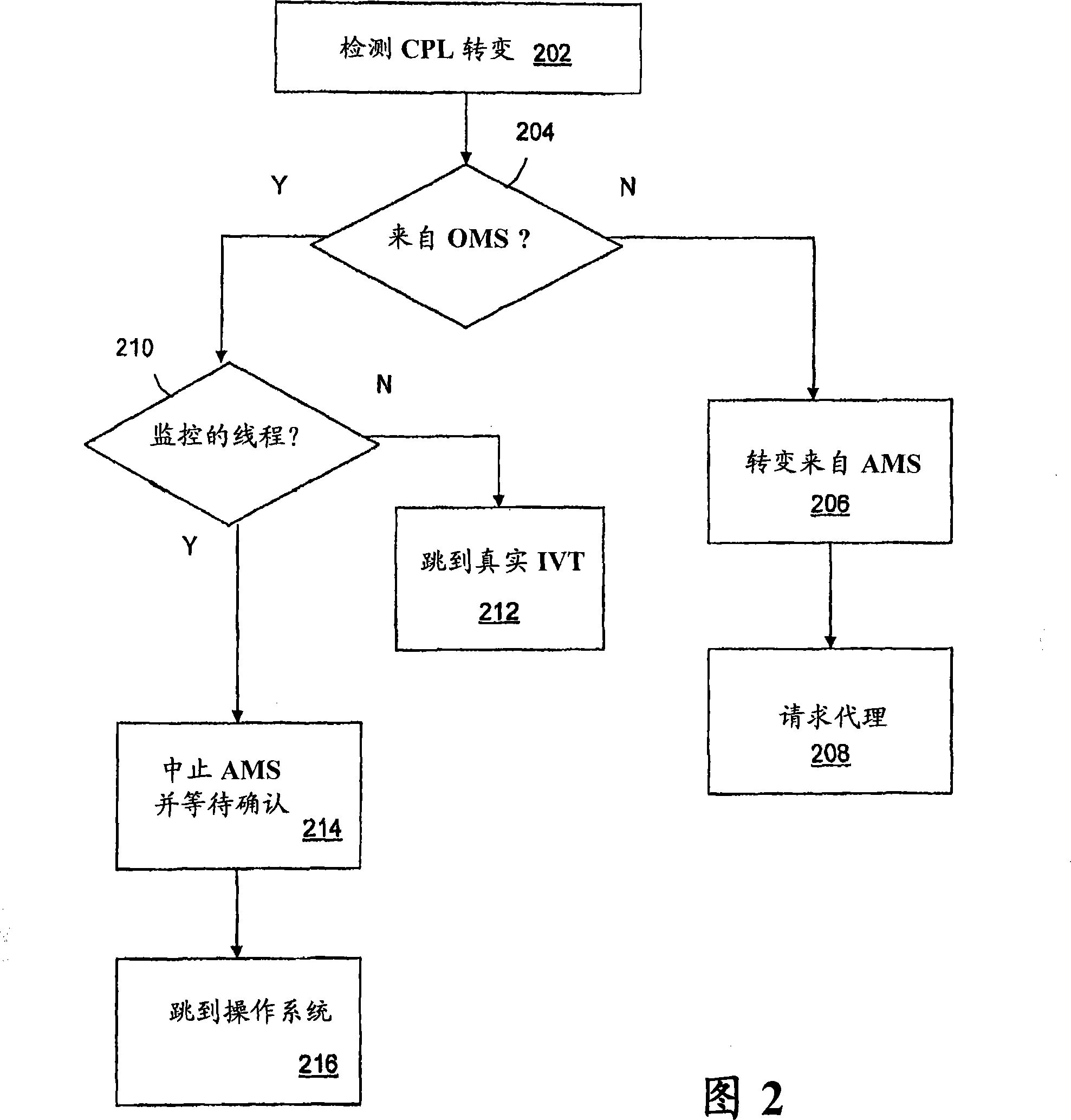

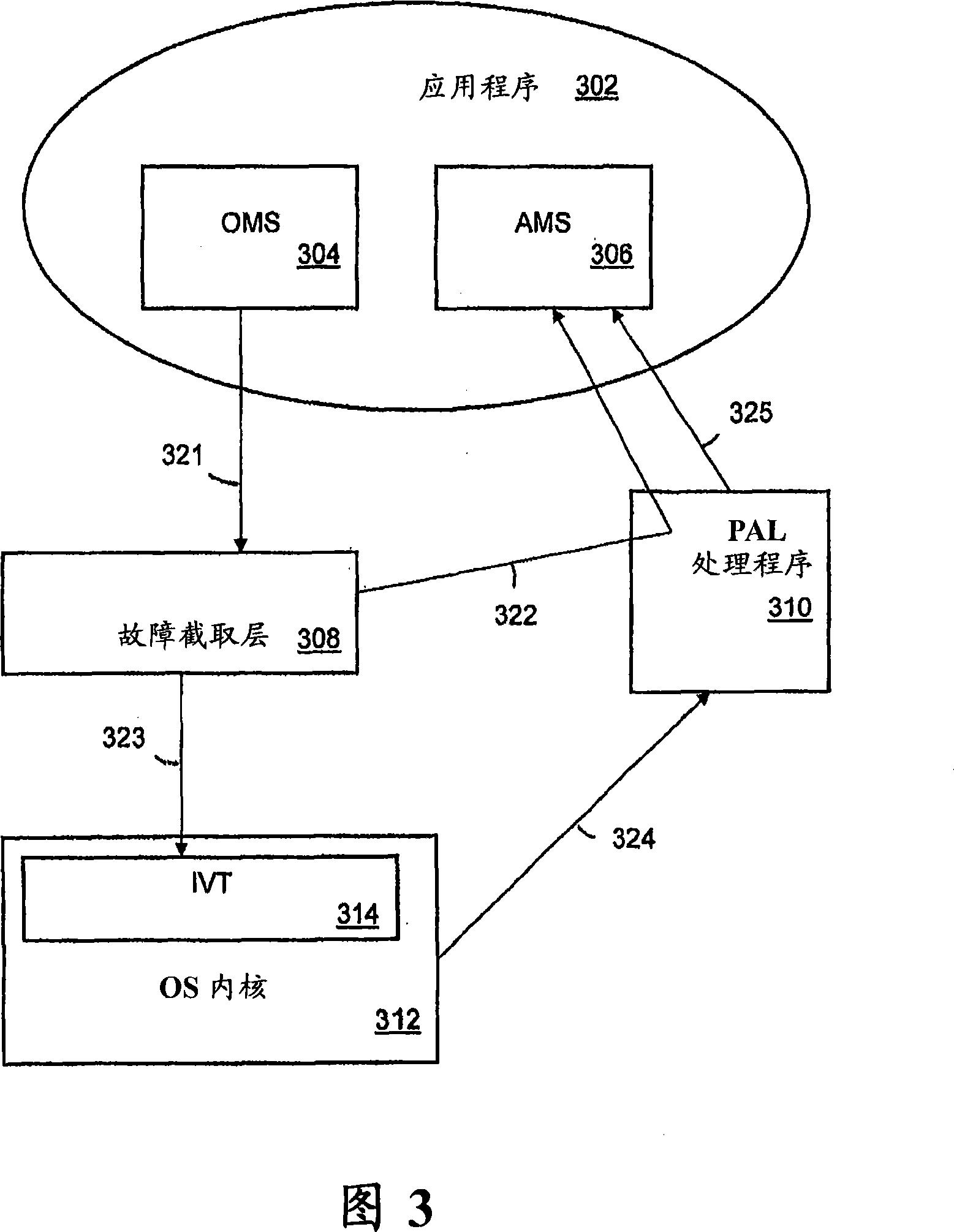

[0013] Embodiments described herein disclose a system for allowing simulation of Multiple Instruction Stream / Multiple Data Stream (MIMD) extensions that support user-level sequencer management and control, and execution by operating system-managed sequencers and application-managed sequencers A set of privileged codes, including different sets of persistent per-CPU and per-thread data. In one embodiment, the portable code layer executes below the operating system. This layer of code is invoked in response to specific monitoring events such as communication needs between OMS and AMS. When this occurs, control is transferred to this layer of code, one or more dedicated operations are performed, and control is returned to where the code was originally executed. While the user application or operating system is executing, the code layer is usually dormant and can be invoked at any time. Includes mechanisms for maintaining processor execution state and interrupt state, where proc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com