Method for parallel data processing adopting multi- password chip

A data processing and multi-password technology, applied in the field of data encryption and decryption, can solve problems such as system unavailability, resource occupation, system processing performance decline, etc., to avoid insufficient PCI bus resources and interrupt resources, and improve encryption and decryption speed.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] Below in conjunction with accompanying drawing and embodiment the present invention will be further described:

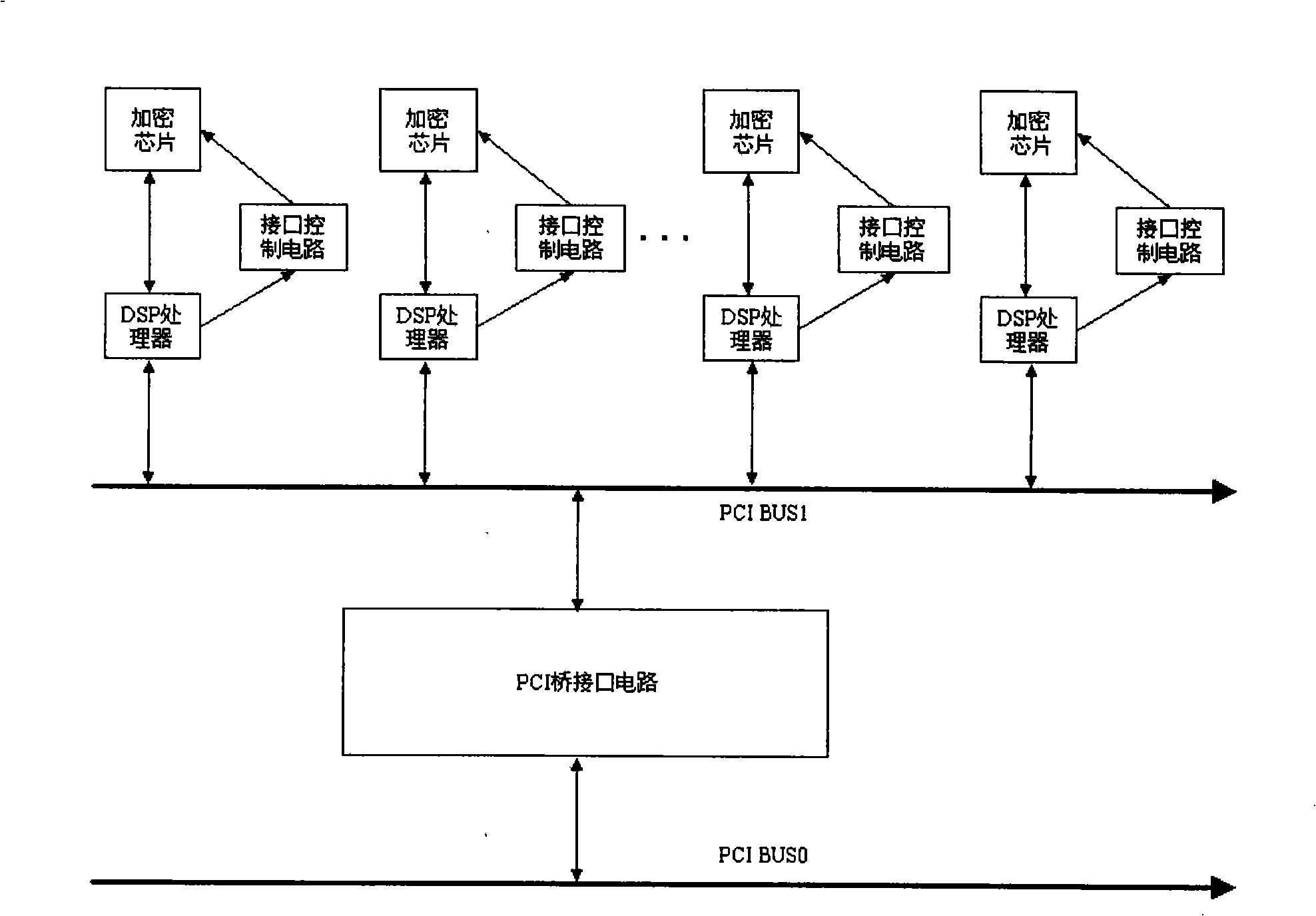

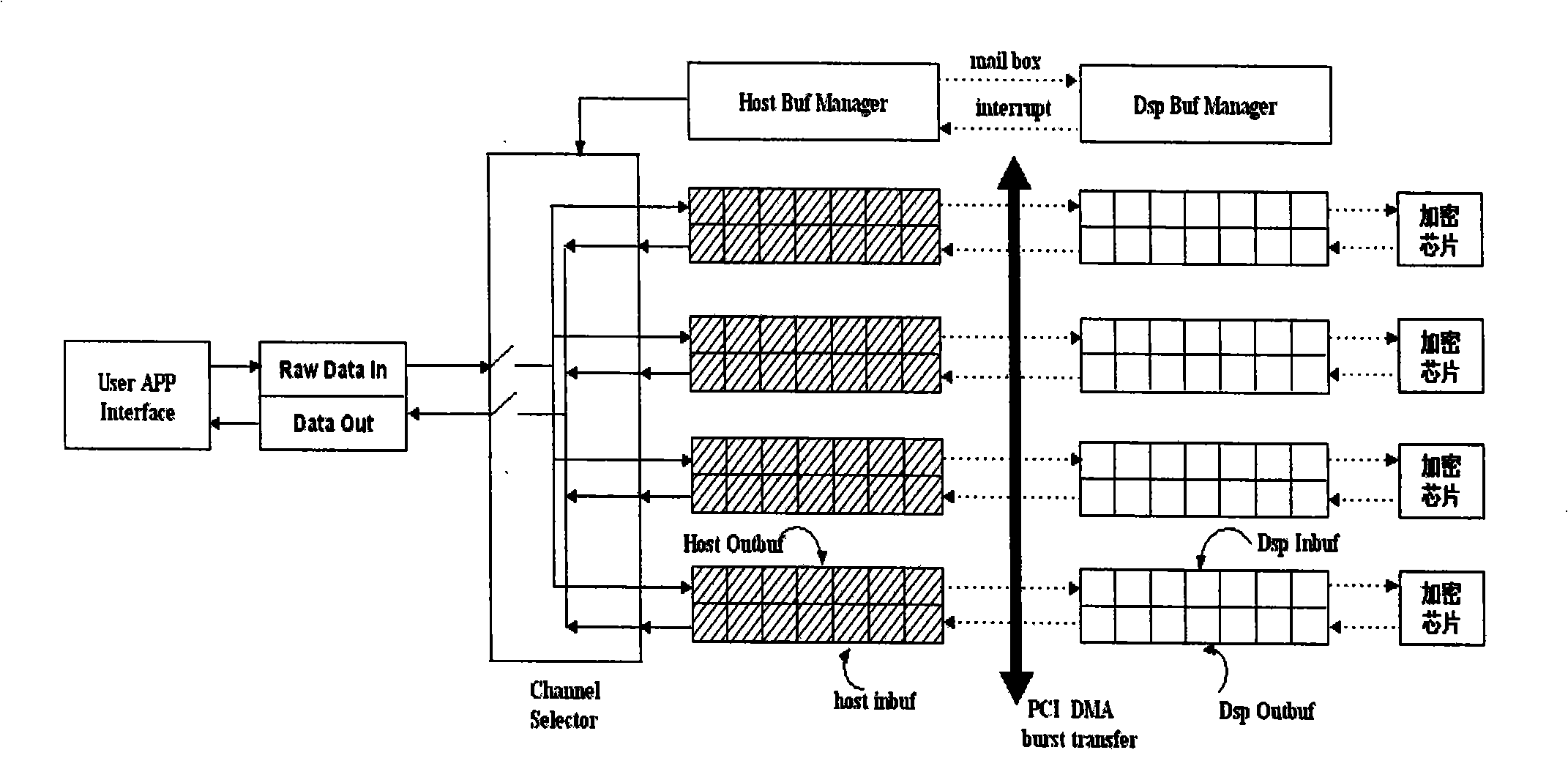

[0038] from figure 1 , figure 2 It can be seen that a parallel data processing device based on multiple cipher chips consists of multiple symmetric encryption chips to form multiple encryption and decryption channels, and the interface control circuit controls the timing of the encryption chips. The PCI bus expansion chip is used to expand a PCI BUS1, avoiding the lack of load capacity of the PCI BUS0 device on the host platform. On the PCI BUS1, a plurality of DSP processor chips are connected, and the chips are used to complete the IO processing of the parallel multi-channel encryption chips.

[0039] There is a 64K internal data RAM in the DSP chip, and the host host can access the RAM in a burst mode through the PCI bus, and the DSP has the PCI Master capability. In the actual software design, the CPU puts the original data in a piece of local memory,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More