Patents

Literature

738results about How to "Avoid resources" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

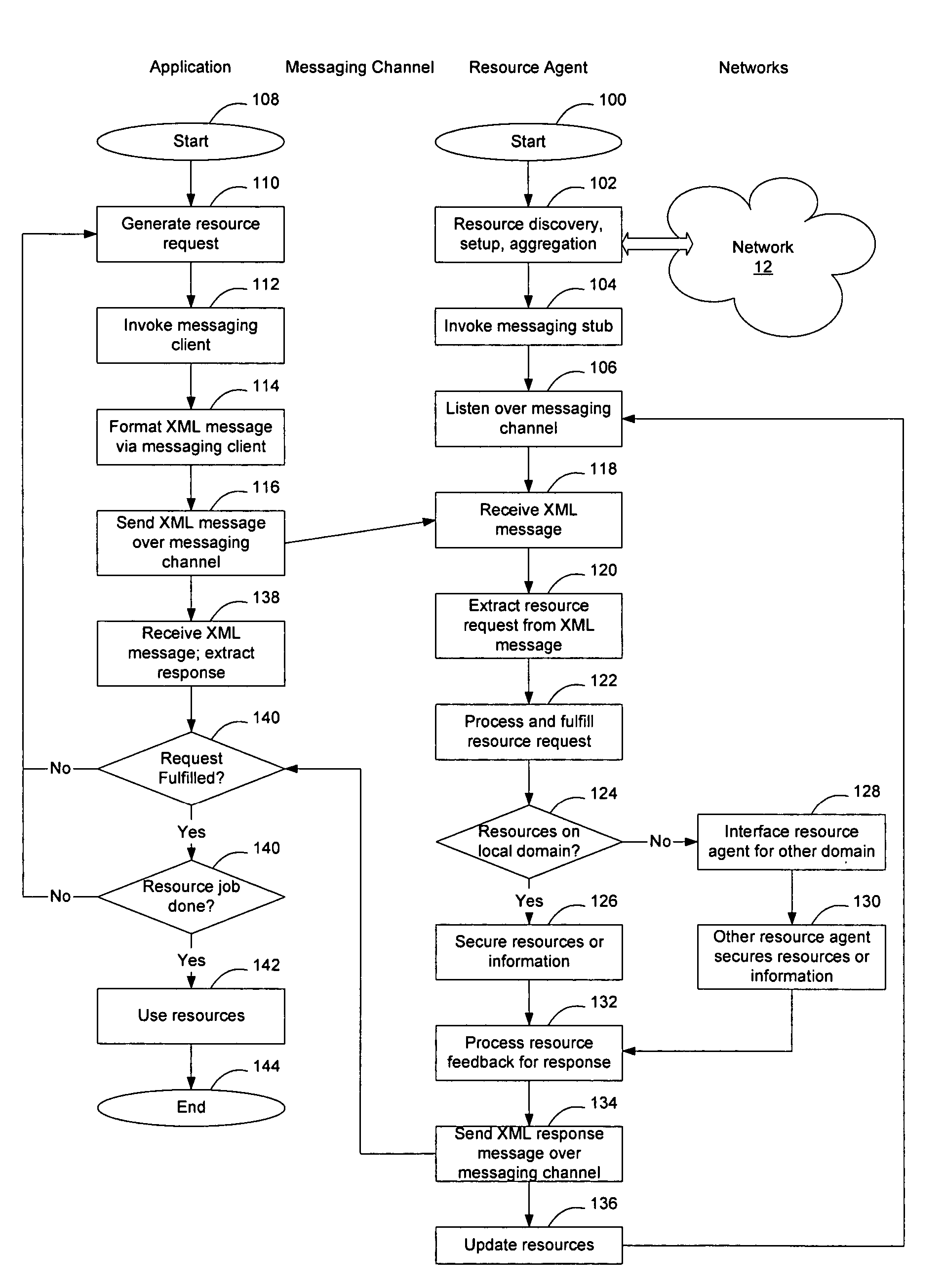

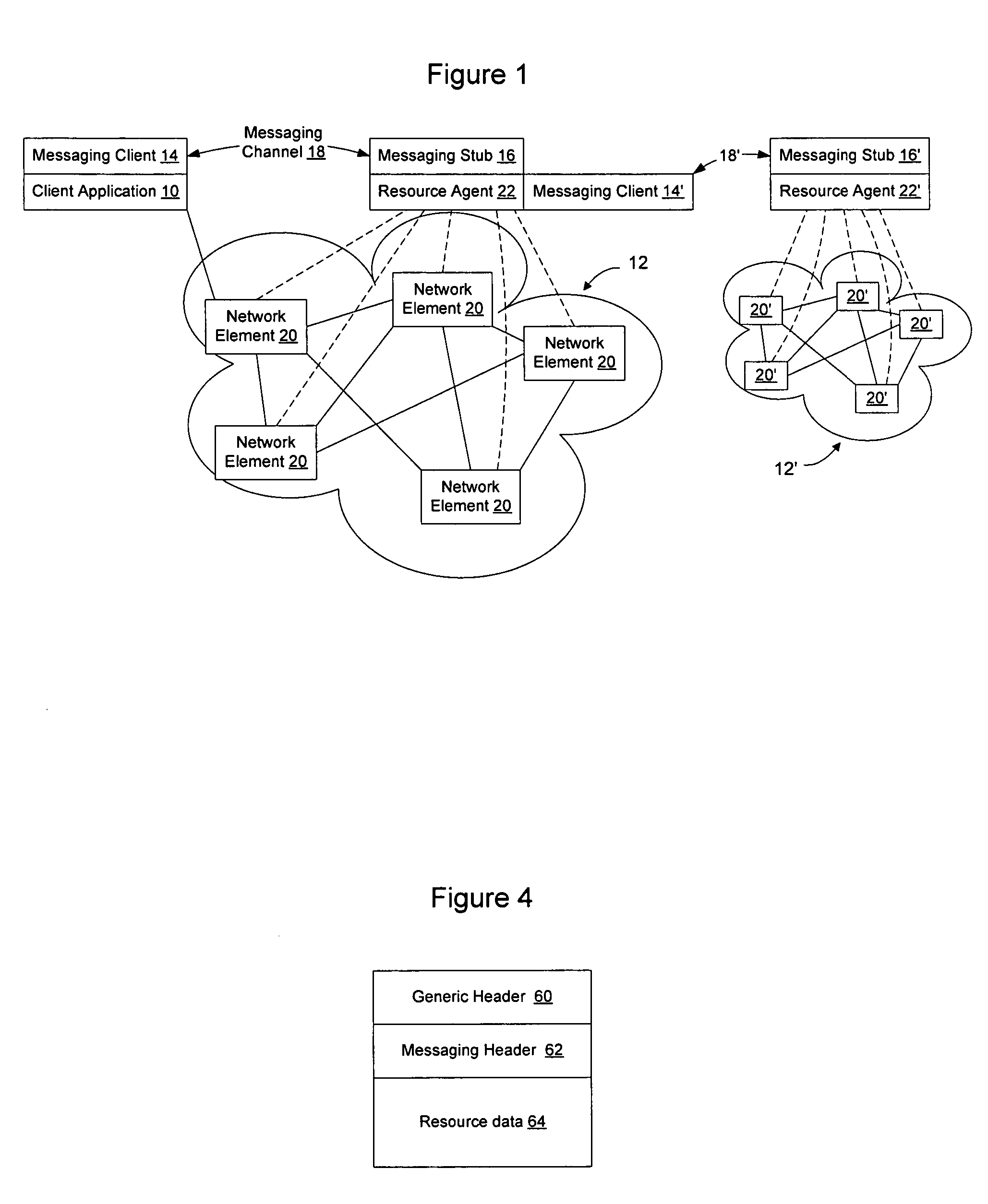

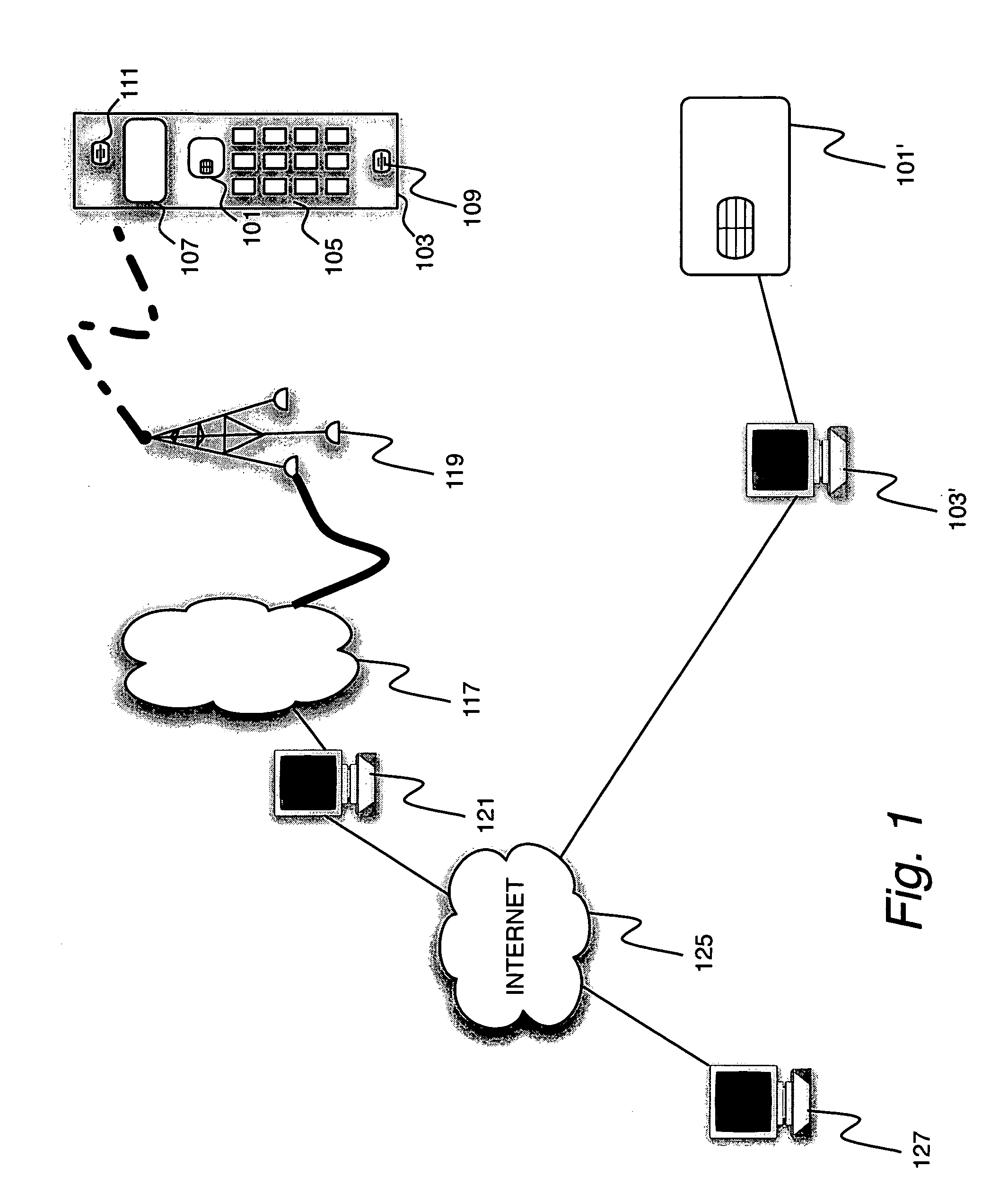

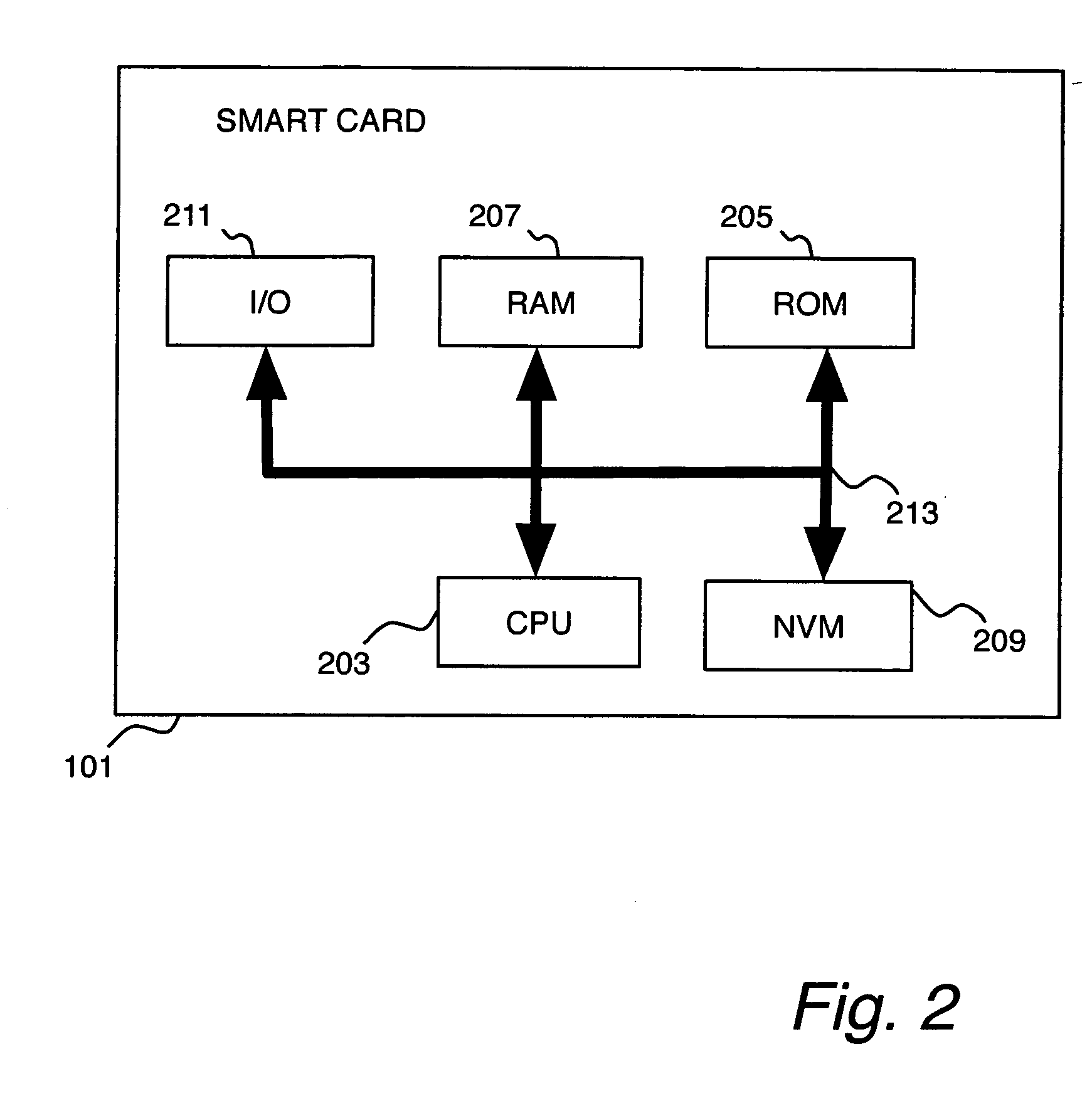

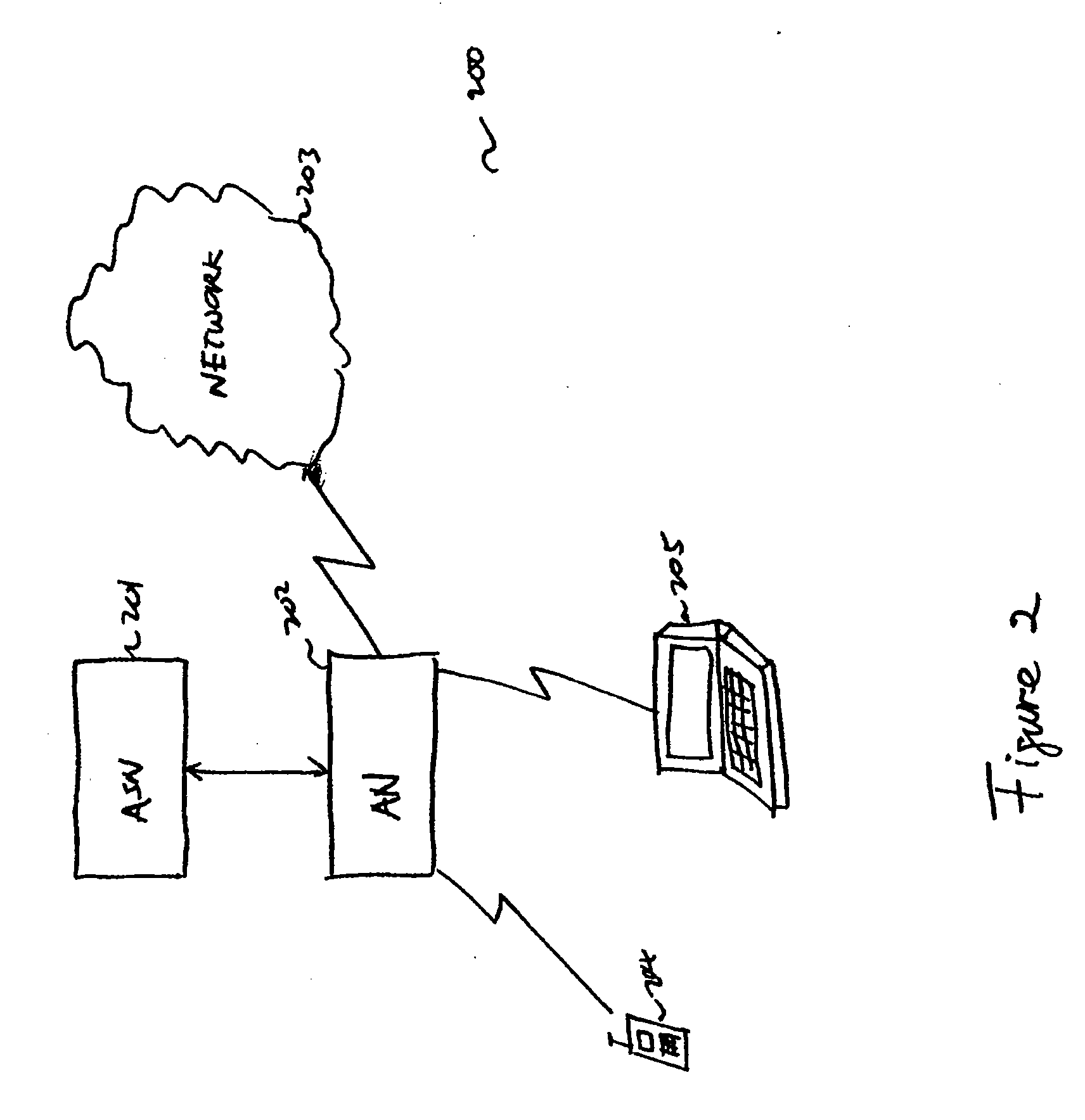

Extensible resource messaging between user applications and network elements in a communication network

InactiveUS20060075042A1Easily use new network resourceAvoid resourcesMultiple digital computer combinationsTransmissionXML schemaMessage passing

Extensible resource messaging in a communication network is provided through creation of a flexible, extensible, and secure messaging environment. A client-server architecture may be implemented in which user applications employ messaging clients to send resource requests for network information, allocation and other operations and receive resource responses, and in which network elements, through resource agents, may use messaging servers to accept resource requests and return resource responses. Resource agents in different network domains may interact through the messaging environment and work together to fulfill resource requests. An XML-based messaging mechanism may be built with a defined message format that can provide flexible message contexts. Network resource semantics may be specified using XML schemas so that network resources are expressed as resource-specific XML elements and network updates can be implemented by updating the XML resource schemas. Secure enhancements may be realized by secure transport, message verification and other means.

Owner:NORTEL NETWORKS LTD

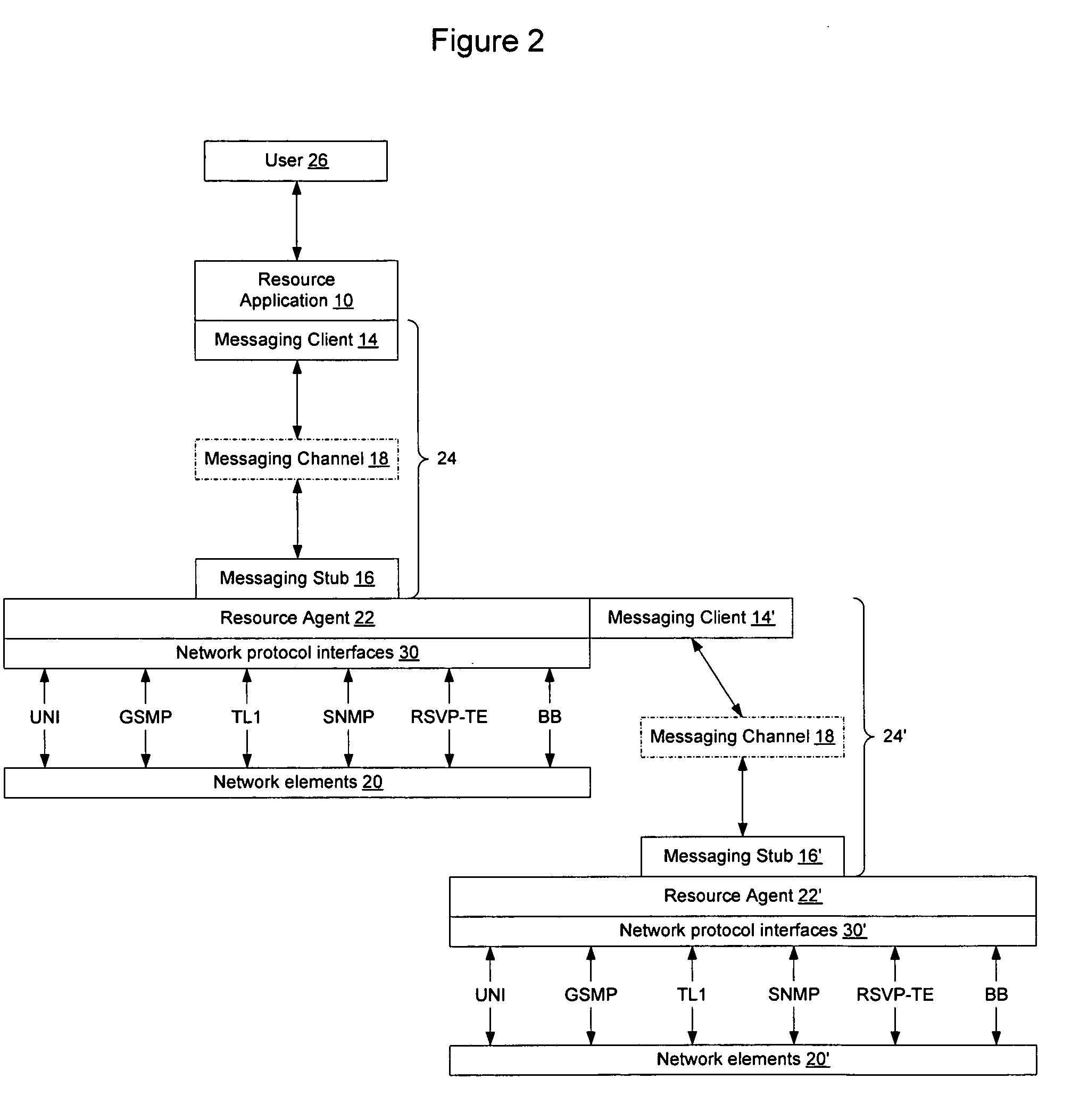

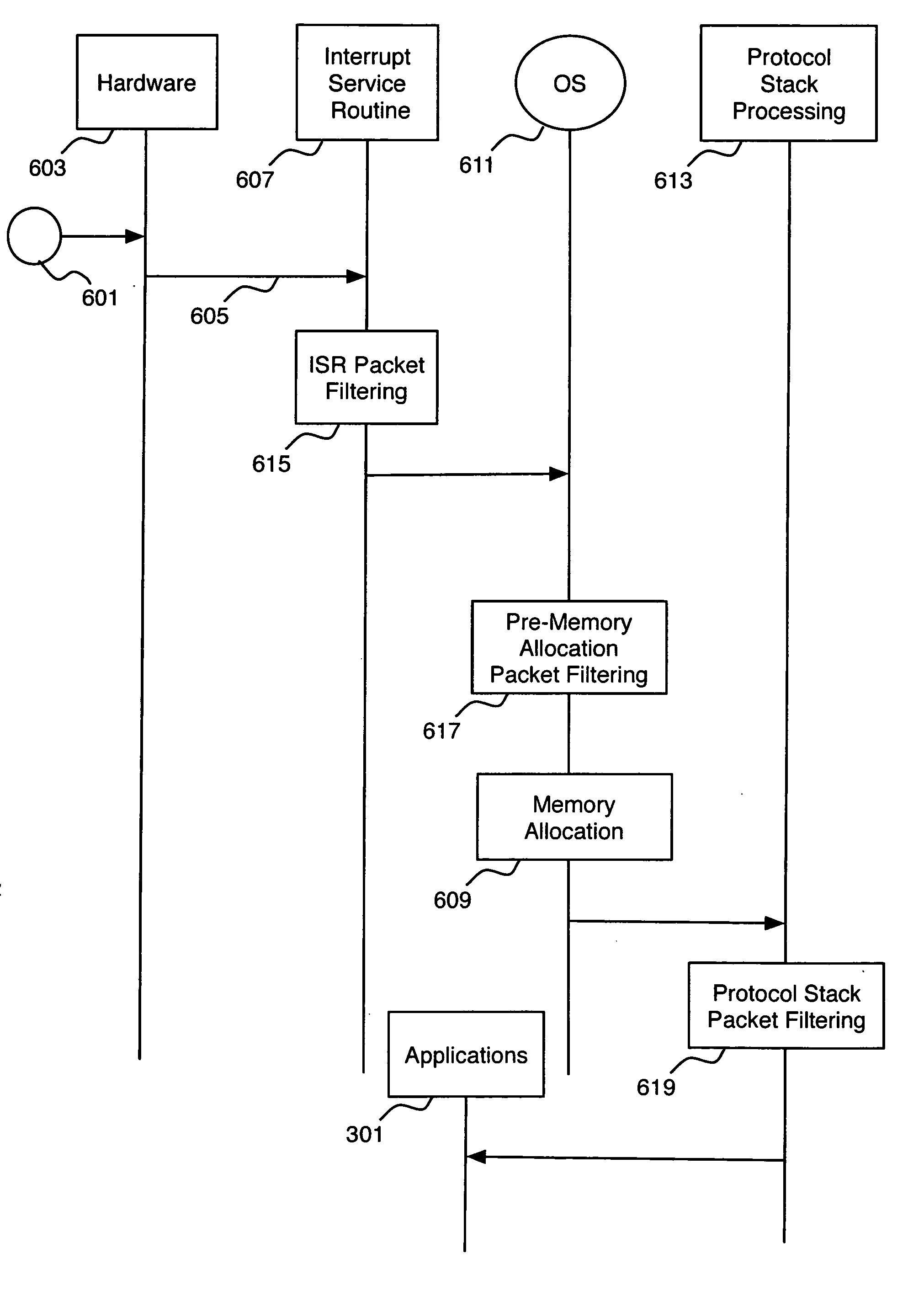

System and method for multi-stage packet filtering on a networked-enabled device

InactiveUS20070083924A1Avoiding allocating memory resourceAvoid resourcesMultiple digital computer combinationsProgram controlData packProtocol processing

A multi-stage packet filtering method and system. The multi-stage packet filtering according to the invention applies a set of filtering rules early in the processing of incoming communications packets by filtering incoming data packets using the filtering rules in a plurality of stages wherein the first stage is triggered by the receipt of a data packet by the device. Filtering rules that cannot be applied in the first stage may be deferred to a pre-memory allocation stage. Thus, preferable leaving only rules that must be executed in conjunction with protocol processing to be filtered at a filtering stage executed in a protocol processing filtering stage.

Owner:LU HONGQIAN KAREN

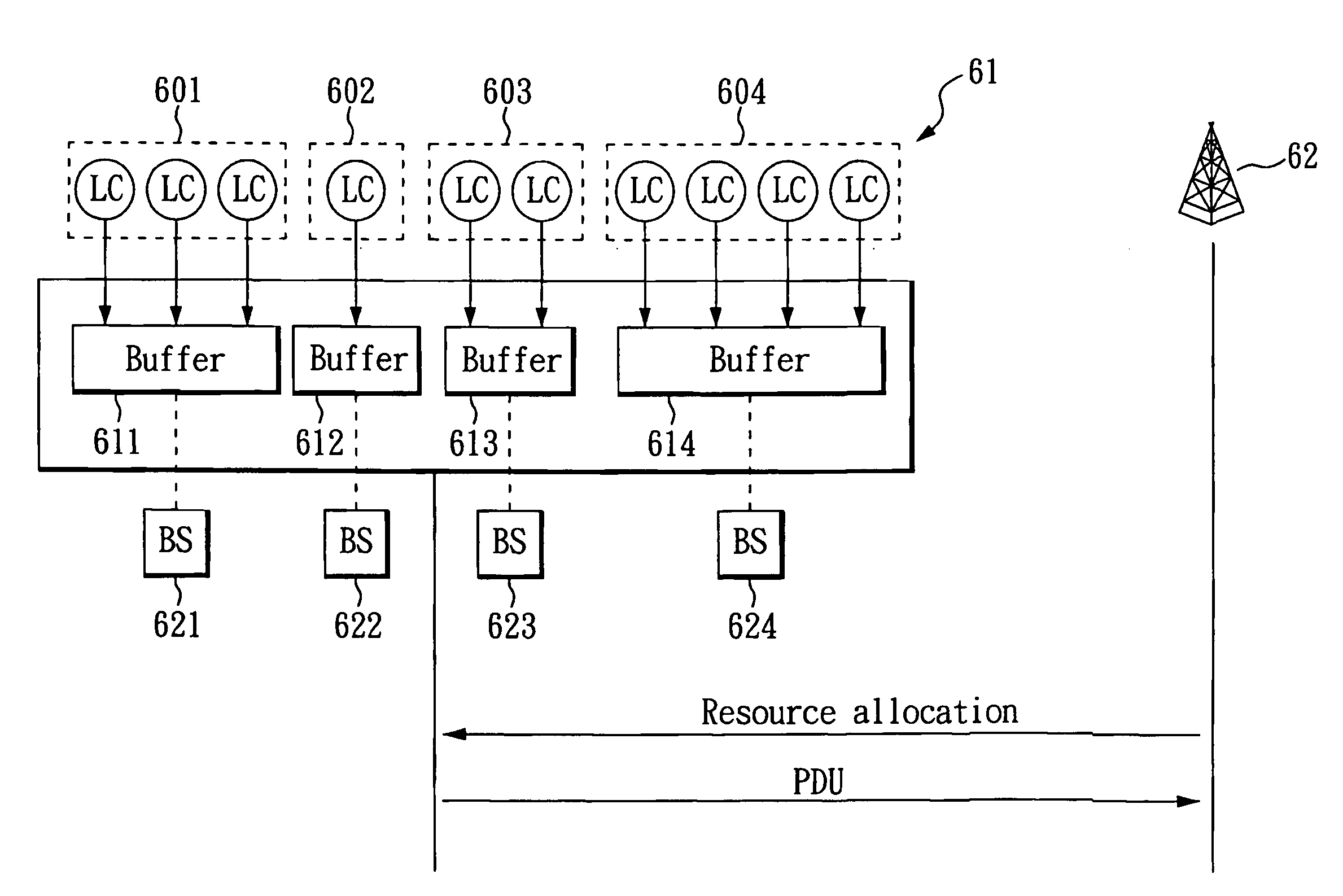

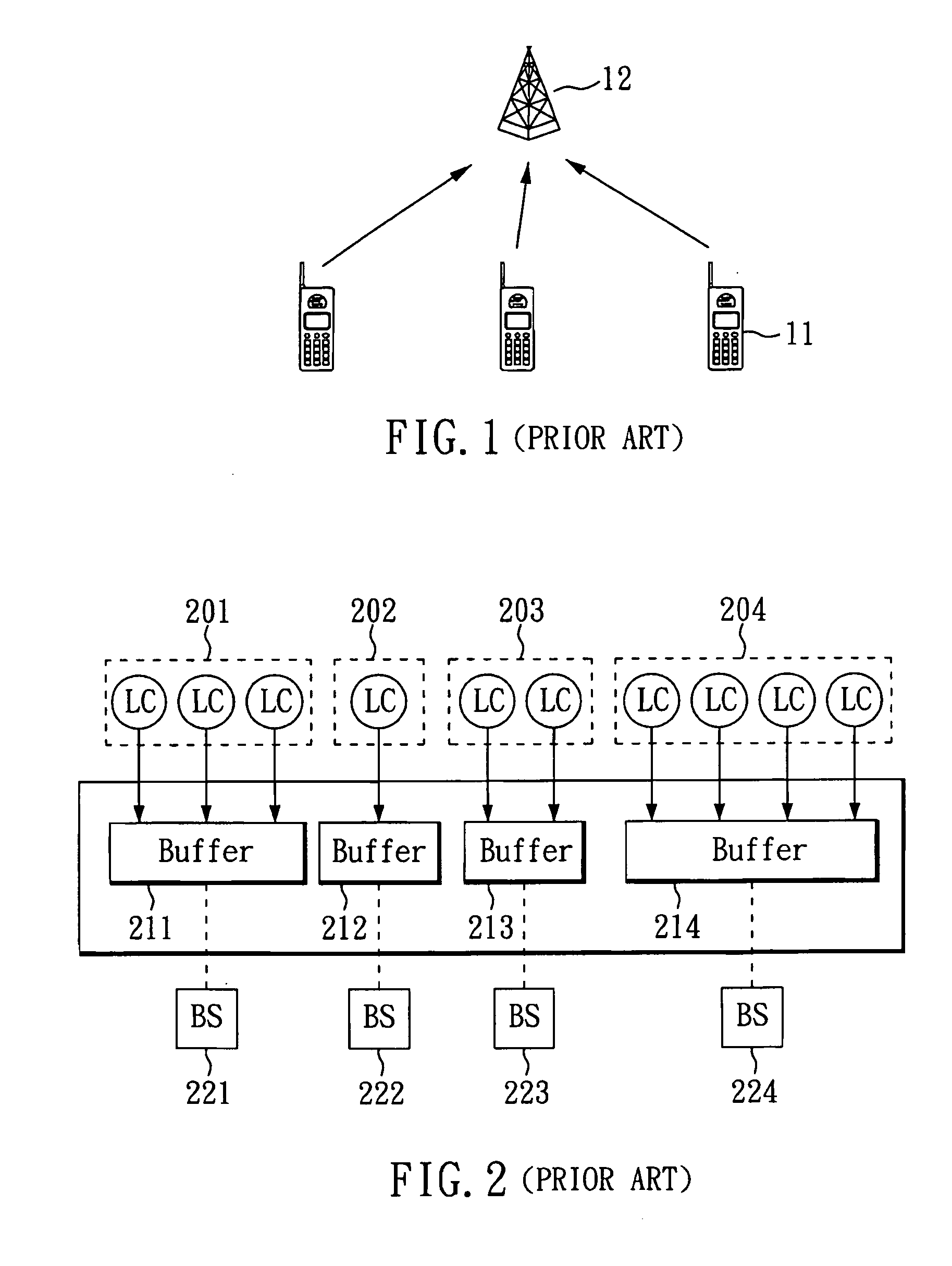

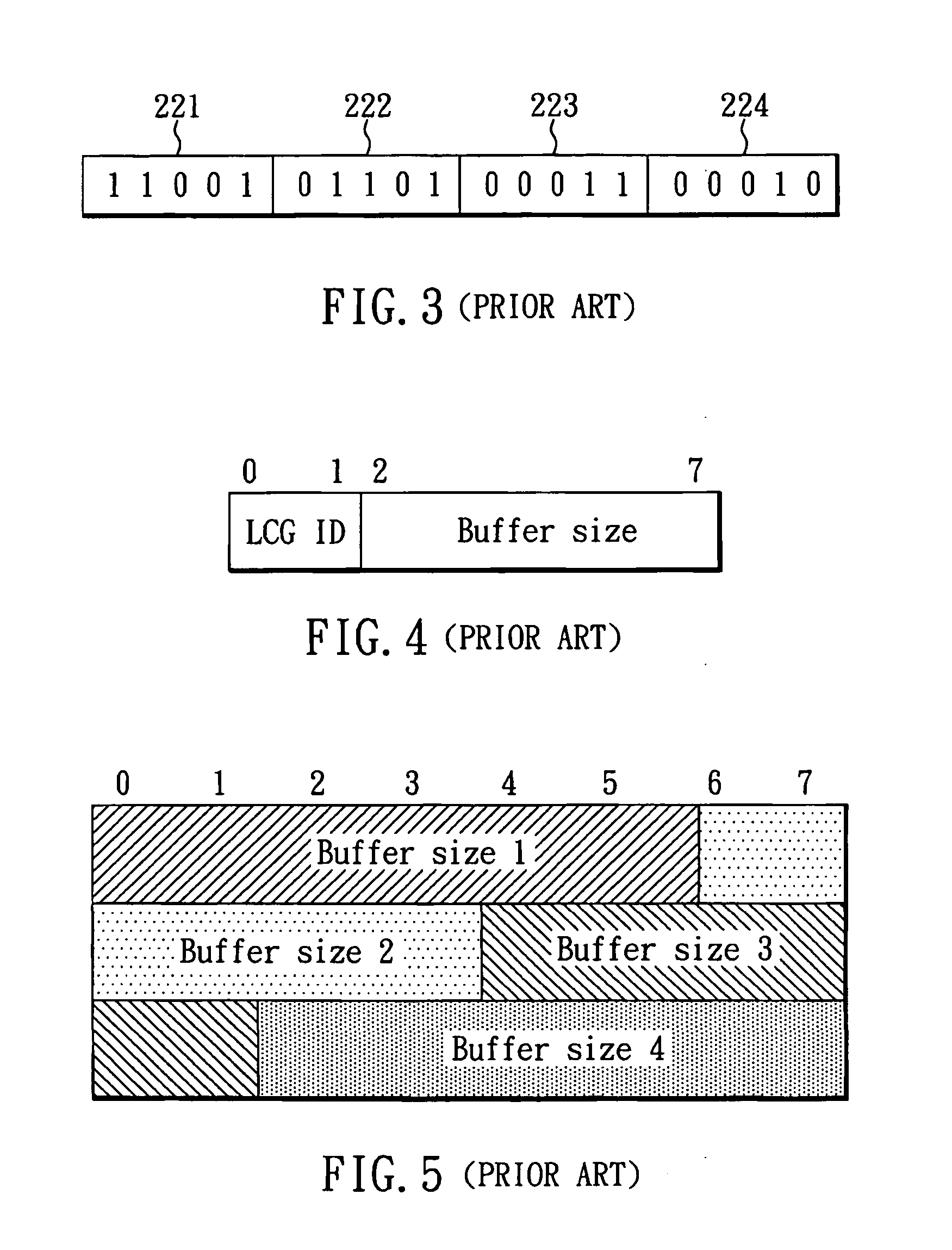

Method for providing a buffer status report in a mobile communication network

ActiveUS20090113086A1Reduce usagePrevent resource network resourceBroadcast transmission systemsTime-division multiplexComputer scienceUser equipment

A method for providing a buffer status report in a mobile communication network is implemented between a base station and a user equipment. When data arrives to buffers of the user equipment and the priority of a logical channel for the data is higher than those of other logical channels for existing data in the buffers, a short buffer status report associated with the buffer of a logical channel group corresponding to the arrival data is triggered. The user equipment is based on obtained resources allocated by the base station to fill all data of the buffer of the logical channel group in a Protocol Data Unit. If all data of the buffer of the logical channel group corresponding to the arrival data can be completely filled in the Protocol Data Unit, the short buffer status report is canceled. Otherwise, the user equipment transmits the short buffer status report.

Owner:HFI INNOVATION INC

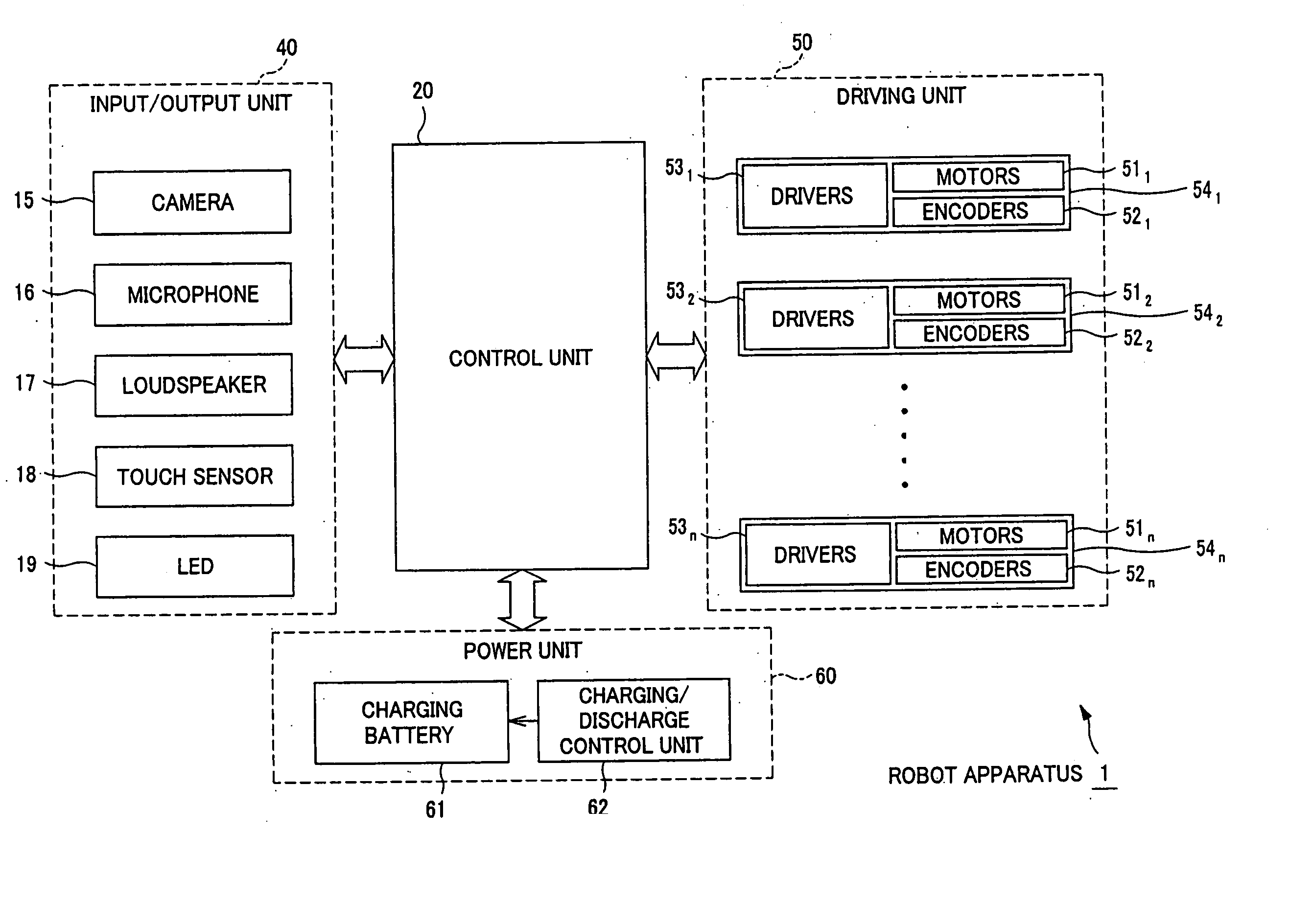

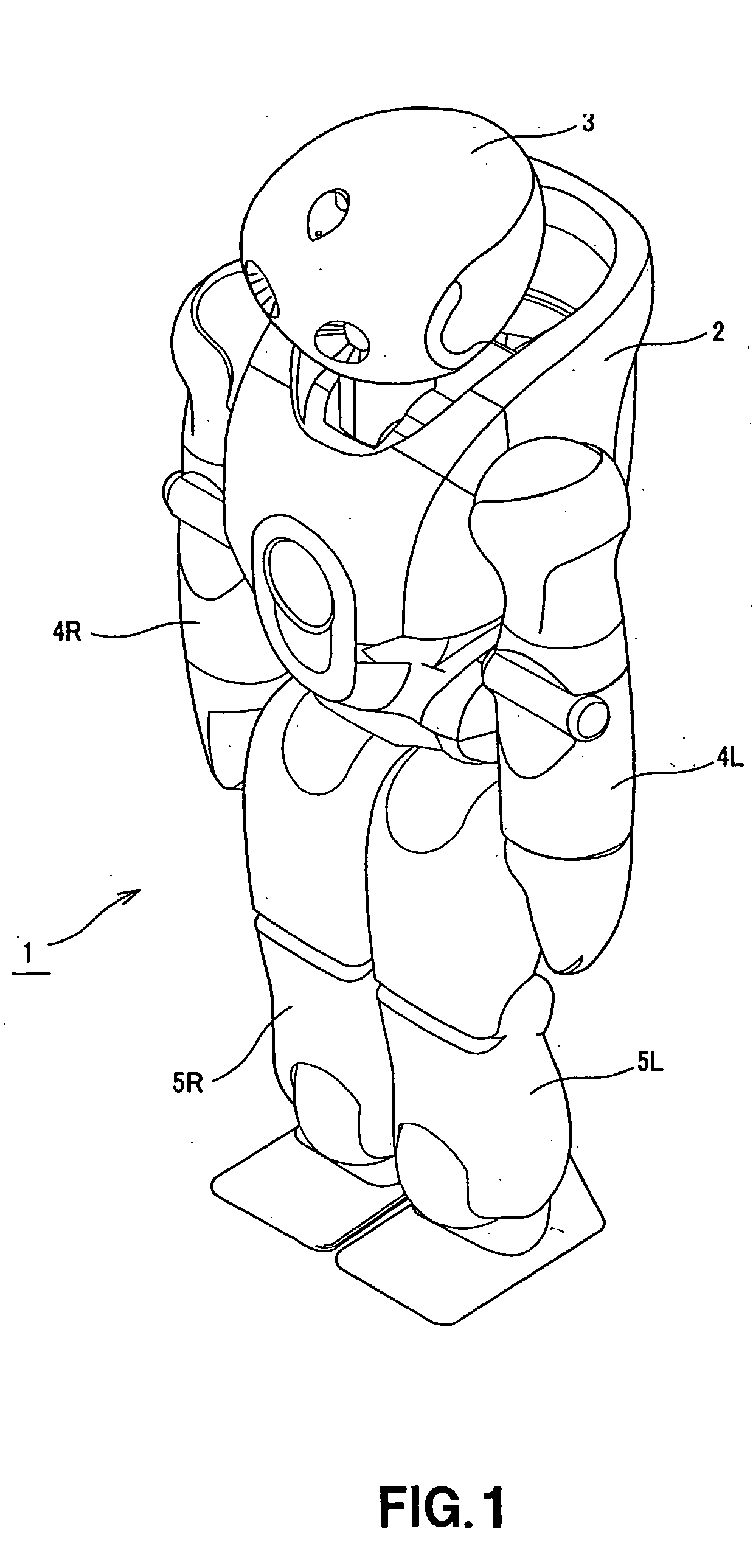

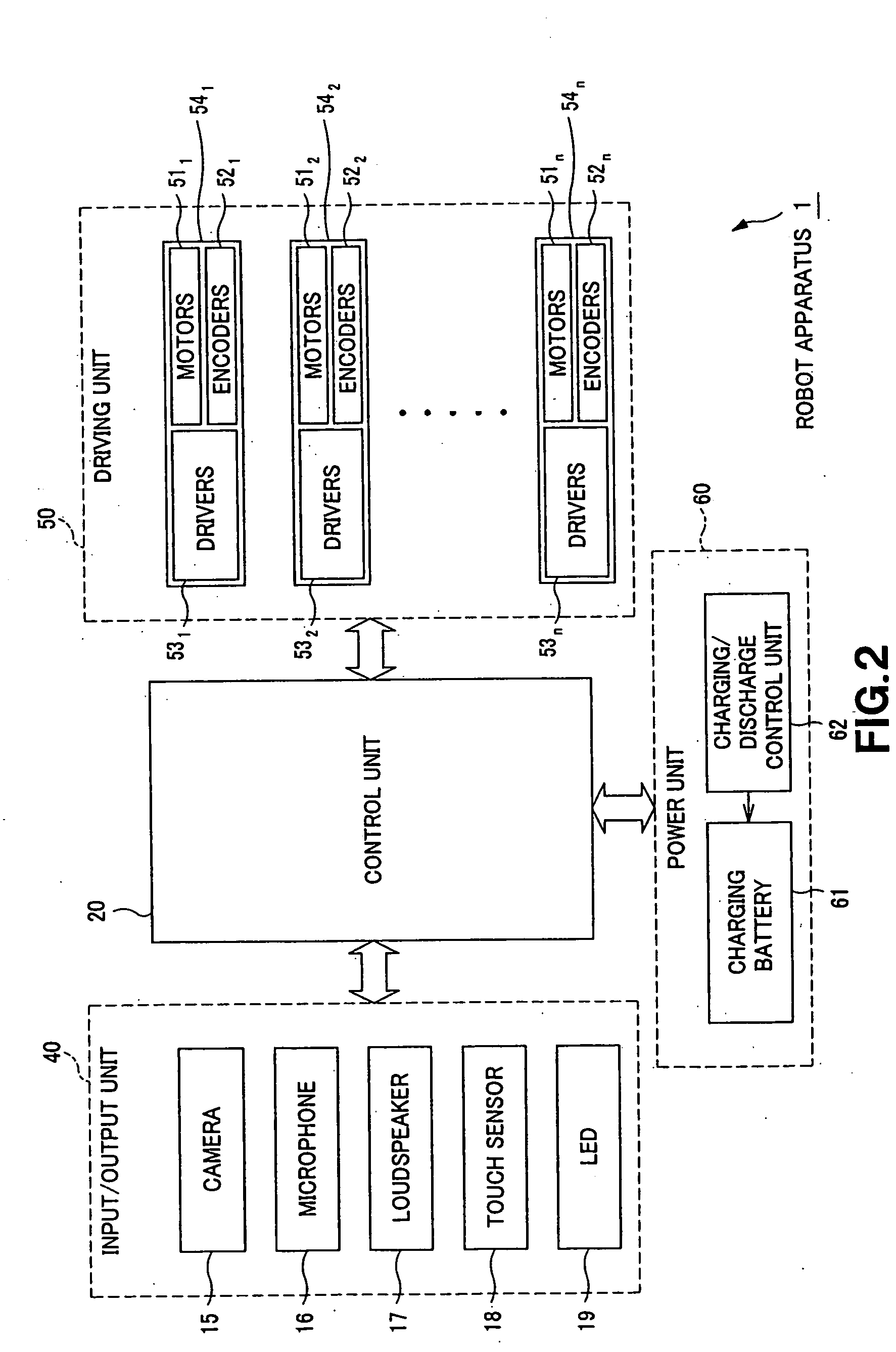

Buffer mechanism and recording and/or reproducing apparatus

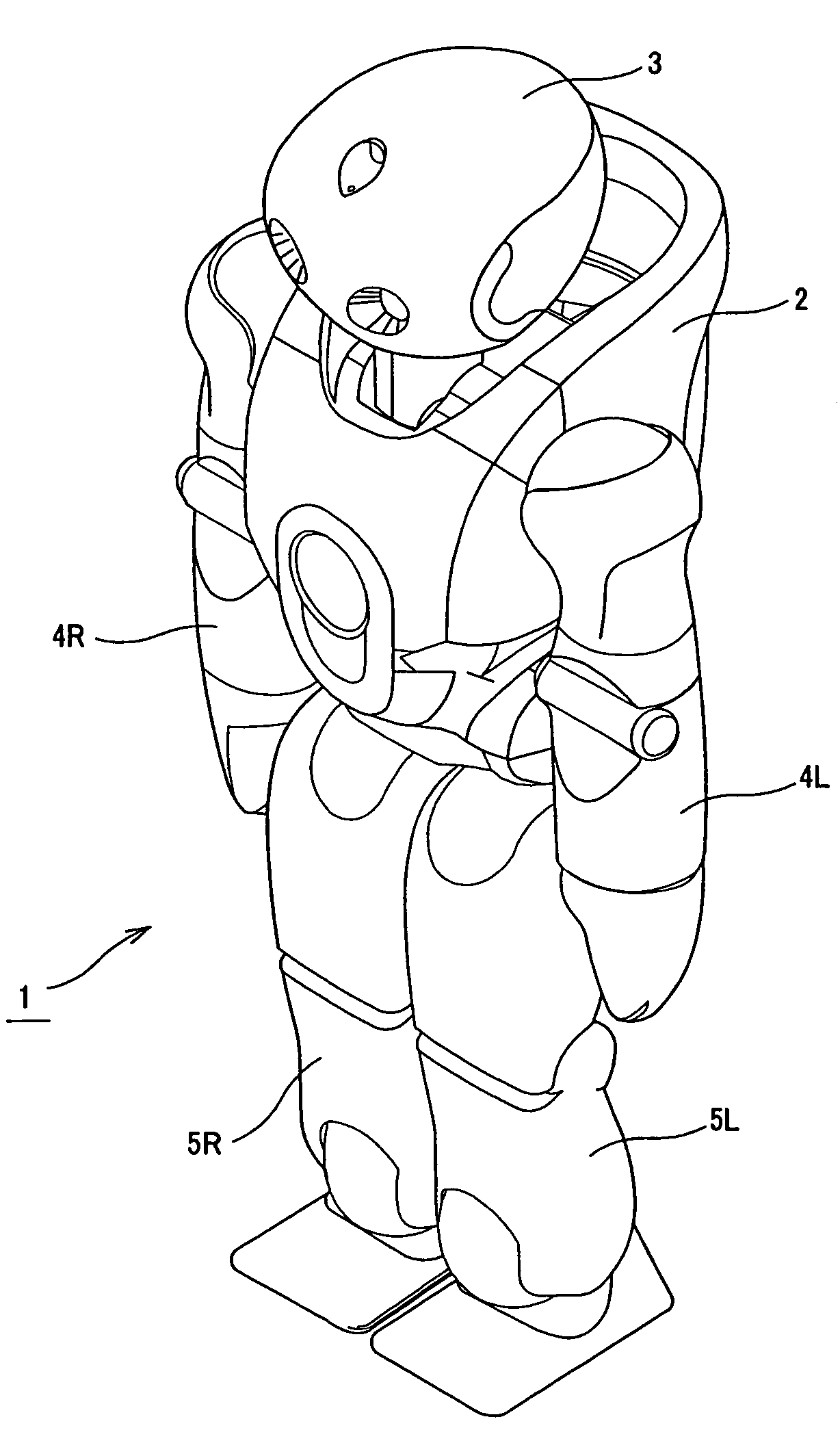

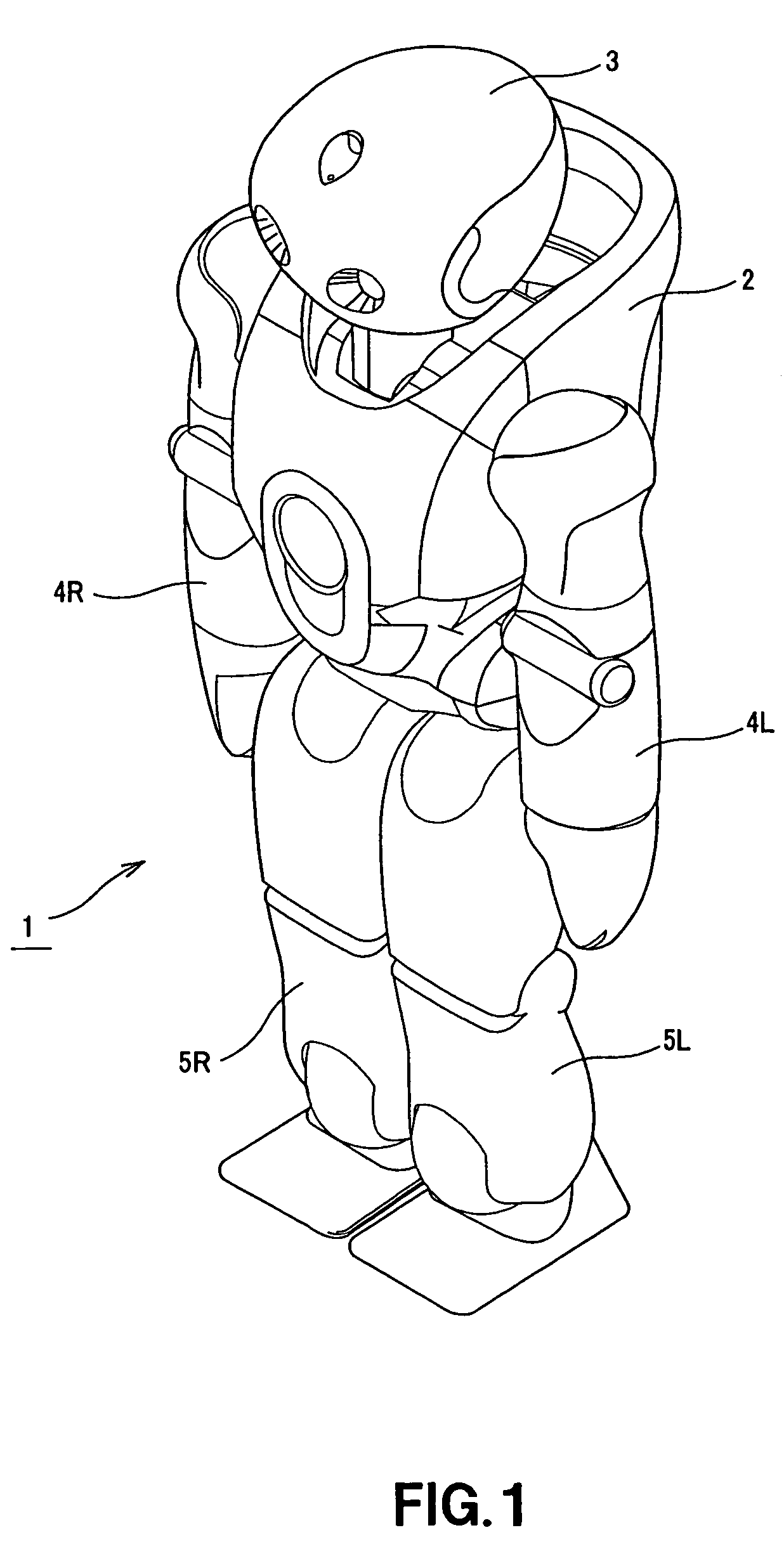

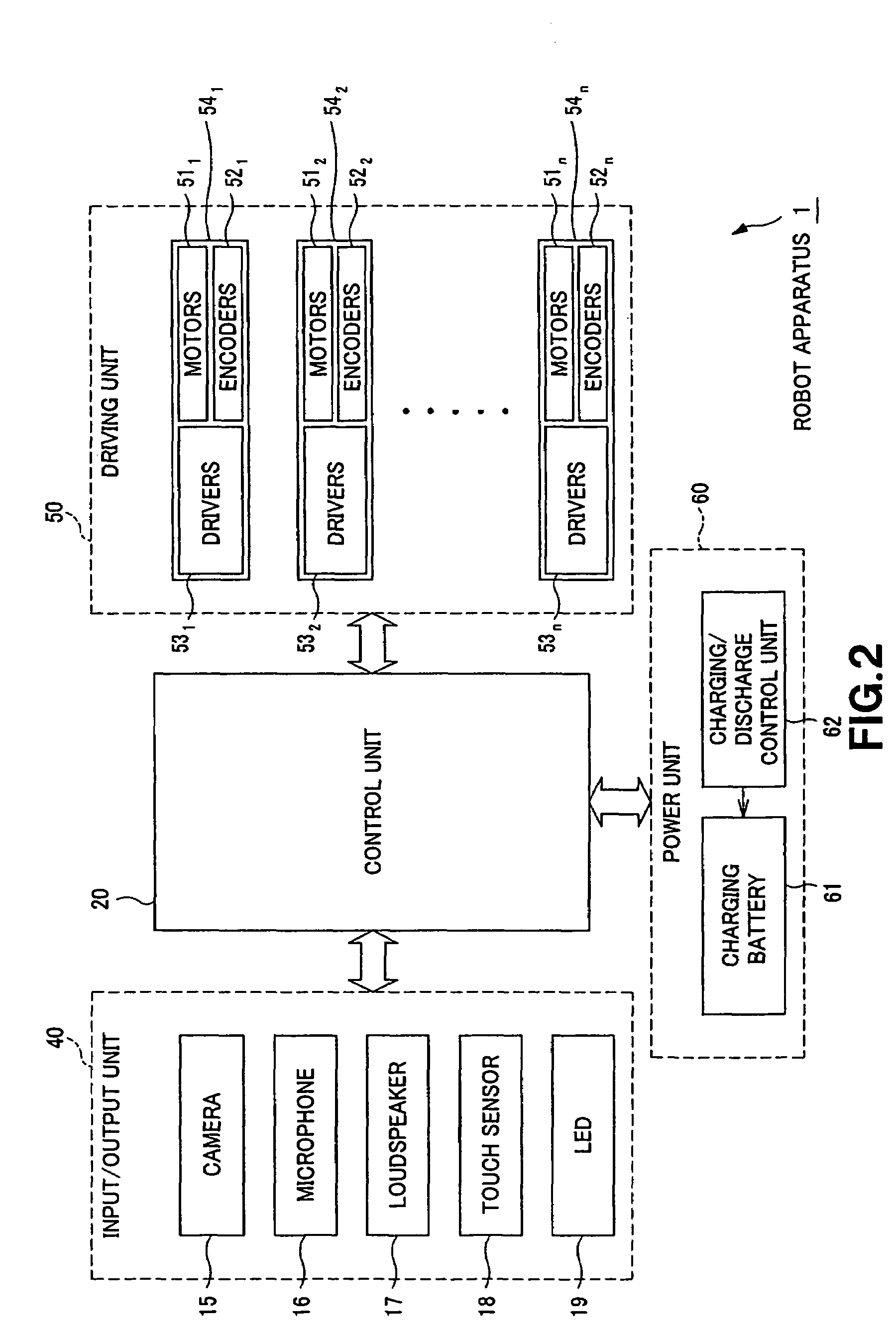

InactiveUS20040210345A1Improve efficiencySmooth communicationAutonomous decision making processSelf-moving toy figuresLimited resourcesHumanoid robot nao

A robot apparatus which, by exploiting limited resources highly efficiently, is capable of making expressions matched to the motion or to complex variegated feeling or instinct states, representing the crucial information in achieving smooth communication with the human being, is disclosed. A method of expression by the robot apparatus is also disclosed. The robot apparatus expresses plural states, such as emotional states or the processing states of perceptual recognition, by a light radiating device loaded at a location of the head part of the humanoid robot apparatus walking on two legs. The light radiating device includes e.g. the color hue, saturation and patterns of light emission as expressive units represented independently of one another. A plural number of orthogonal states, that is, the emotional states and the states of perceptual recognition, are expressed simultaneously, using a plural number of the orthogonal representations of the light radiating device correlated by a unit for correlating plural reciprocally orthogonal states, derived from the own inner states or external stimuli, with at least one expressive unit.

Owner:SONY CORP

Robot and control method for controlling robot expressions

InactiveUS7363108B2Limited resourceSmooth communicationProgramme-controlled manipulatorAutonomous decision making processLimited resourcesHumanoid robot nao

A robot apparatus which, by exploiting limited resources highly efficiently, is capable of making expressions matched to the motion or to complex variegated feeling or instinct states, representing the crucial information in achieving smooth communication with the human being, is disclosed. A method of expression by the robot apparatus is also disclosed. The robot apparatus expresses plural states, such as emotional states or the processing states of perceptual recognition, by a light radiating device loaded at a location of the head part of the humanoid robot apparatus walking on two legs. The light radiating device includes e.g. the color hue, saturation and patterns of light emission as expressive units represented independently of one another. A plural number of orthogonal states, that is, the emotional states and the states of perceptual recognition, are expressed simultaneously, using a plural number of the orthogonal representations of the light radiating device correlated by a unit for correlating plural reciprocally orthogonal states, derived from the own inner states or external stimuli, with at least one expressive unit.

Owner:SONY CORP

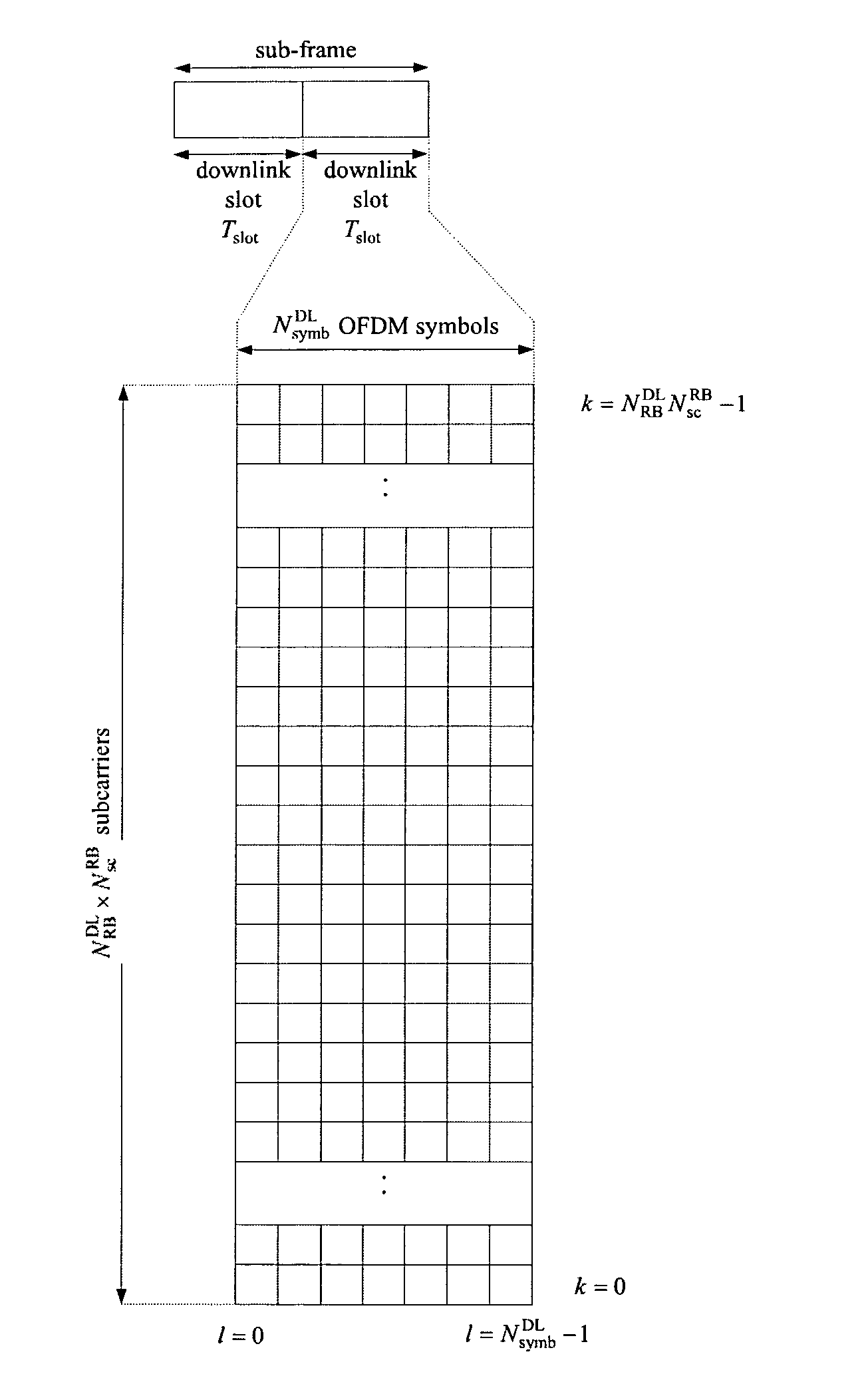

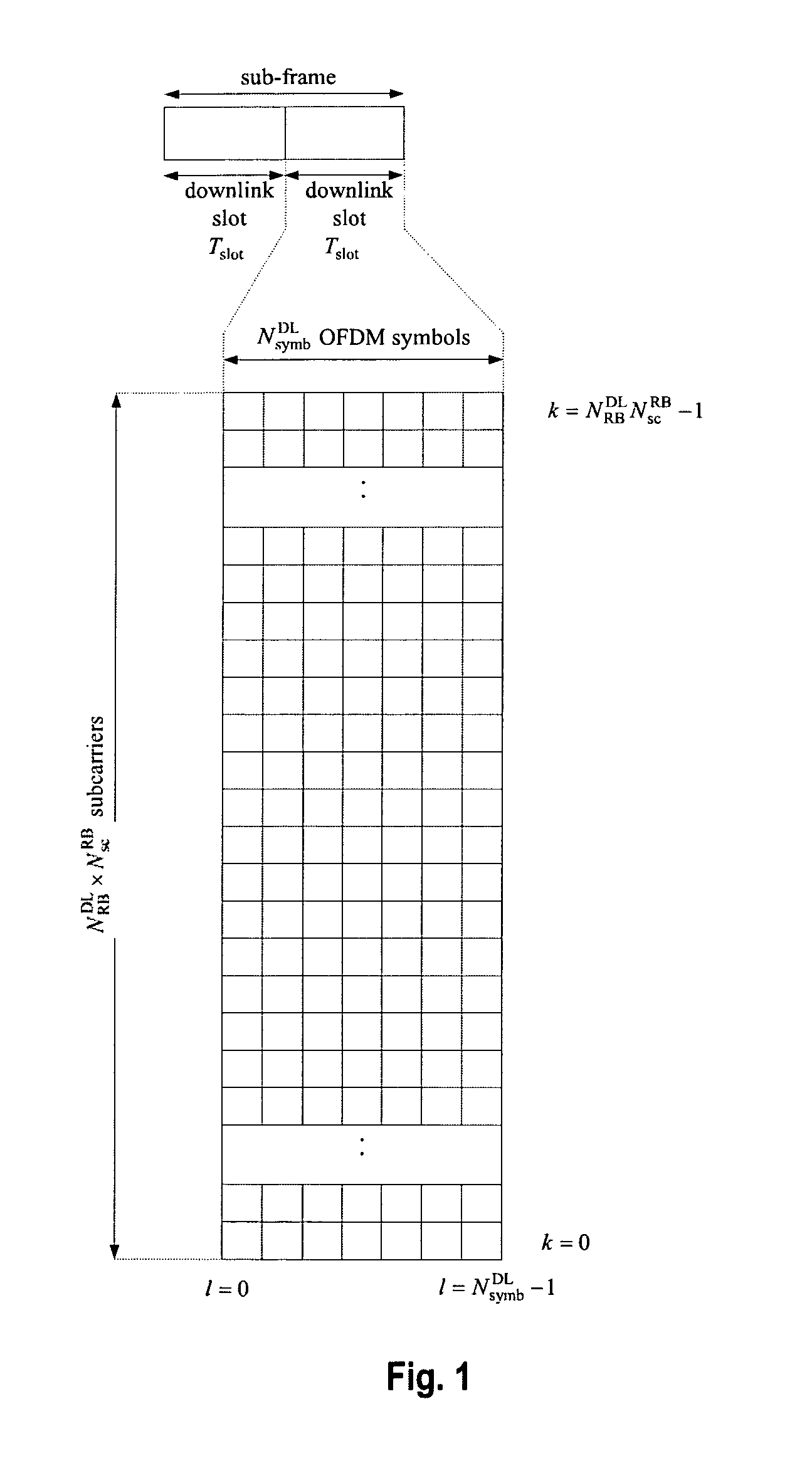

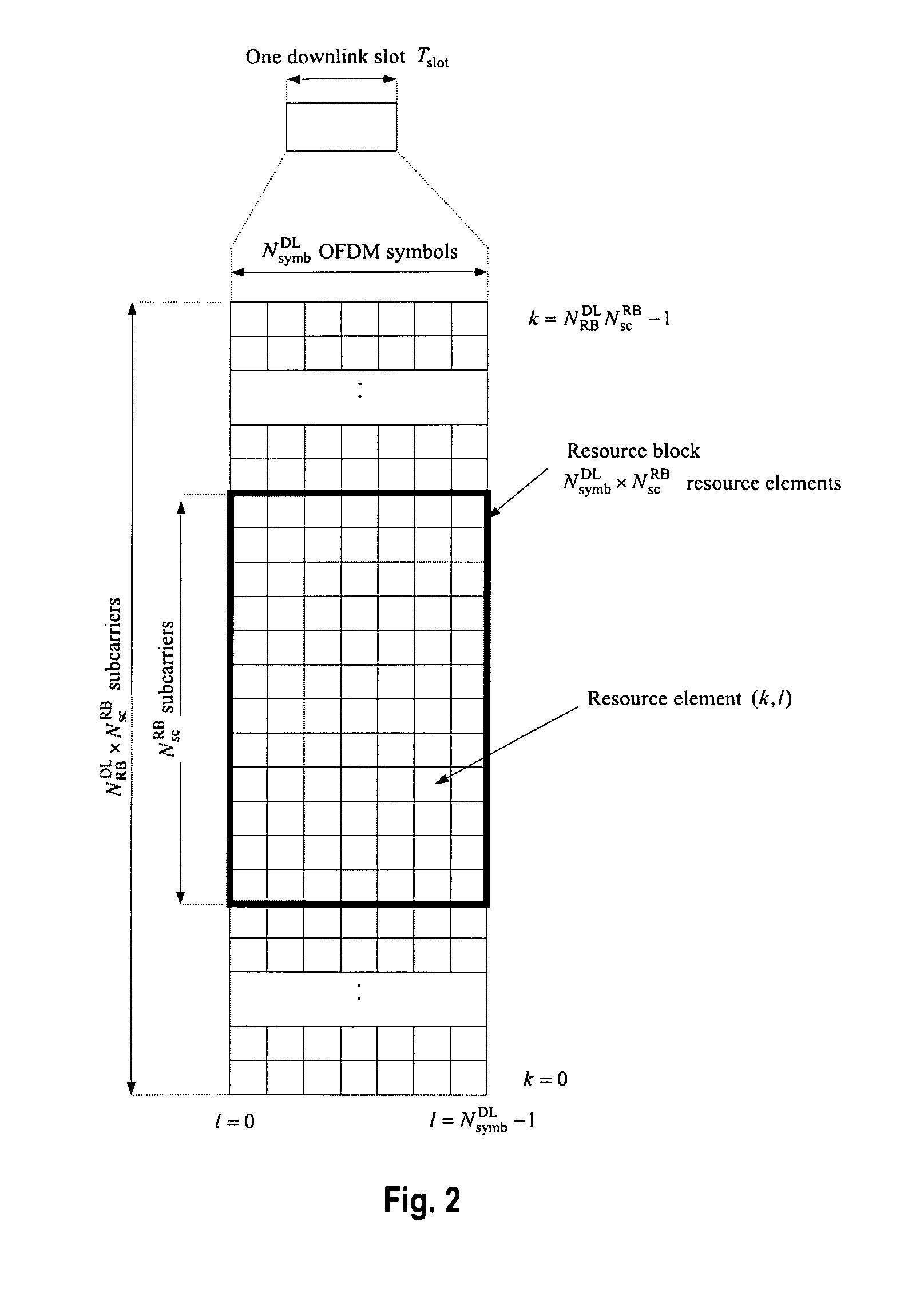

Mapping of control information to control channel elements

ActiveUS20130223402A1Increase system bandwidthWider transmission bandwidthTransmission path divisionSignal allocationTime domainCommunications system

The invention relates to a new structure of a control channel region within a sub-frame of a 3GPP-based based communication system using OFDM in the downlink. This new structure of a control channel region is inter alia particularly suitable for conveying physical downlink control channel information from a donor eNodeB to a relay node. The control channel region is divided in CCEs that have equal size irrespective of the presence of further cell-specific and / or UE-specific reference signals within the control channel region. This is achieved by dividing the control channel region in plural sub-CCEs that are combined to CCEs all having equal size (in terms of resource elements that can be used for the signaling of control information). The control channel region is divided in the frequency domain and / or time domain in a FDM respectively TDM fashion in order to obtain the sub-CCEs

Owner:SUN PATENT TRUST

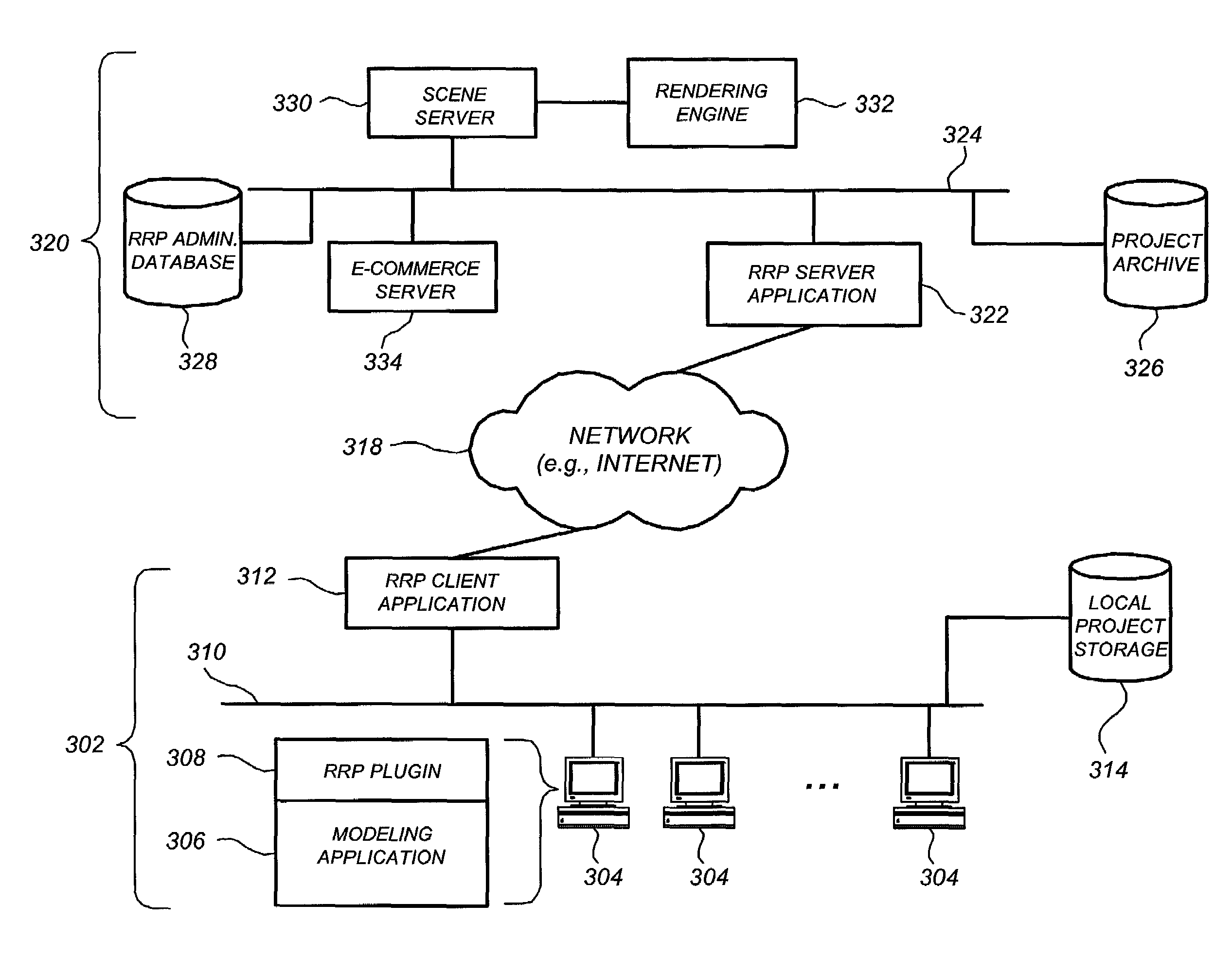

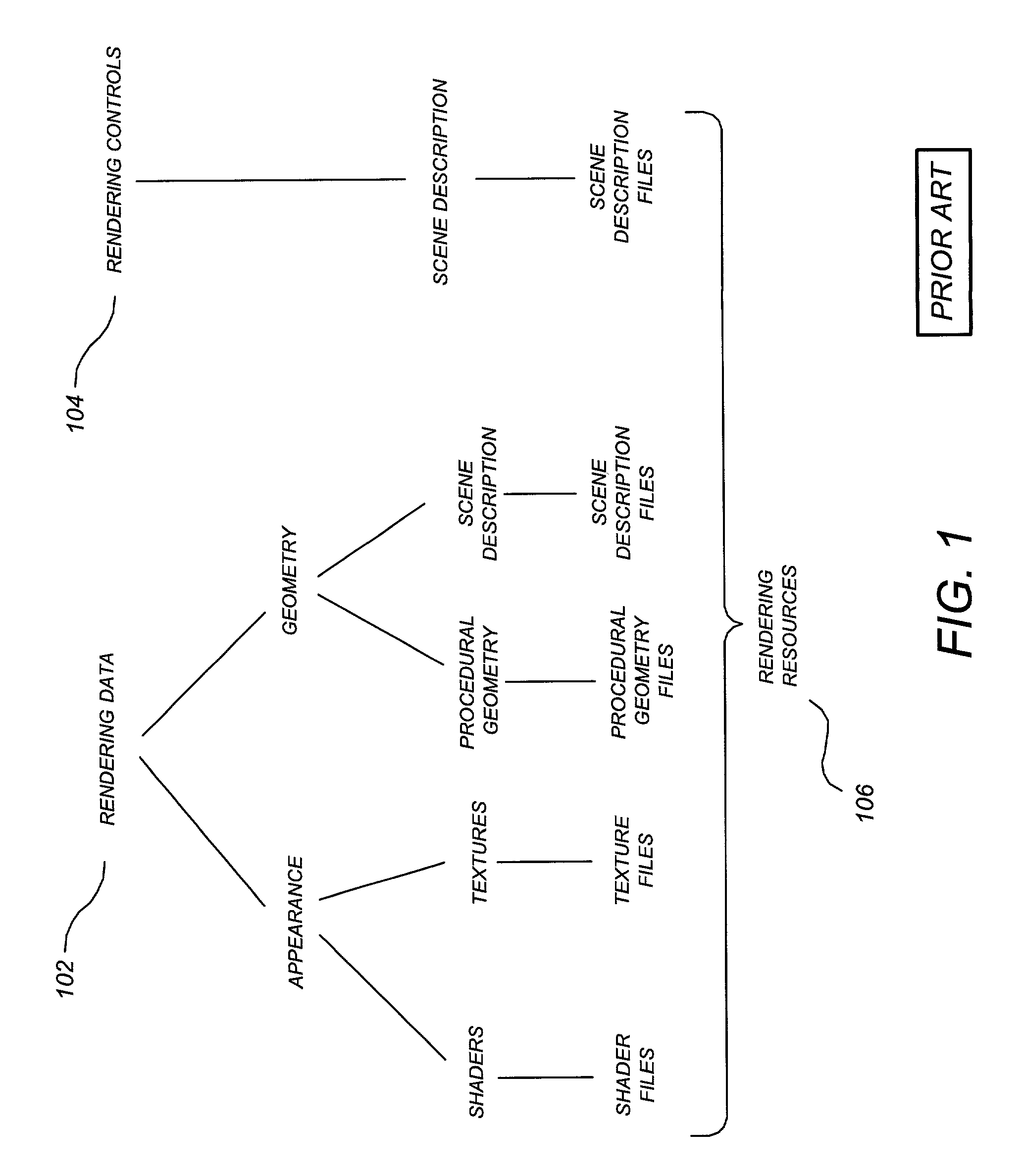

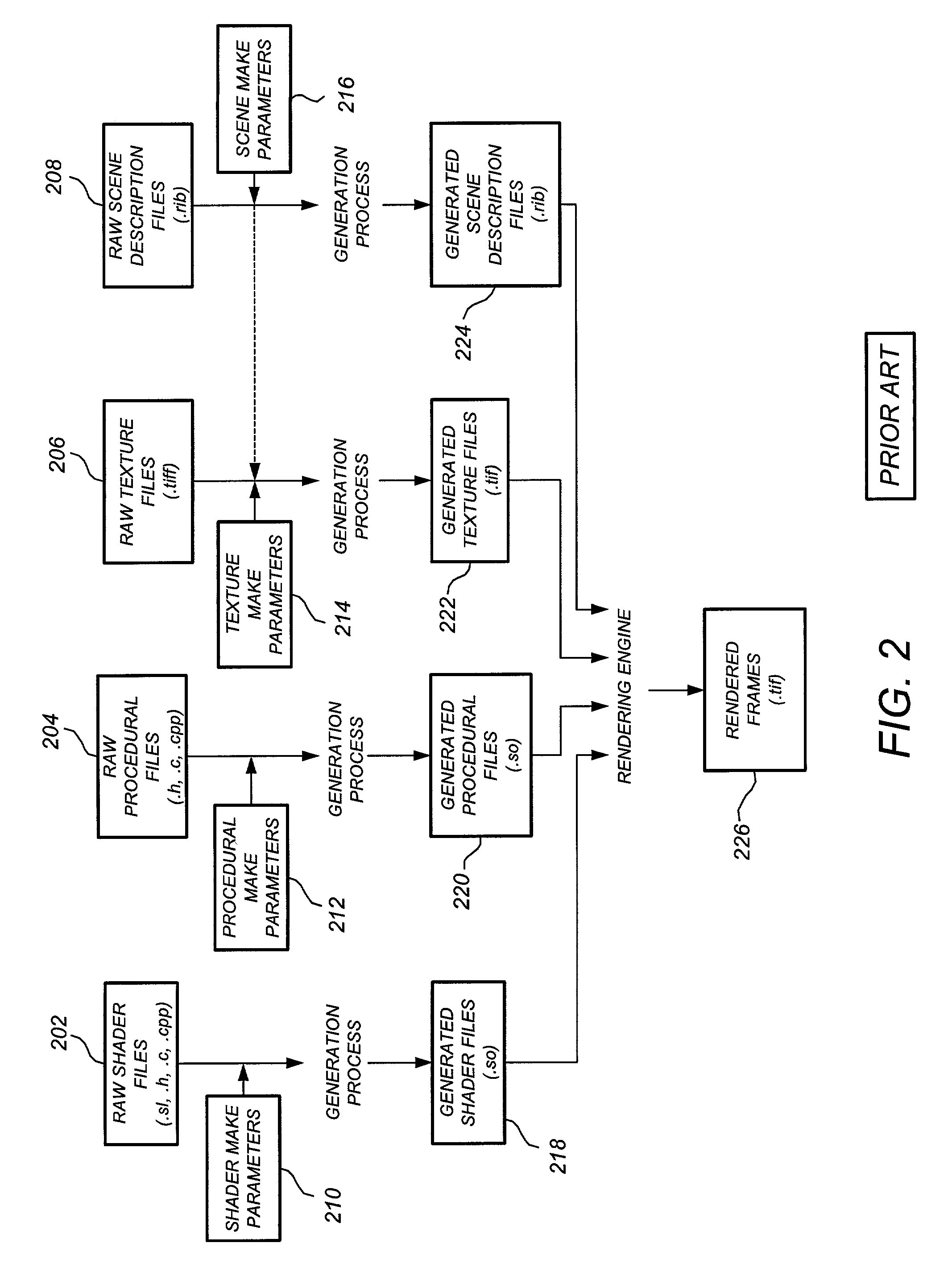

Method and system for digital rendering over a network

InactiveUS7266616B1BandwidthSave bandwidthMultiple digital computer combinationsImage data processing detailsClient-sideResource pool

Digital rendering over a network is described. Rendering resources associated with a project are stored in a project resource pool at a rendering service site, and for each rendering request received from a client site the project resource pool is compared to current rendering resources at the client site. A given rendering resource is uploaded from the client site to the rendering service only if the project resource pool does not contain the current version, thereby conserving bandwidth. In one embodiment, redundant generation of raw rendering resource files is avoided by only generating those raw rendering resource files not mated with generated rendering resource files. Reducing redundant generation of raw resources is also described, as well as statistically reducing the number of raw resource files required to be uploaded to the rendering service for multi-frame sessions.

Owner:DATACLOUD TECH LLC

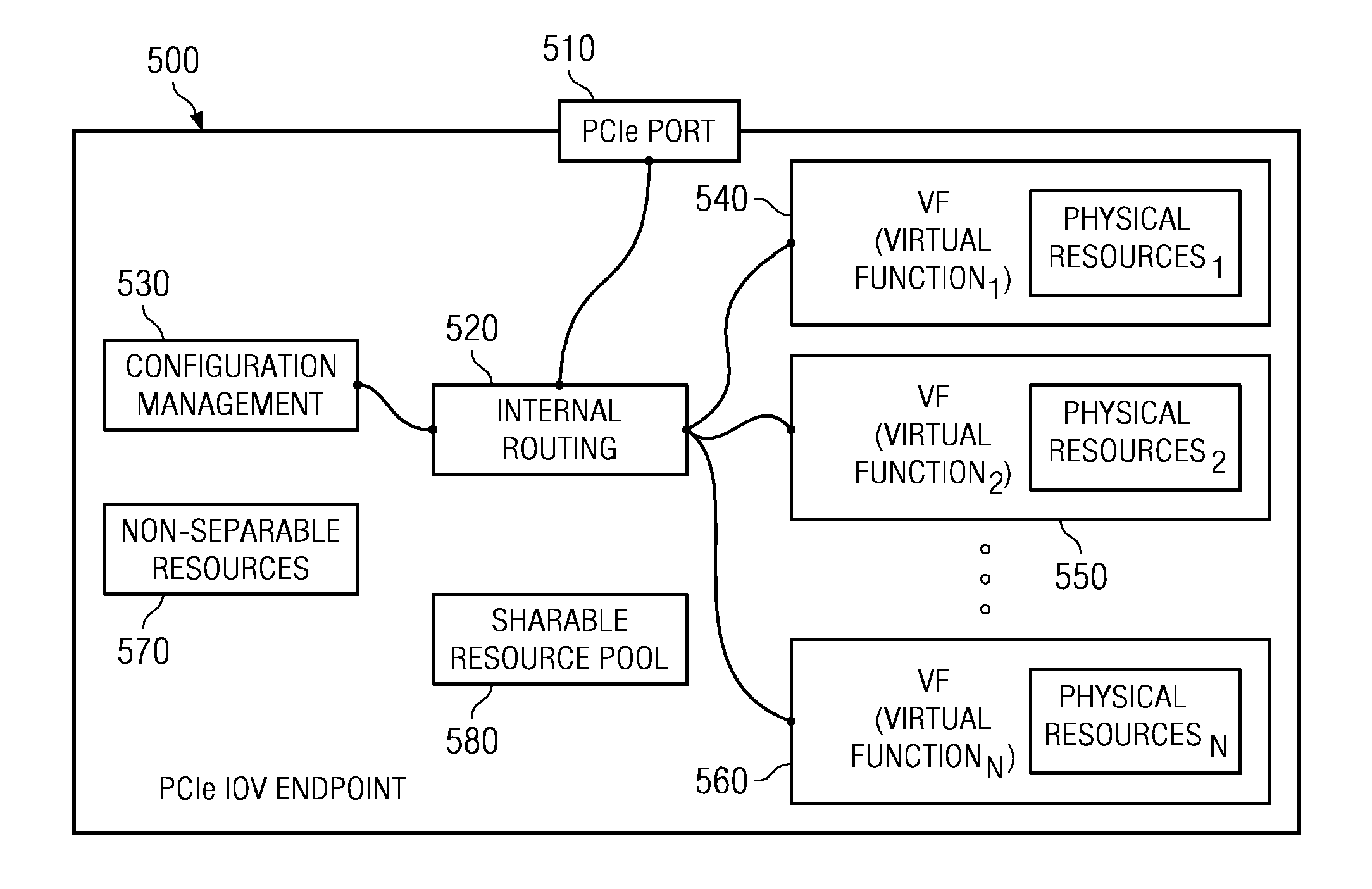

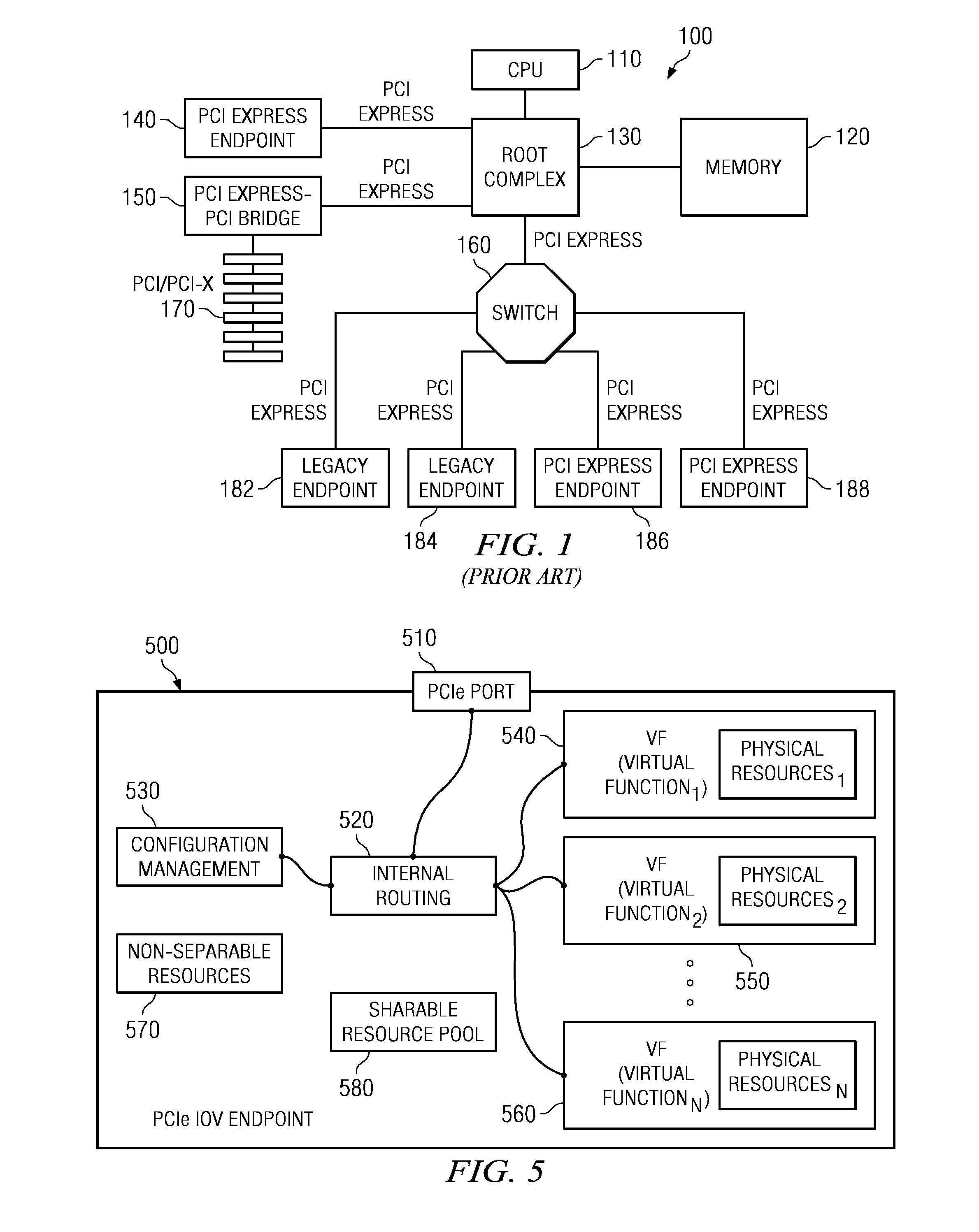

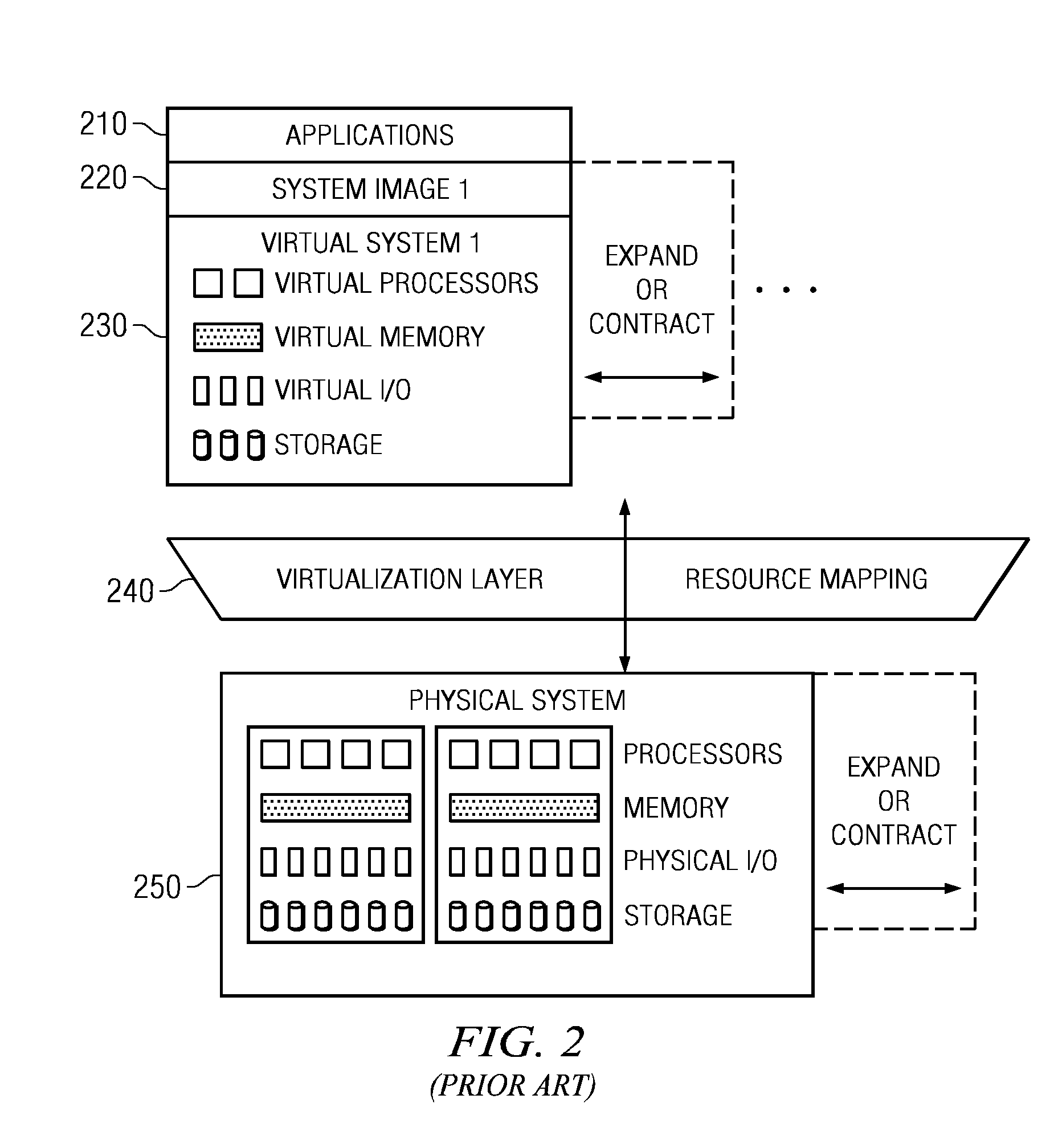

System and method for management of an iov adapter through a virtual intermediary in a hypervisor with functional management in an iov management partition

ActiveUS20090133028A1Avoid resourcesMultiprogramming arrangementsSoftware simulation/interpretation/emulationCapability managementFunctional management

A system and method which provide a mechanism for an I / O virtualization management partition (IMP) to control the shared functionality of an I / O virtualization (IOV) enabled I / O adapter (IOA) through a physical function (PF) of the IOA while the virtual functions (VFs) are assigned to client partitions for normal I / O operations directly. A hypervisor provides device-independent facilities to the code running in the IMP and client partitions. The IMP may include device specific code without the hypervisor needing to sacrifice its size, robustness, and upgradeability. The hypervisor provides the virtual intermediary functionally for the sharing and control of the IOA's control functions.

Owner:IBM CORP

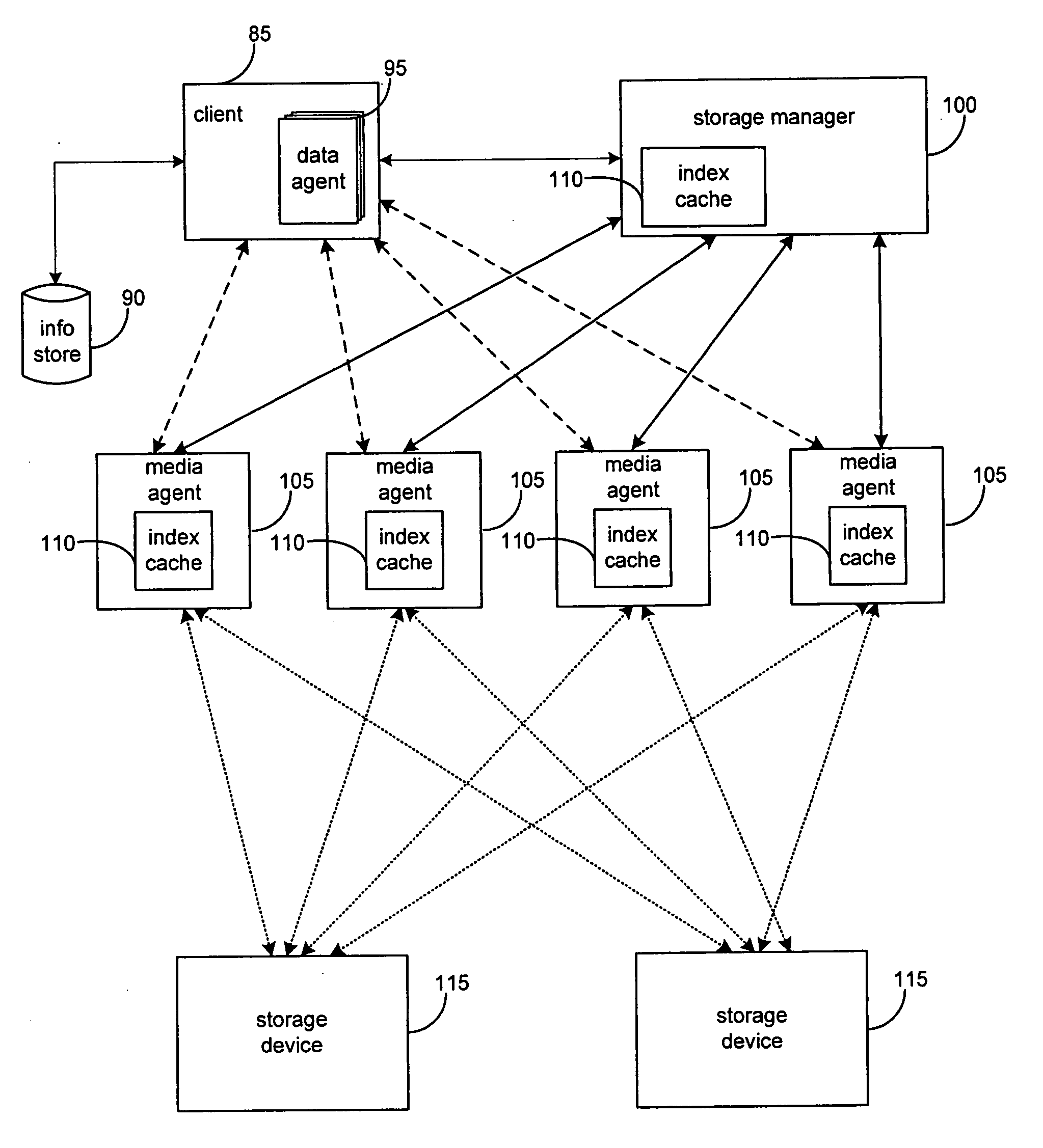

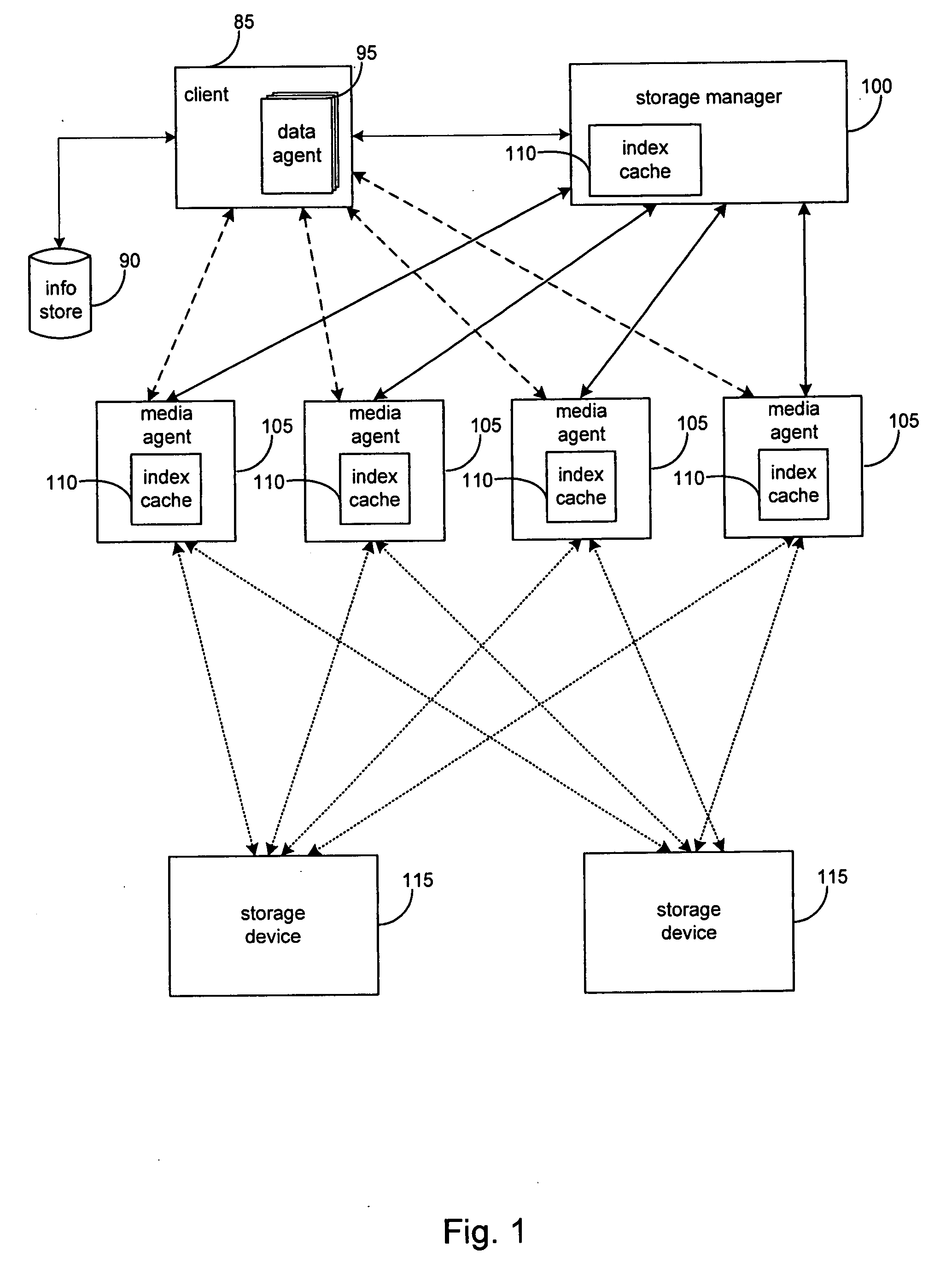

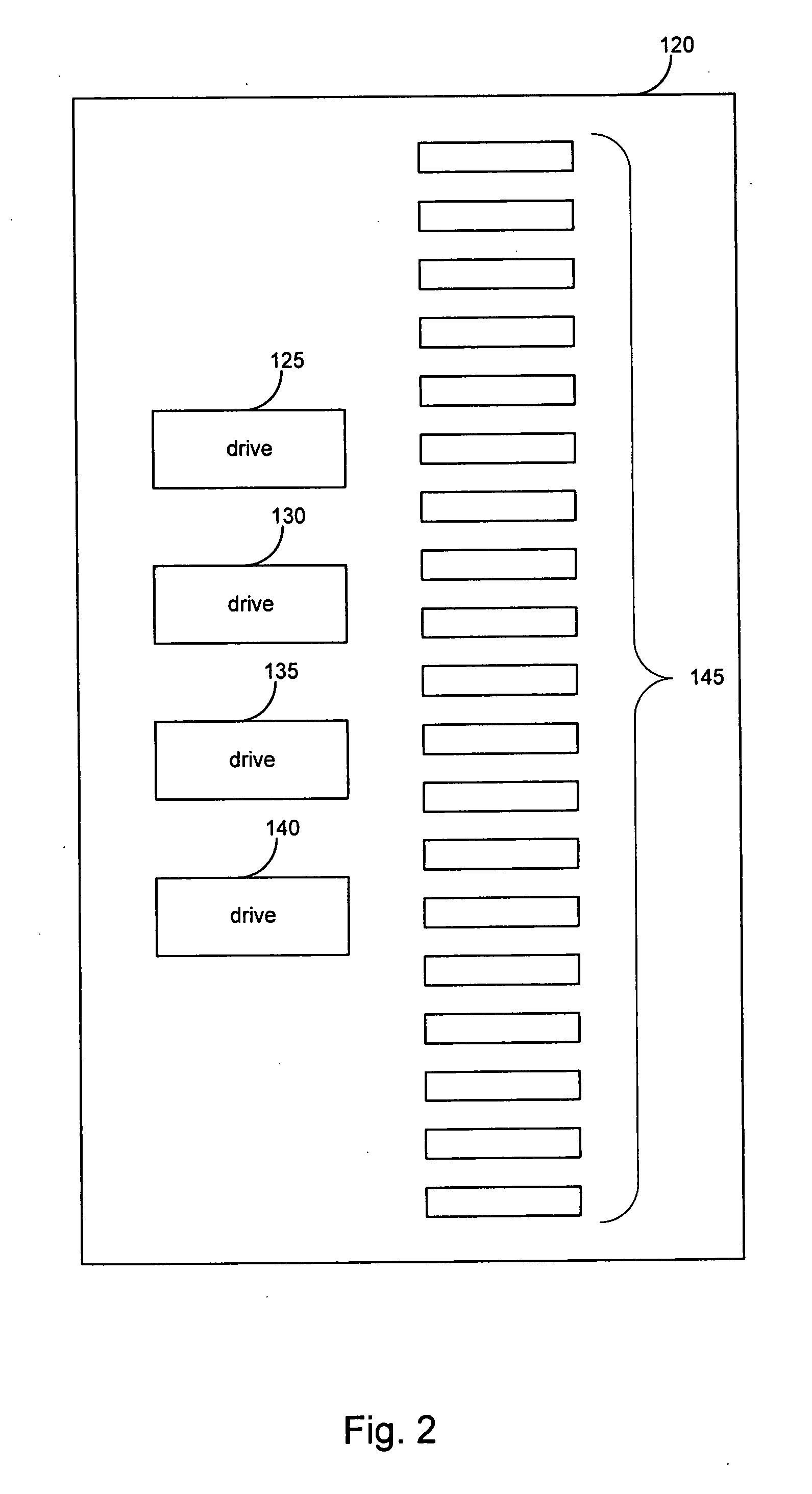

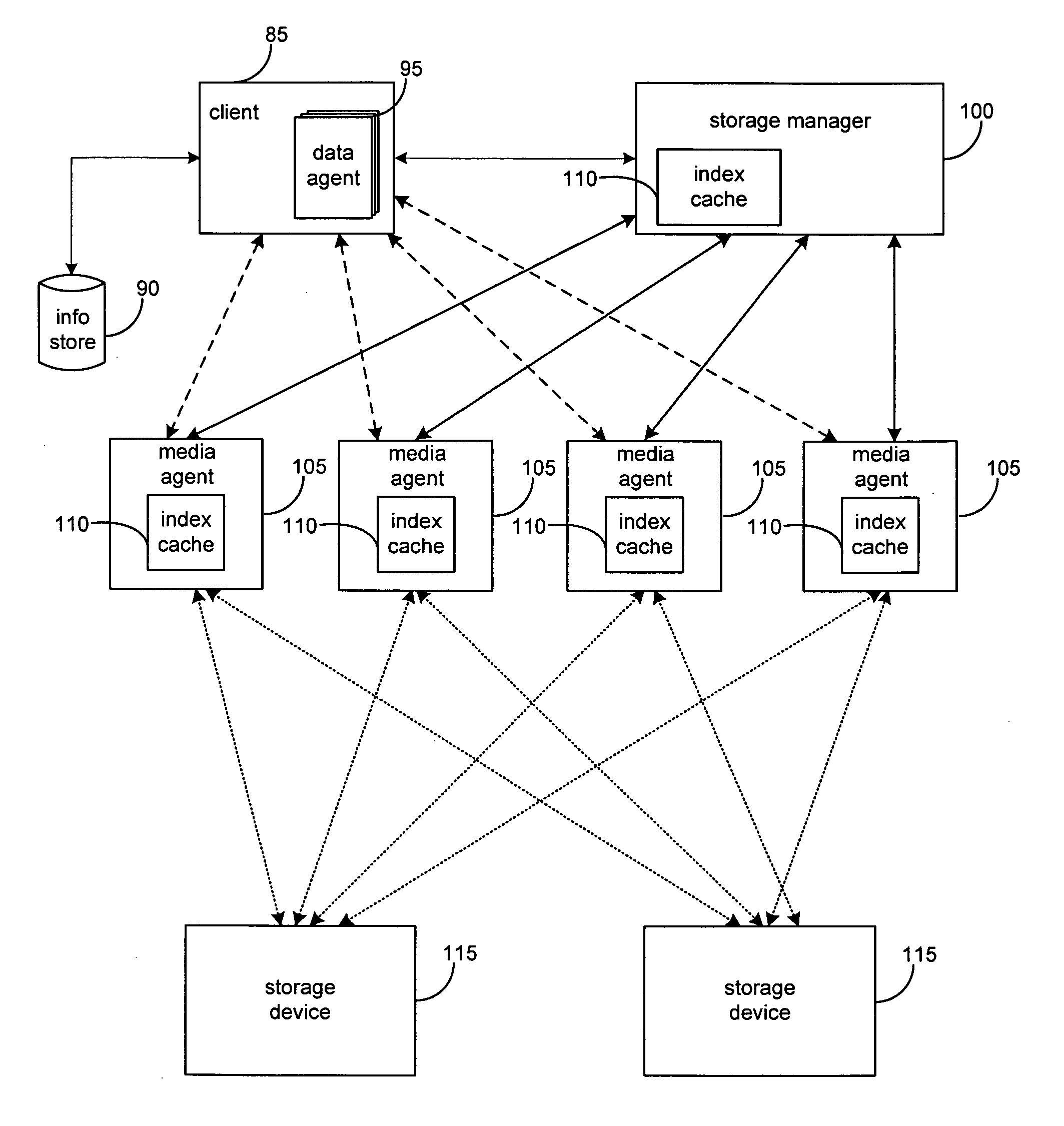

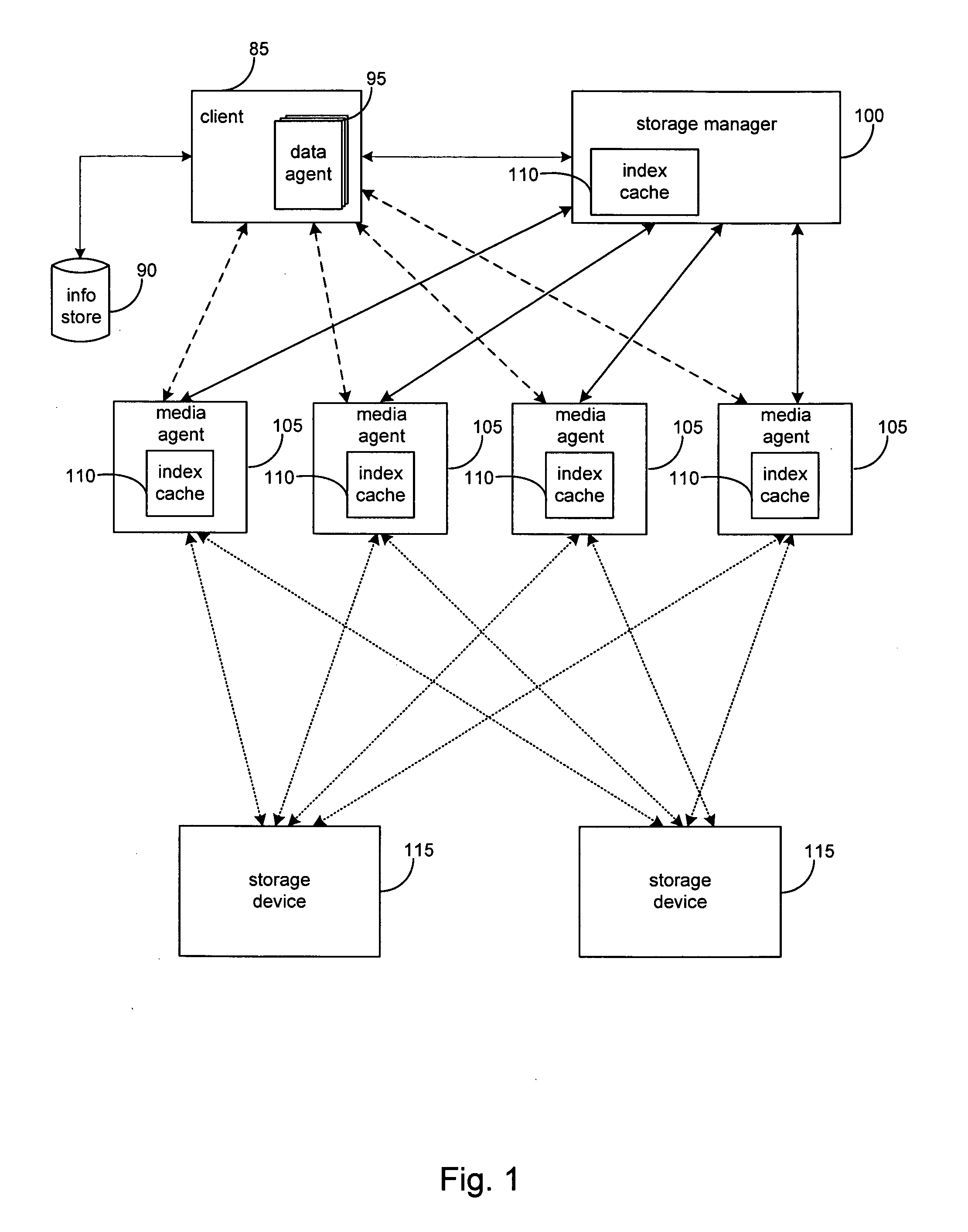

System and methods for granular resource management in a storage network

InactiveUS20080147878A1Improve performanceImprove system reliabilityDigital data information retrievalMultiple digital computer combinationsResource managementDatapath

In accordance with some aspects of the present invention, systems and methods are provided for dynamically and / or automatically selecting and / or modifying data path definitions that are used in performing storage operations on data. Alternate data paths may be specified or selected that use some or all resources that communicate with a particular destination to improve system reliability and performance. The system may also dynamically monitor and choose data path definitions to optimize system performance, conserve storage media and promote balanced load distribution.

Owner:KOTTOMTHARAYIL RAJIV +2

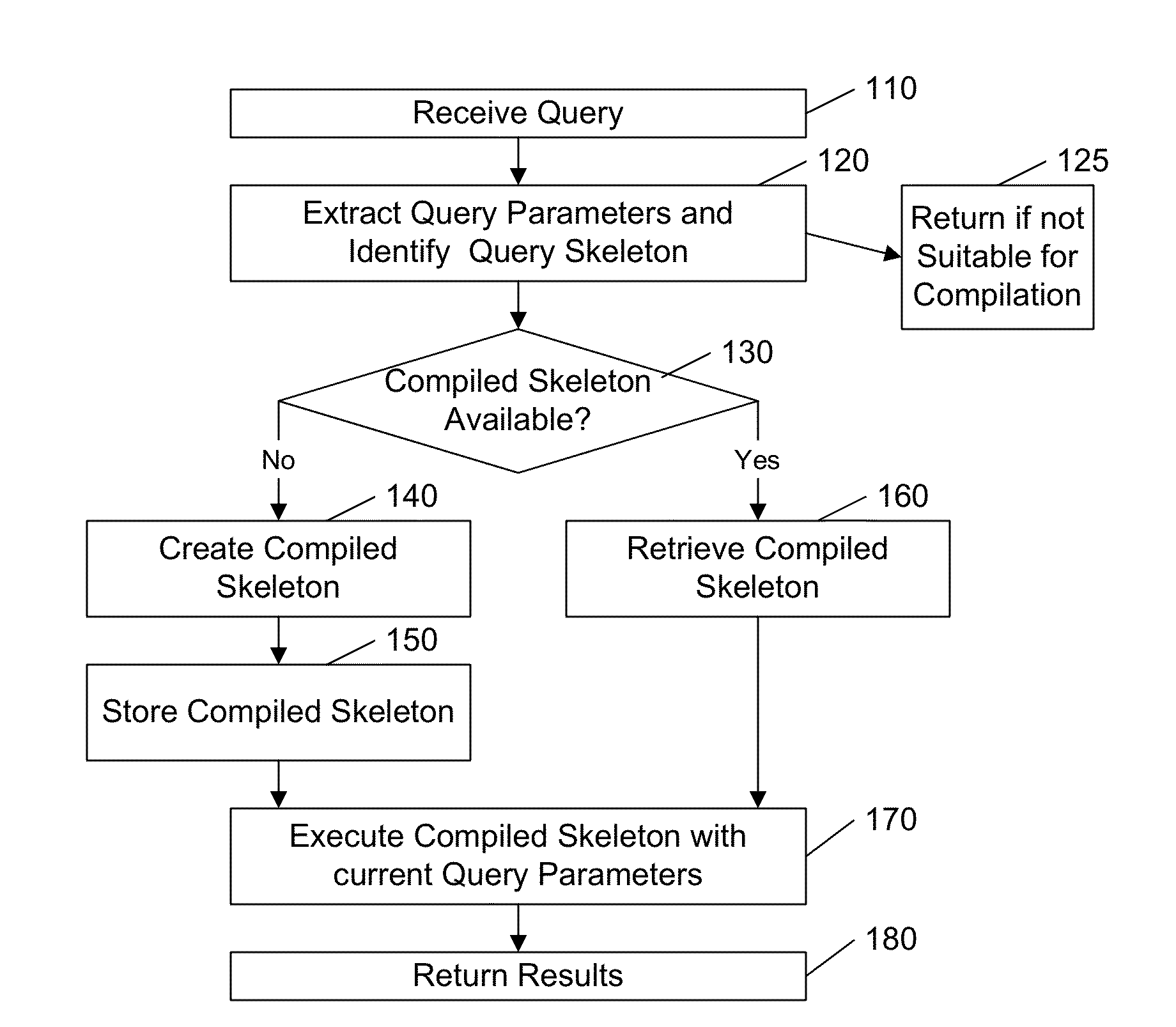

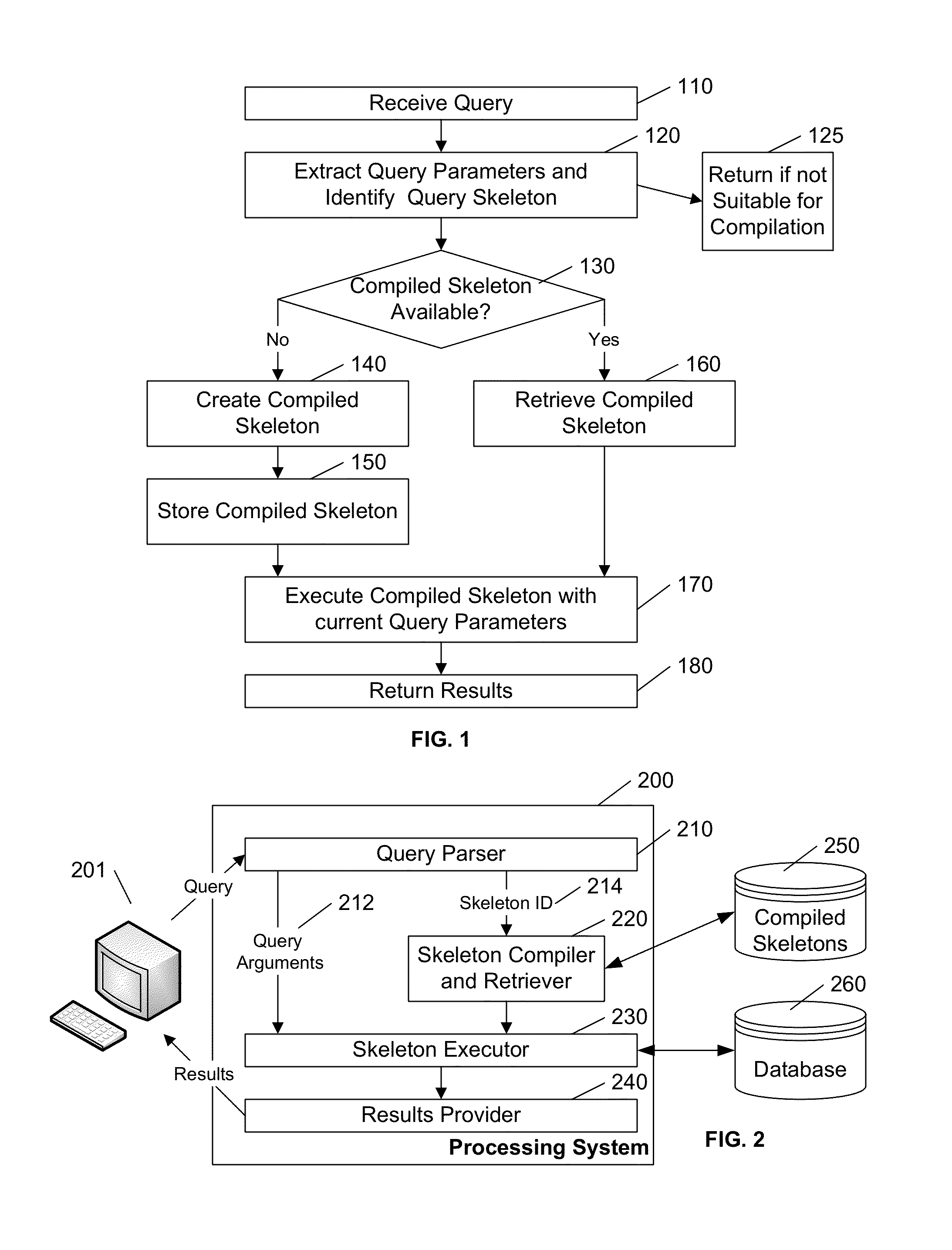

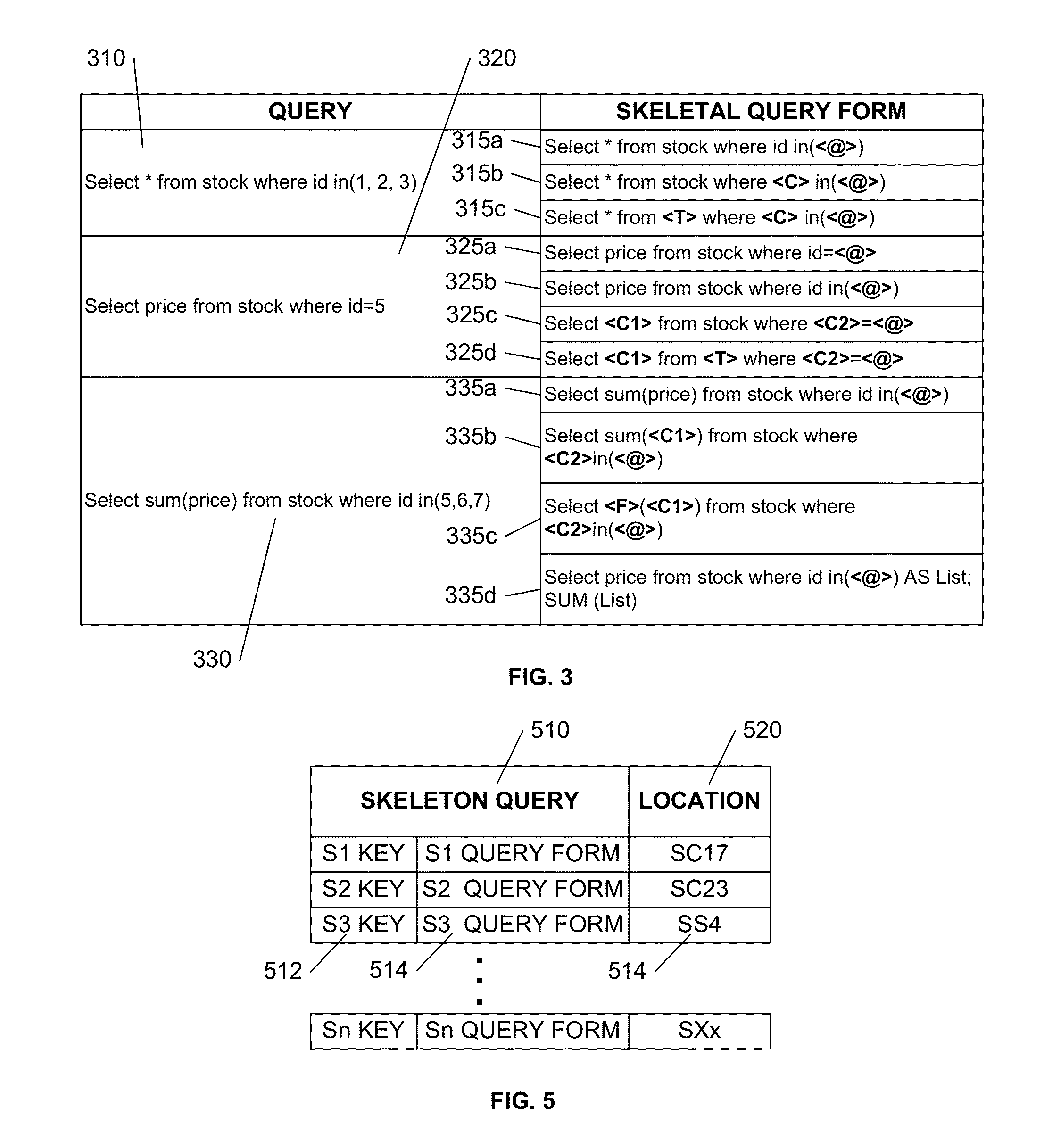

Query routing in a distributed database system

ActiveUS20130198232A1Lower performance requirementsReduce time consumptionDigital data information retrievalDigital data processing detailsDatabase serverClient-side

A distributed query system includes a distributed collection of dynamically created compiled queries. As each client submits a query, a parameterized query skeleton is identified, which identifies the general form of the query, and the parameters associated with the particular query. If a compiled form of the skeletal query is available within the distributed system, it is executed with the parameters of the current query. If the compiled form of the skeletal query is not available within the distributed system, a compiled form is created, and the location of this compiled skeletal query is stored for subsequent access by this client, or other clients. The executable compiled skeletal queries may be stored at each client system, in a commonly available server storage system, or within one or more database servers. A routing system may be provided to efficiently route parameterized queries to the appropriate location(s) of the compiled skeletal query.

Owner:SINGLESTORE INC

Systems and methods for granular resource management in a storage network

InactiveUS20070198722A1Improve performanceImprove reliabilityDigital computer detailsNetwork connectionsStorage area networkResource management

In accordance with some aspects of the present invention, systems and methods are provided for dynamically and / or automatically selecting and / or modifying data path definitions that are used in performing storage operations on data. Alternate data paths may be specified or selected that use some or all resources that communicate with a particular destination to improve system reliability and performance. The system may also dynamically monitor and choose data path definitions to optimize system performance, conserve storage media and promote balanced load distribution.

Owner:COMMVAULT SYST INC

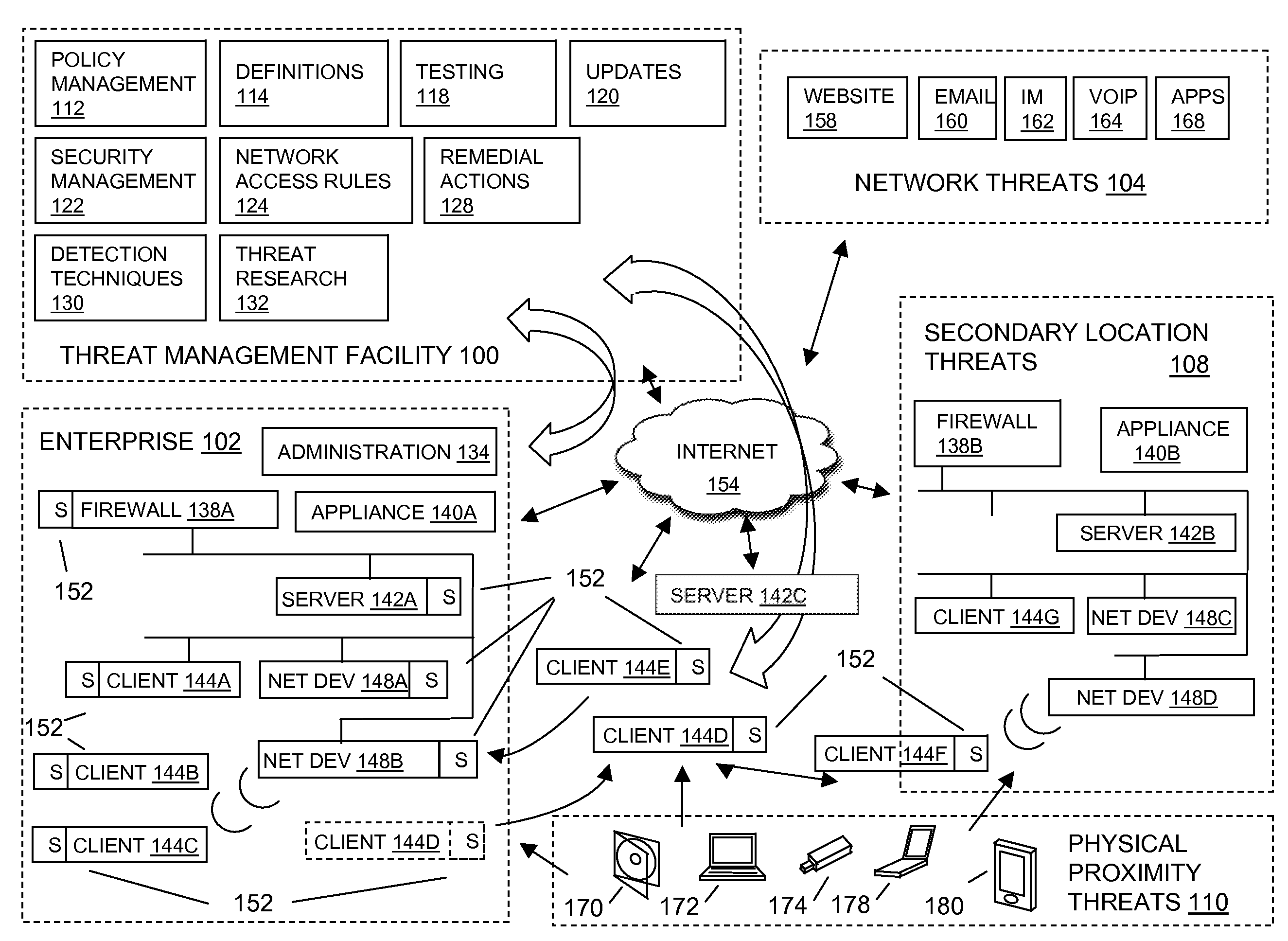

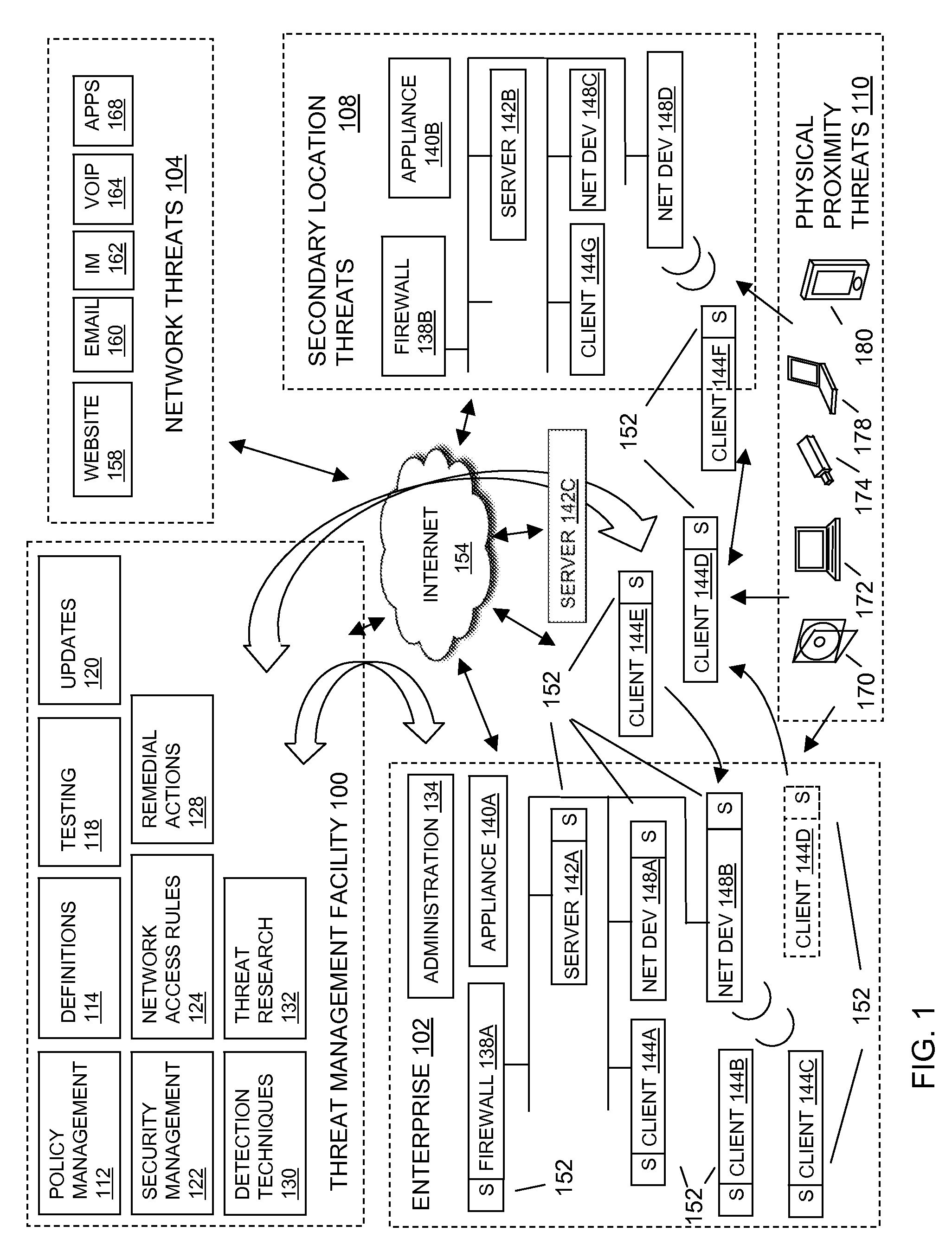

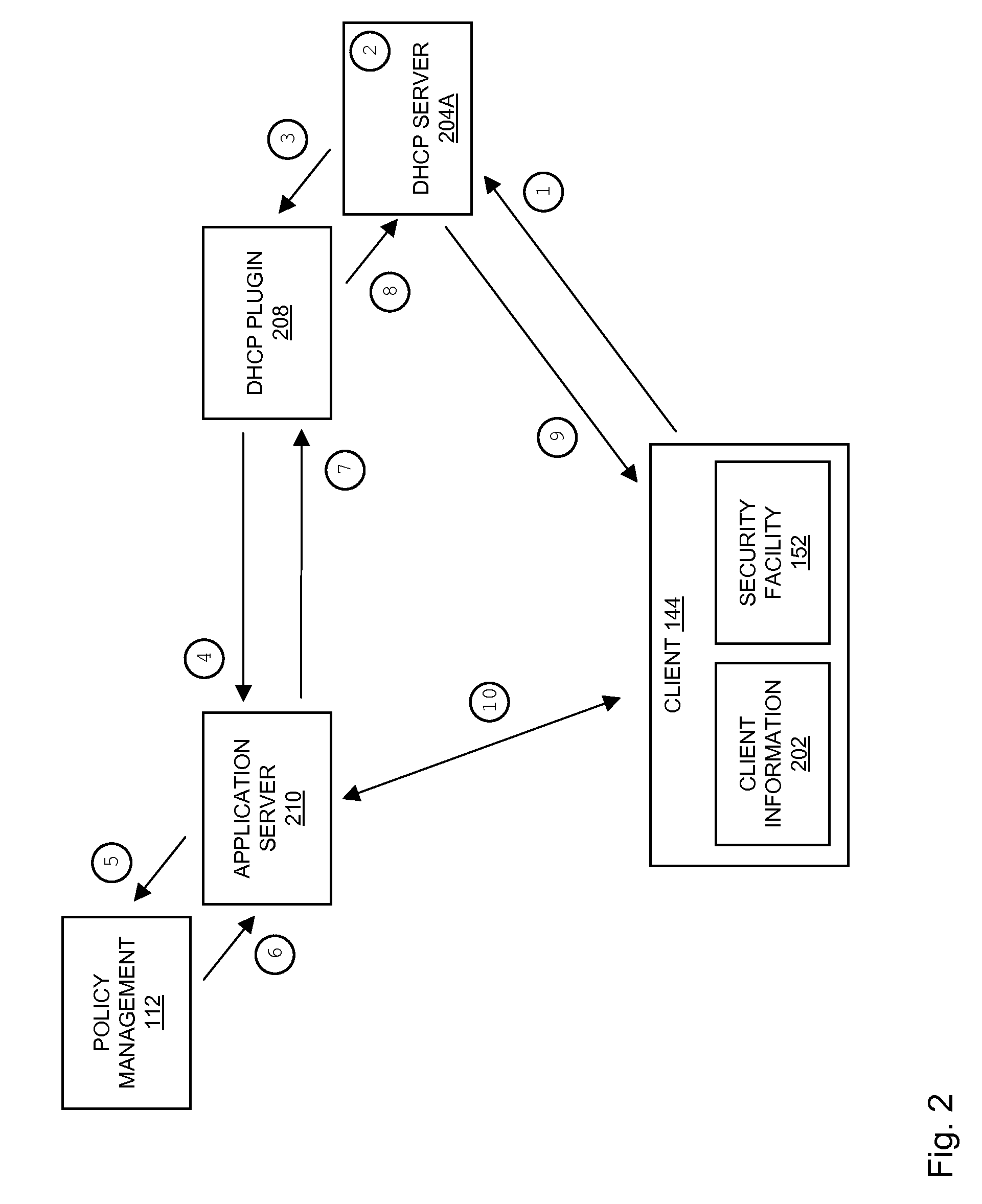

DHCP centric network access management through network device access control lists

InactiveUS20090217346A1Improved security situationEasy to operateDigital data processing detailsComputer security arrangementsSecurity complianceSecure state

In embodiments of the present invention improved capabilities are described for the computer program product steps of serving a limited network connection to an endpoint computing facility via network device access control lists, where the limited network connection may enable the endpoint to communicate with a limited set of network resources; assessing security compliance information relating to the endpoint to determine a security state; and in response to receiving an indication that the security compliance information is acceptable, serving a managed network connection to the endpoint, where the managed connection may enable the endpoint to communicate with a larger set of network resources than the limited network connection.

Owner:SOPHOS

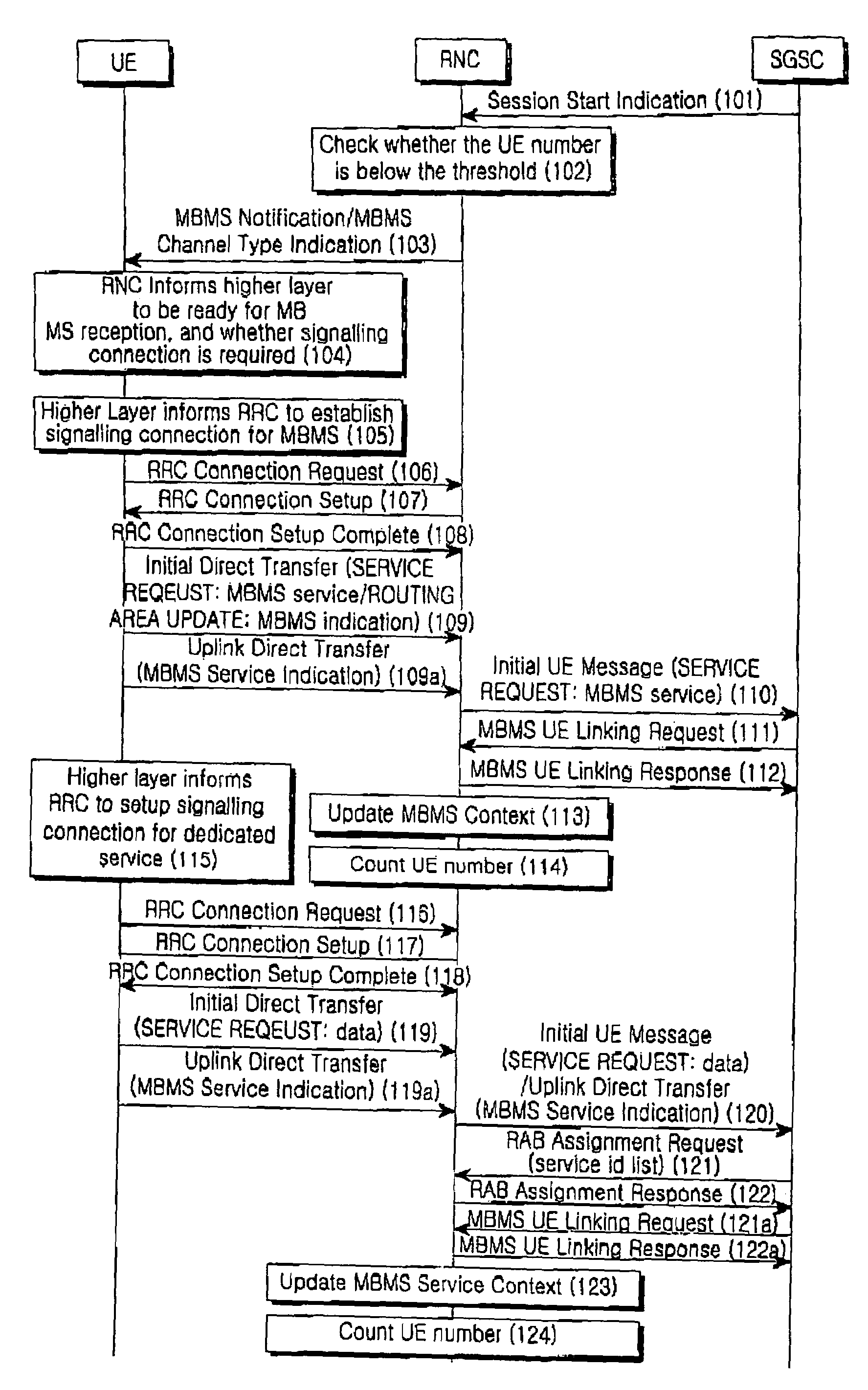

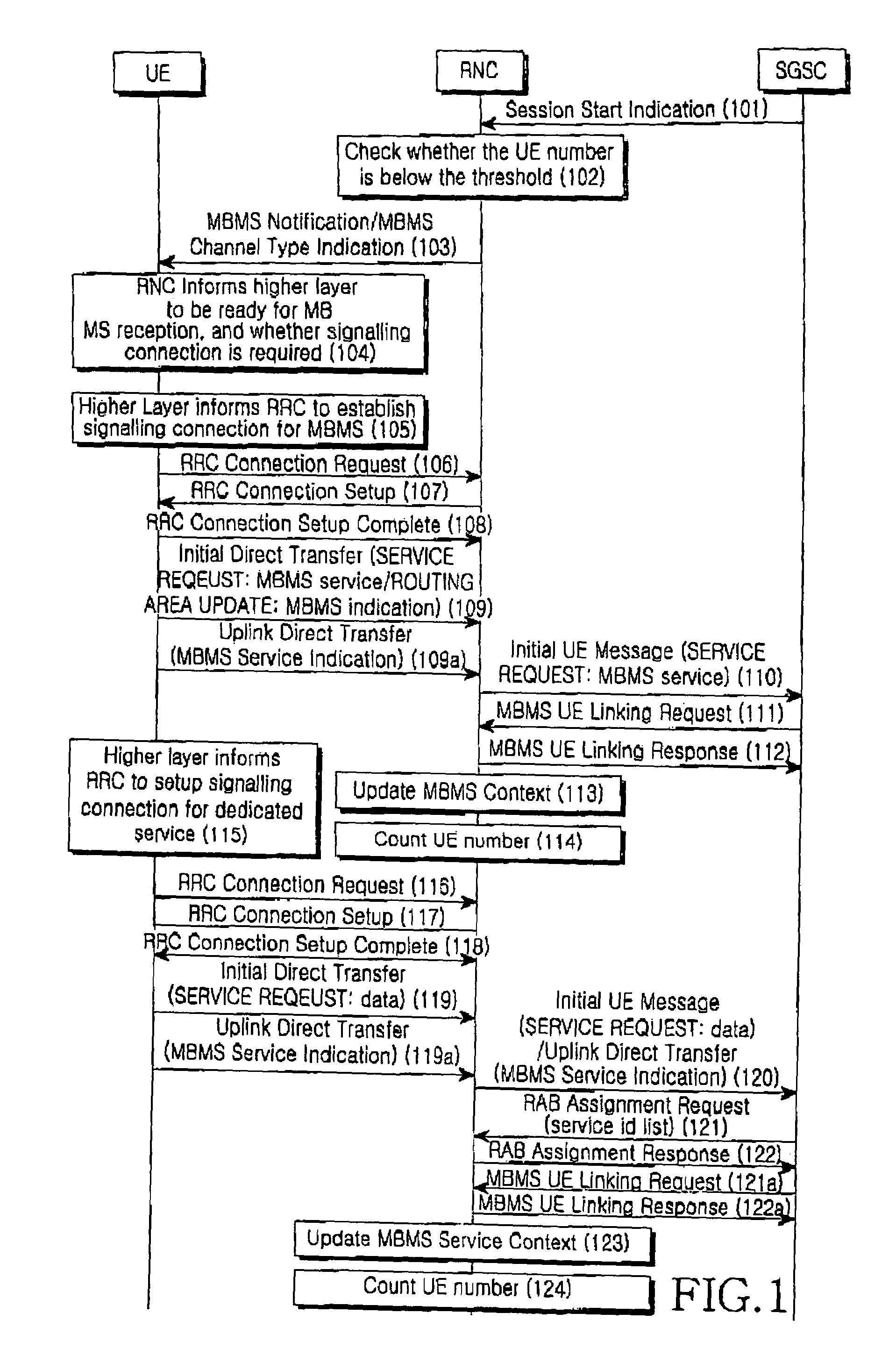

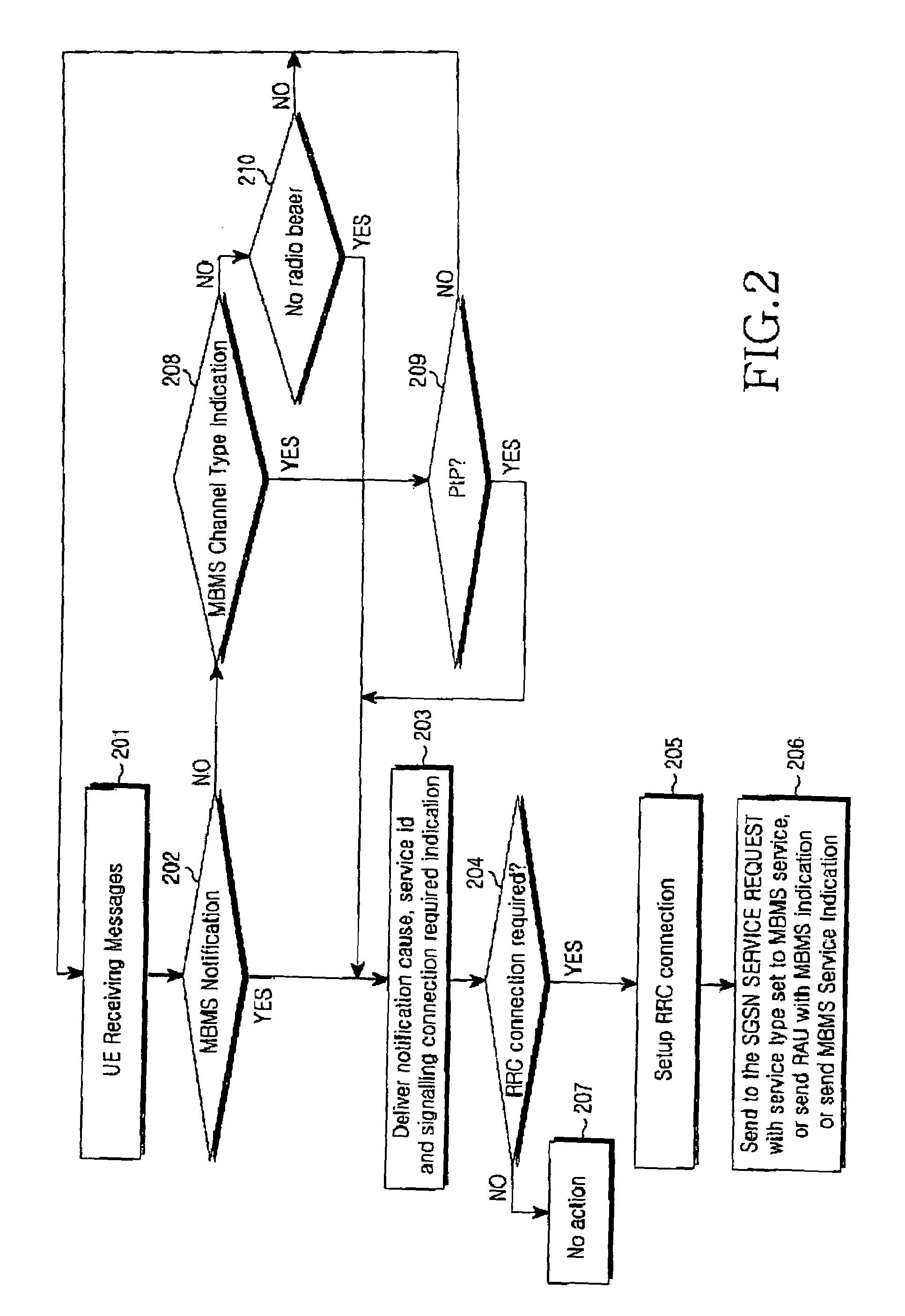

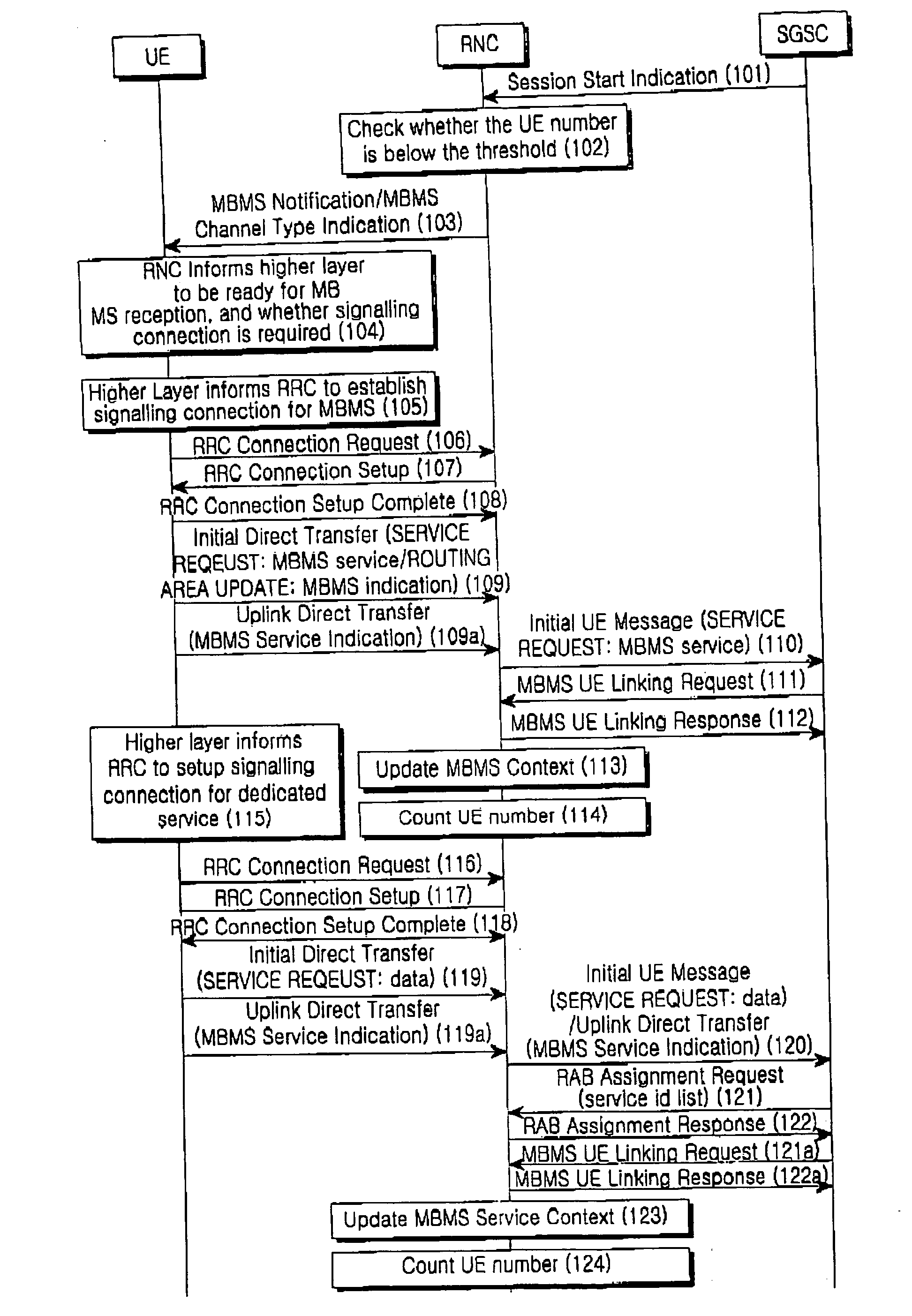

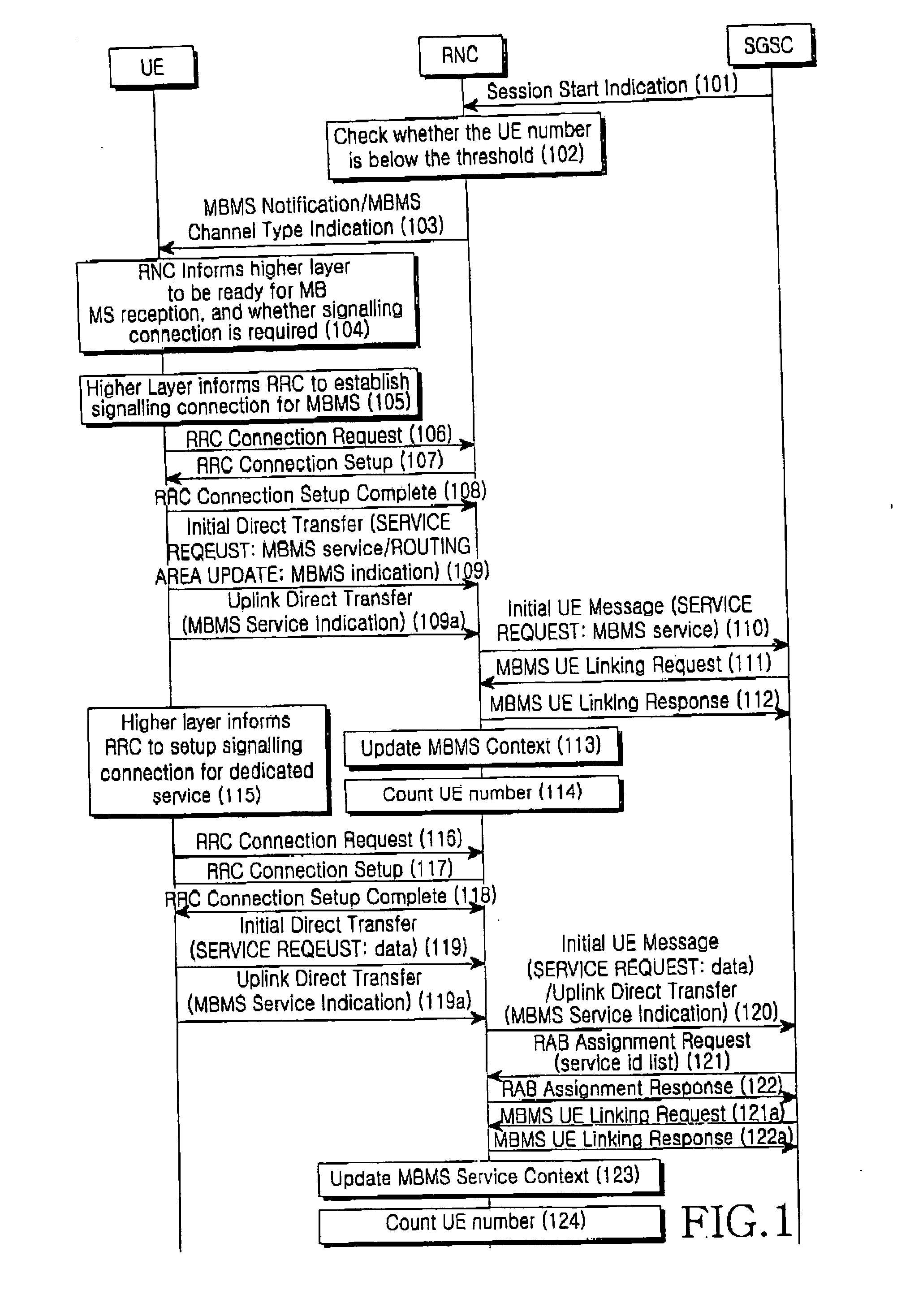

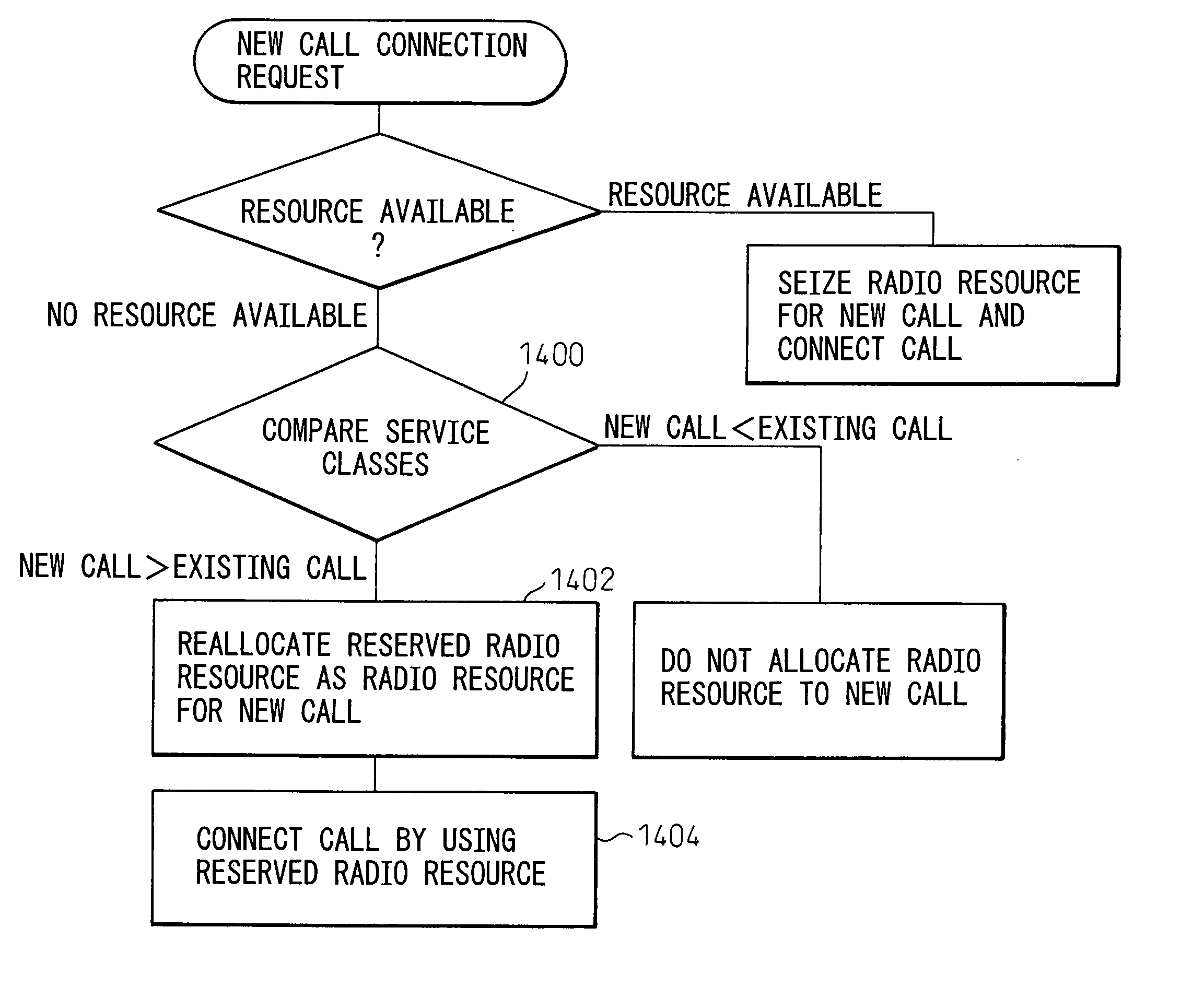

Method for distinguishing MBMS service request from other service requests

ActiveUS7400593B2Avoid interfaceAvoid resourcesConnection managementData switching by path configurationTelecommunicationsRadio resource

Owner:SAMSUNG ELECTRONICS CO LTD +1

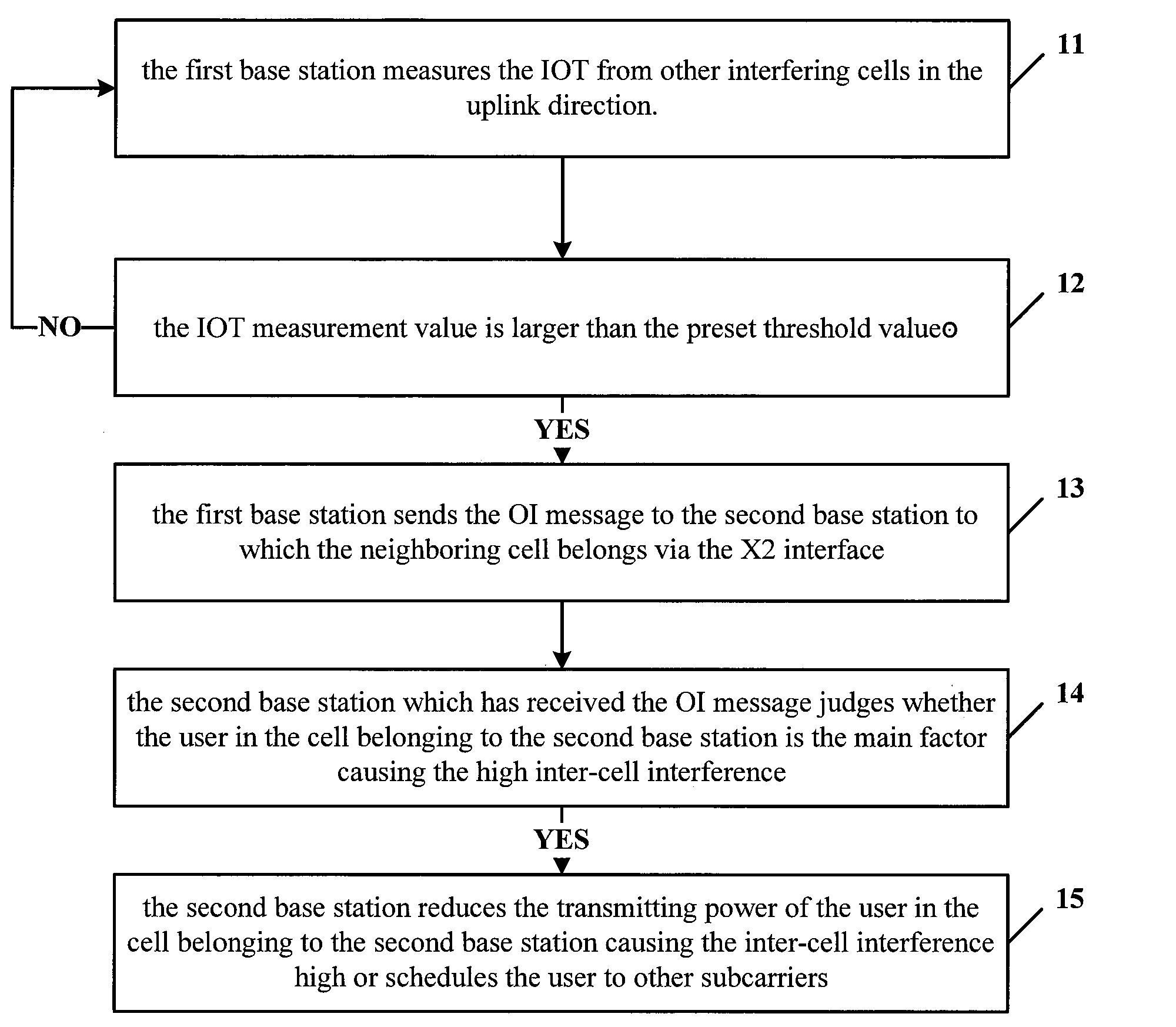

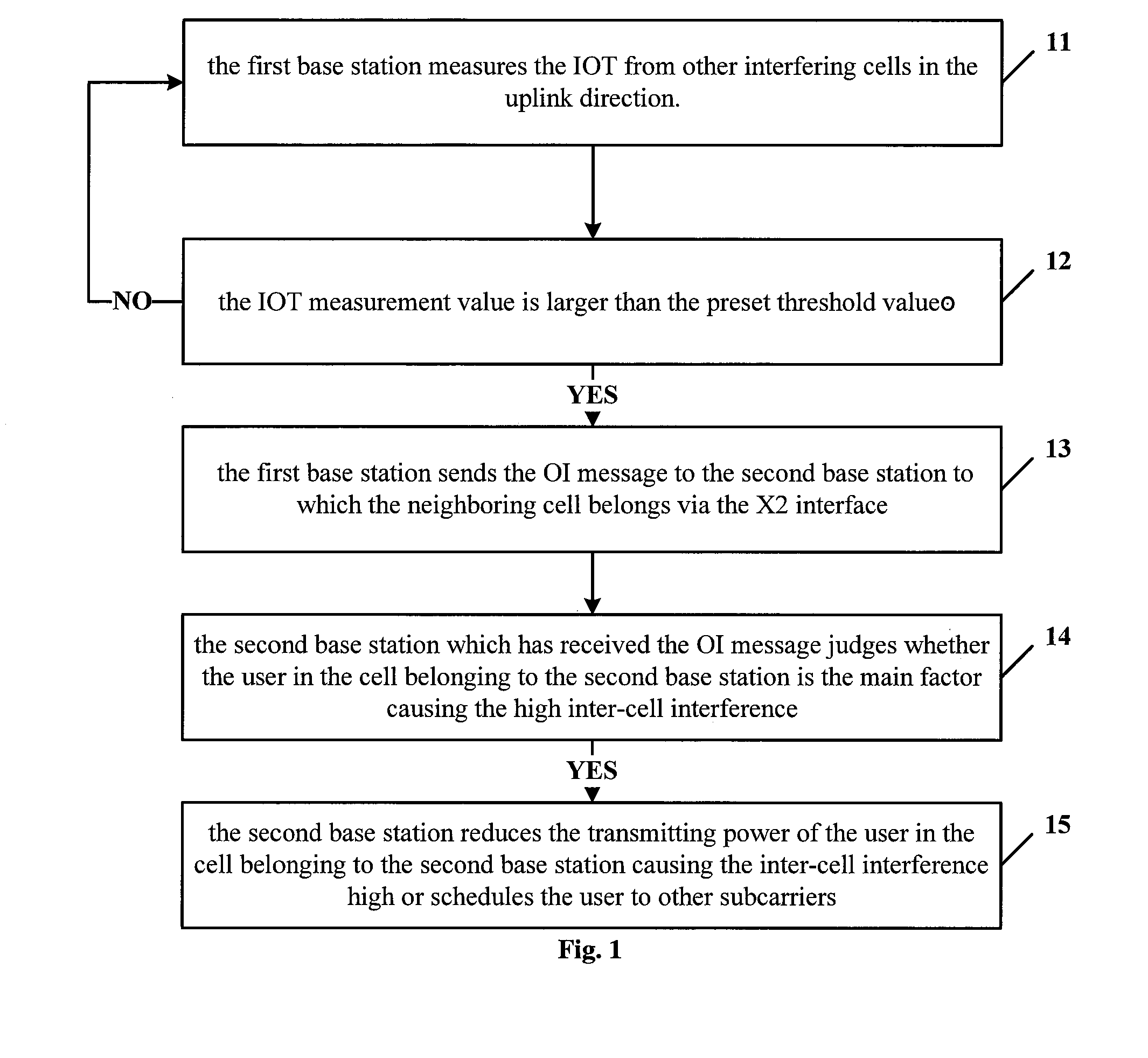

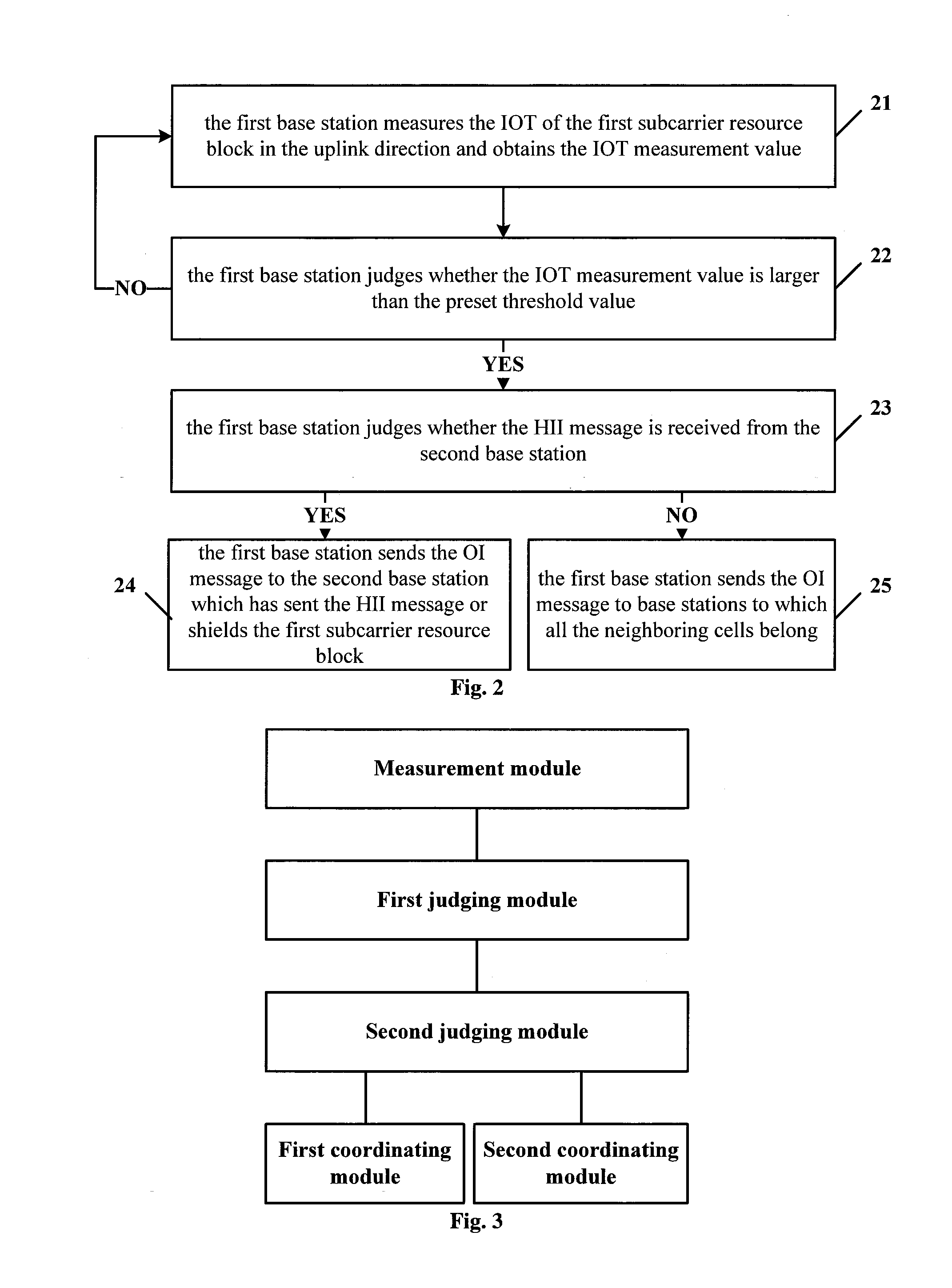

Inter-cell interference coordination method and base station

ActiveUS20110045856A1Reduce overheadReduce transmit powerRadio transmissionTransmission noise suppressionResource blockEngineering

An inter-cell interference coordination method comprises: measuring an interference over thermal noise of a first subcarrier resource block in an uplink direction and obtaining an interference over thermal noise measurement value by a first base station; judging whether a first high interference indicating message is received from a second base station when the interference over thermal noise measurement value is larger than a first preset threshold value by the first base station; sending an overload indicator message to the second base station which has sent the high interference indicating message or shielding the first subcarrier resource block by the first base station when the first high interference indicating message is received; and sending the overload indicator message to base stations to which all the neighboring cells belong by the first base station when the first high interference indicating message is not received. The overhead at X2 interface is reduced according to the present invention.

Owner:NTT DOCOMO INC

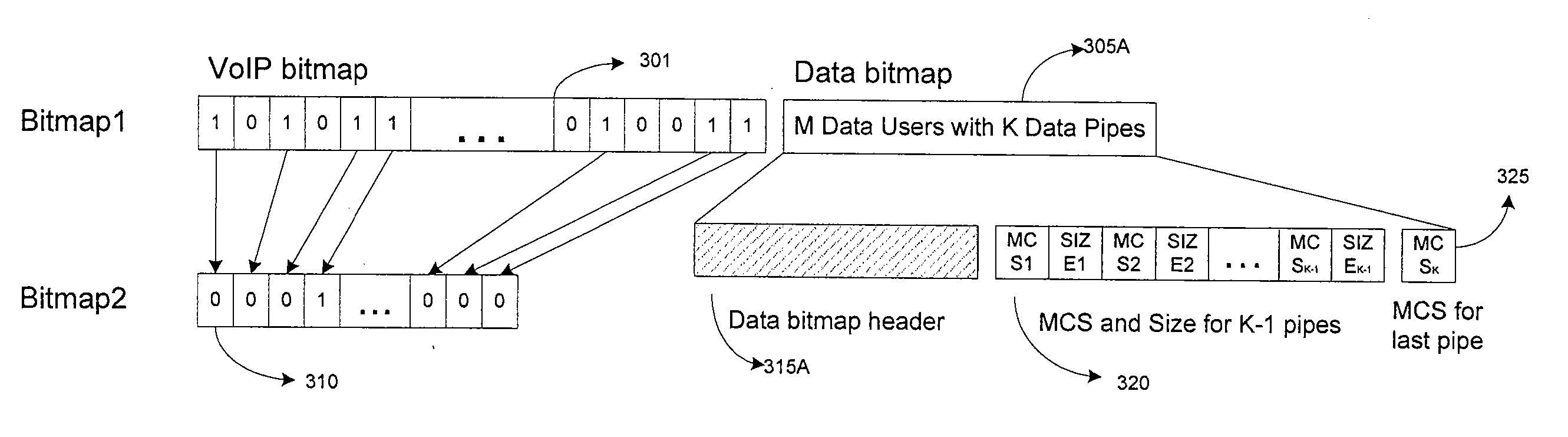

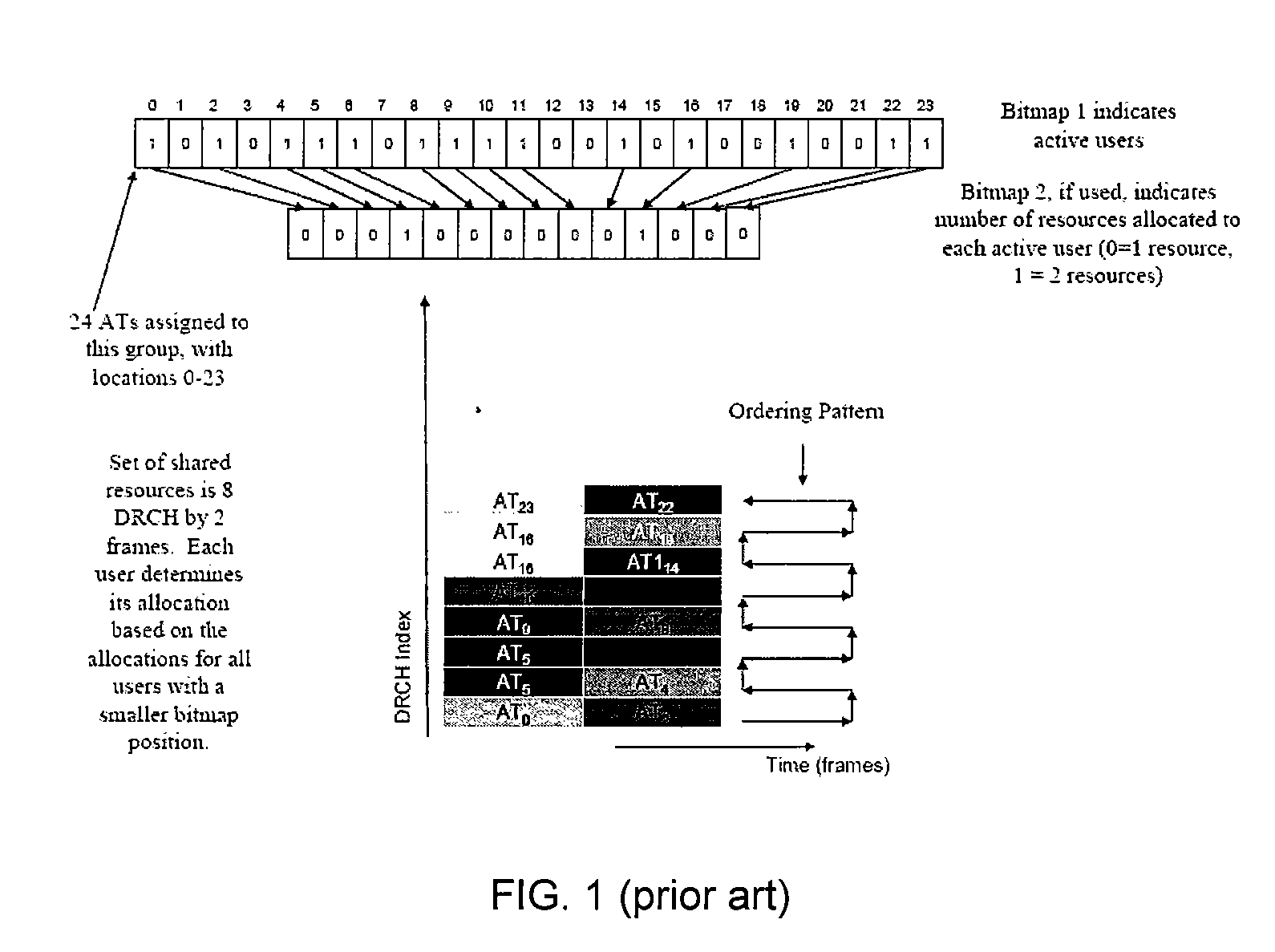

Method and system for sharing resources in a wireless communication network

ActiveUS20080095071A1ServeRaise priorityData switching by path configurationWireless communicationVoice communicationDistribution method

Method and system for sharing resources in a wireless communication network. According to an embodiment, the present invention provides a method for resource allocation. The method includes providing an access node that is configured to provide wireless access for both voice and data services. The method also includes providing at least a first access terminal that is configured to perform at least voice communication through the access node. Additionally, the method includes providing at least a second access terminal that is configured to perform at least data communication through the access node. The method further includes allocating a first portion of communication resources to the first access terminal. The method additionally includes allocating a second portion of communication of resources to the second access terminal. Furthermore, the method includes generating a group resource allocation message, which includes at least a first bitmap and a second bitmap.

Owner:FUTUREWEI TECH INC

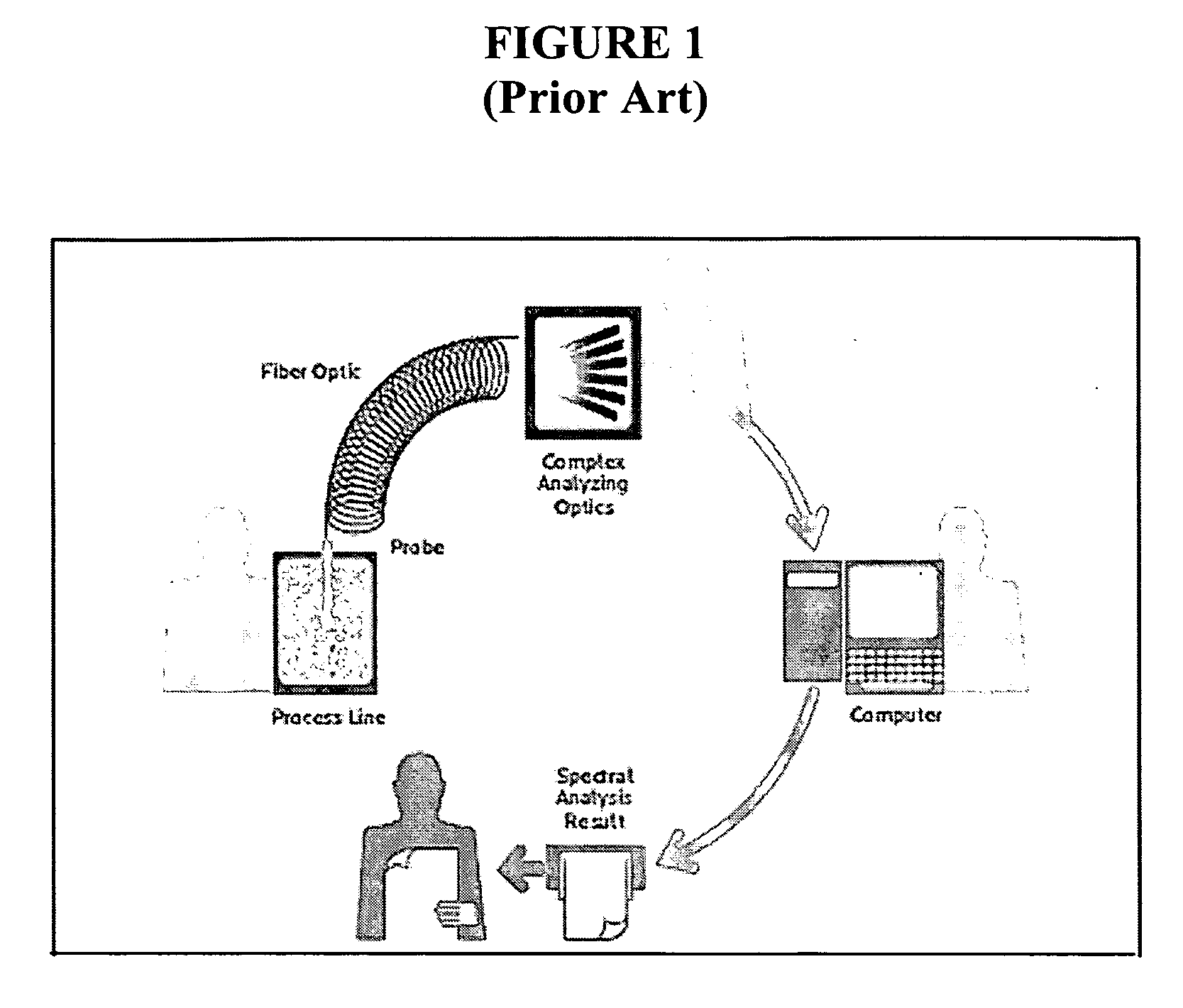

Methods of assessing and designing an application specific measurement system

ActiveUS20070282647A1Great confidenceReliable and economical to developMarket predictionsSpectrum investigationAnalysis dataEngineering

Methods of assessing feasibility of a project include receiving a datum from a customer; designing an application specific system based on the datum; analyzing the datum; evaluating a set of input parameters to determine an applicability of the application specific system to a customer process; and providing feedback for the customer process with the application specific system.

Owner:HALLIBURTON ENERGY SERVICES INC

Method for distinguishing MBMS service request from other services requests

ActiveUS20050083913A1Waste of resourceAvoid interfaceConnection managementData switching by path configurationTelecommunicationsRadio resource

Owner:SAMSUNG ELECTRONICS CO LTD +1

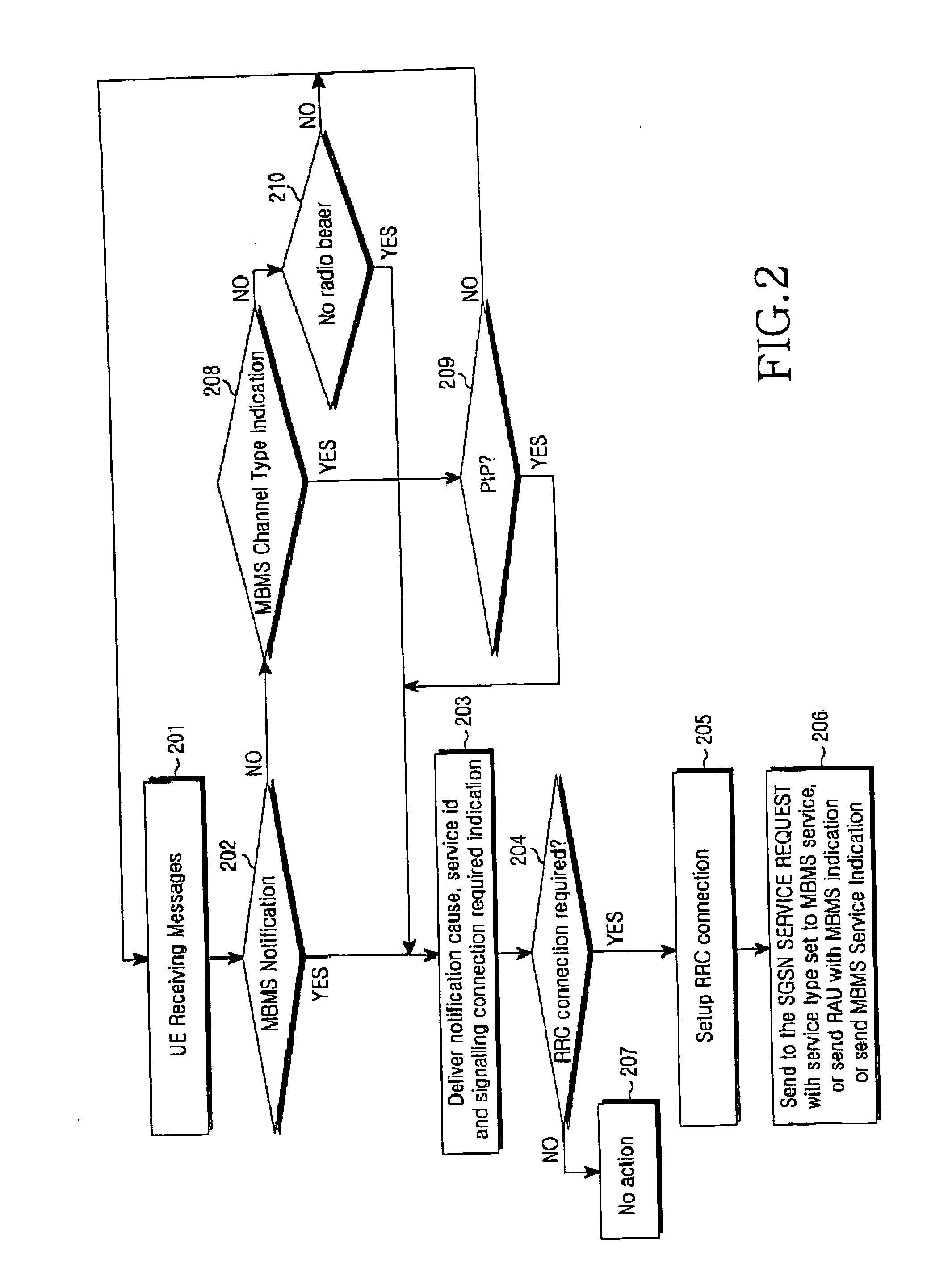

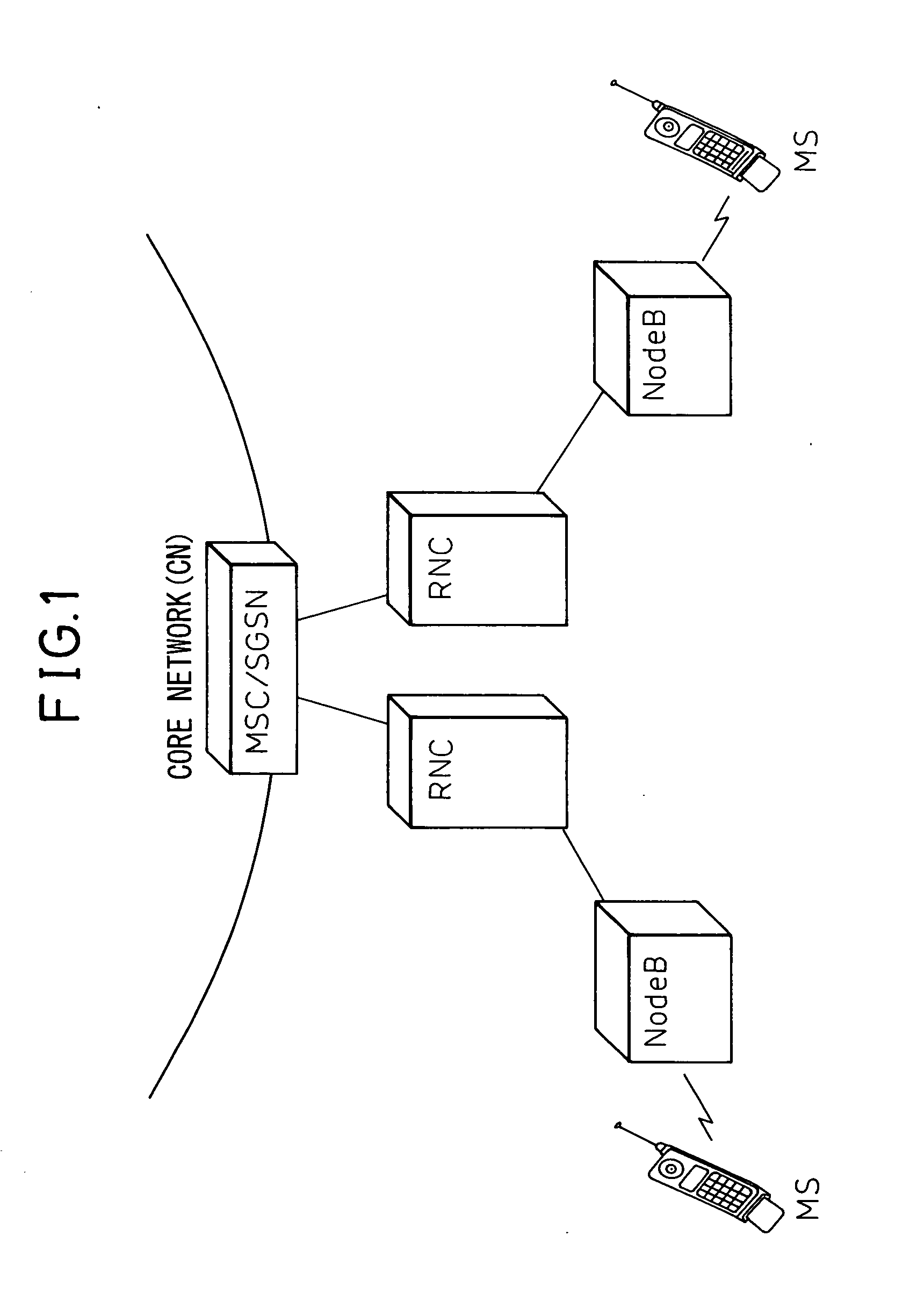

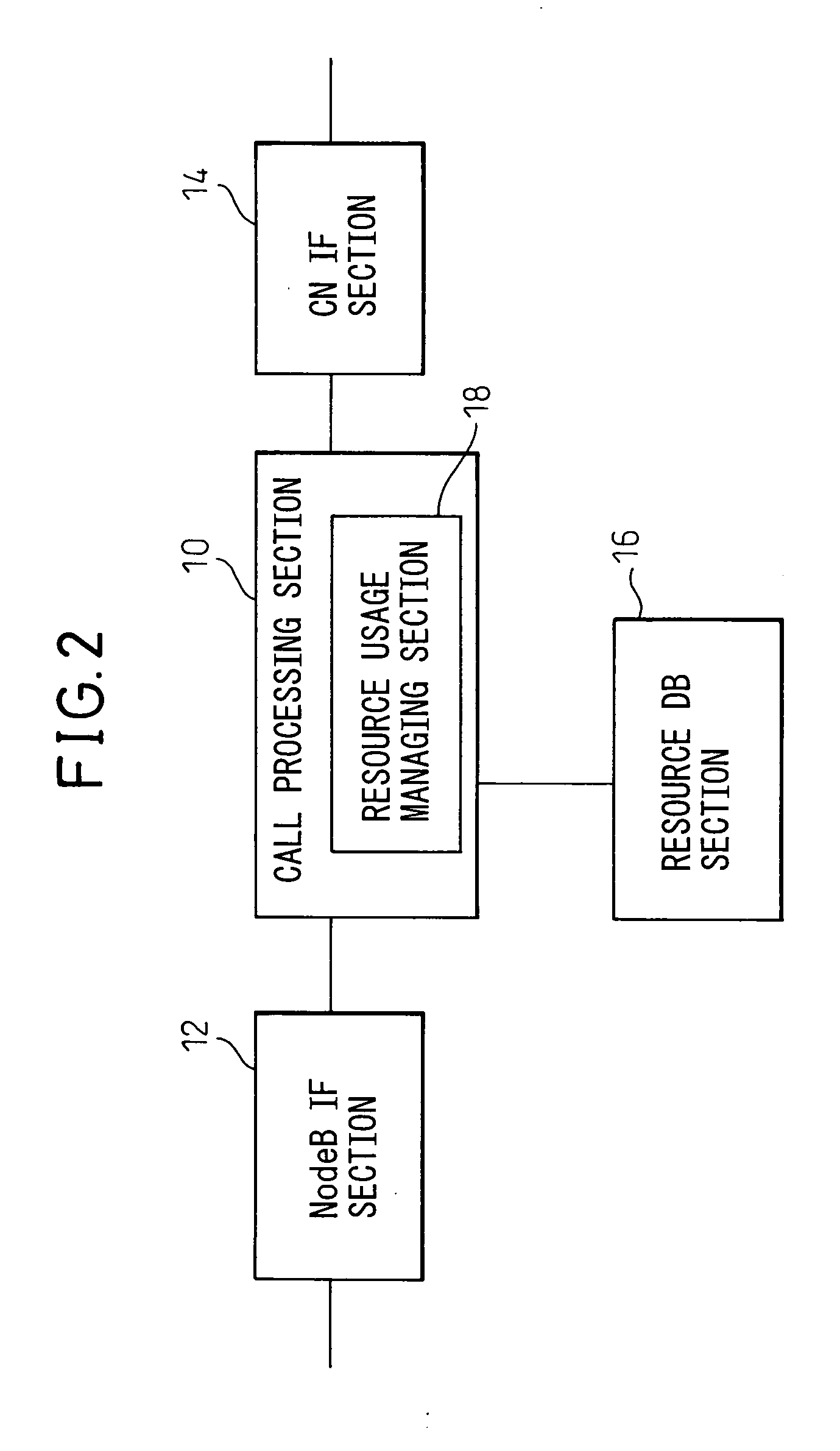

Mobile communication control method and radio network controller

InactiveUS20050208948A1Avoid resourcesShorten the timeNetwork traffic/resource managementSpecial service for subscribersTelecommunicationsRadio networks

A resource seizure failure and a delay time in resource seizure are prevented from occurring when a packet transmit request is made, during a connected voice call, from a mobile station to which a multicall service is provided. When setting up a CS call, a resource for a PS call is reserved. When a PS call request is made by the user, the PS call is set up by using the reserved resource.

Owner:FUJITSU LTD

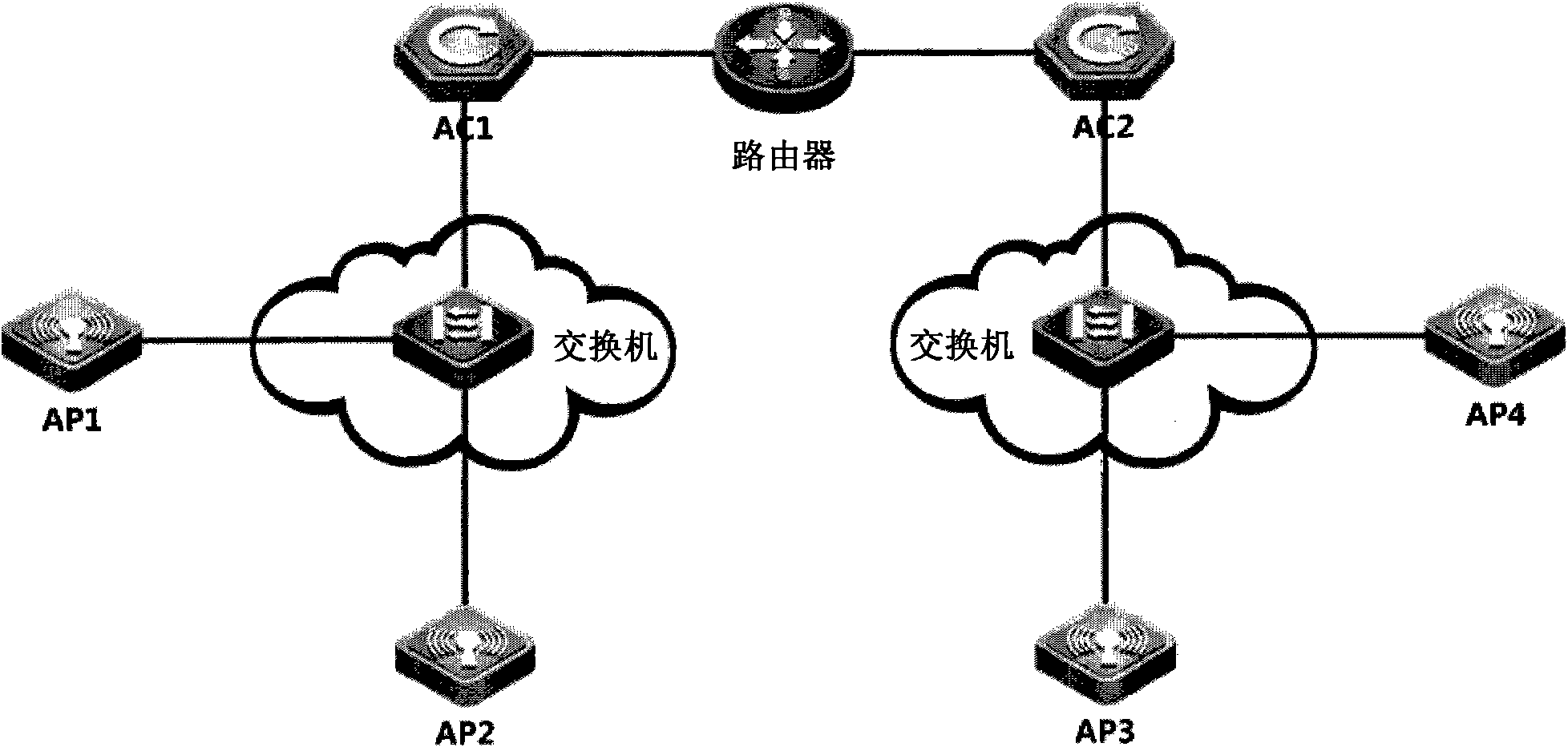

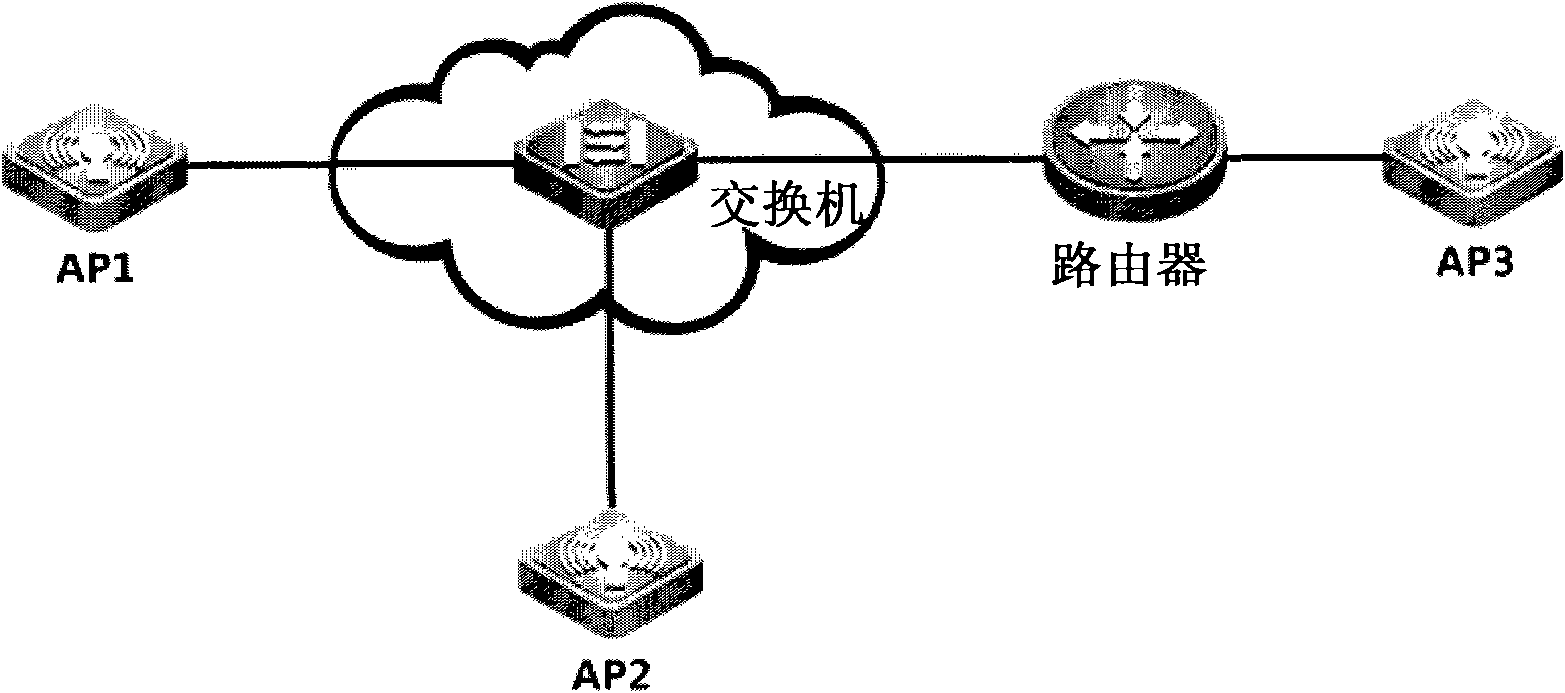

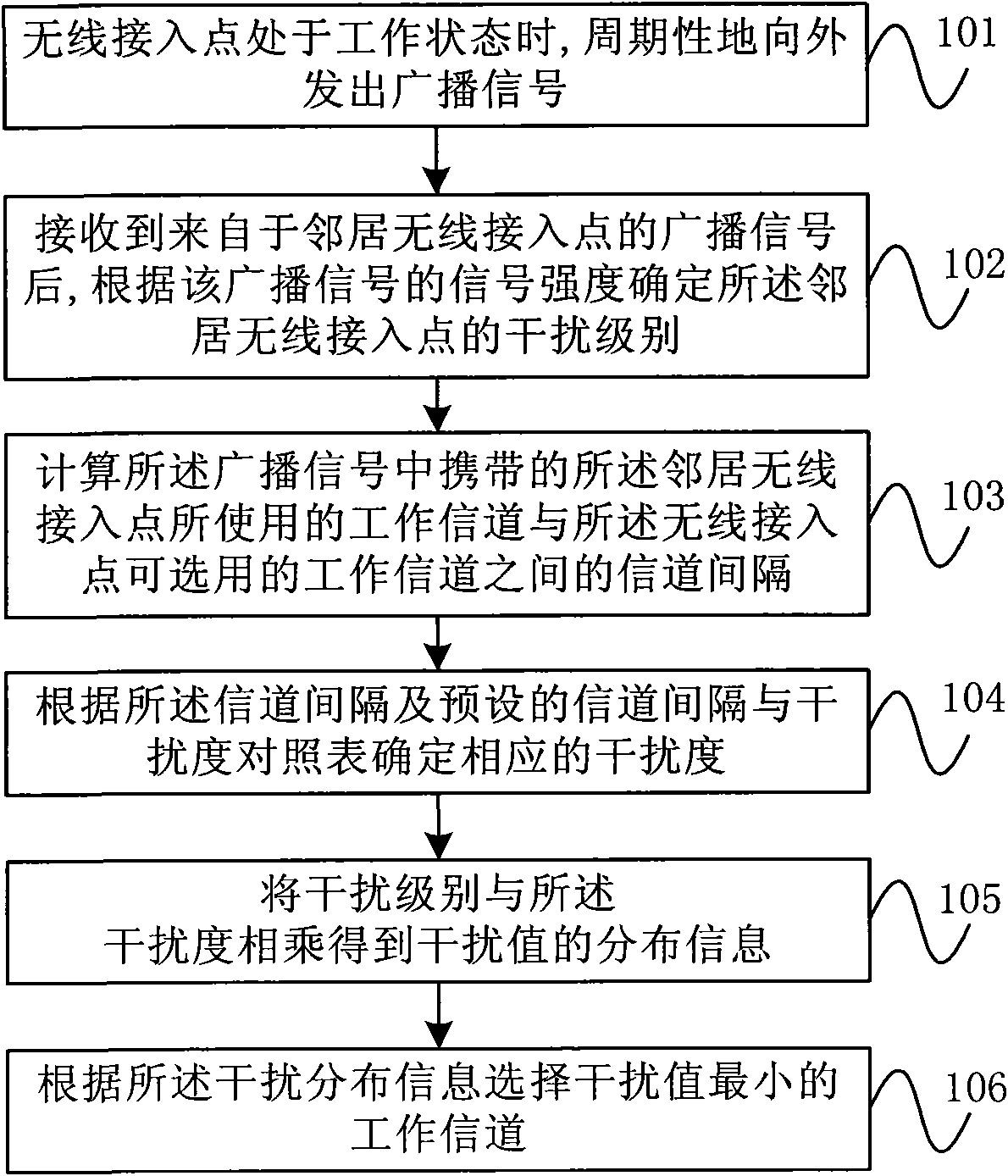

Wireless access point working channel selecting method and device

InactiveCN101835243AReduce distractionsNo need to occupyAssess restrictionNetwork topologiesSystem capacityTelecommunications

The invention provides a wireless access point working channel selecting method and a wireless access point working channel selecting device. The wireless access point working channel selecting method comprises the following steps of: periodically transmitting broadcast signals outwards from an AP which is positioned in a working state; determining the interference level of an adjacent AP according to the signal strength by the AP receiving the broadcast signals; calculating the channel spacing between the working channel used by the adjacent AP and the working channel used by the AP; determining the corresponding interference degree according to the channel spacing and the preset channel spacing and an interference degree comparison table; multiplying the interference level by the interference degree to obtain the distribution information of the interference value; and selecting the working channel with the minimum interference value according to the interference distribution information. The wireless access point working channel selecting method and the wireless access point working channel selecting device can reduce the channel interference and improve the system capacity, does not need to occupy a common channel, avoids the resource waste, can be applied to the common fat AP framework and thin AP framework in the wireless local area network simultaneously, and has wide applicability.

Owner:BEIJING XINWANG RUIJIE NETWORK TECH CO LTD

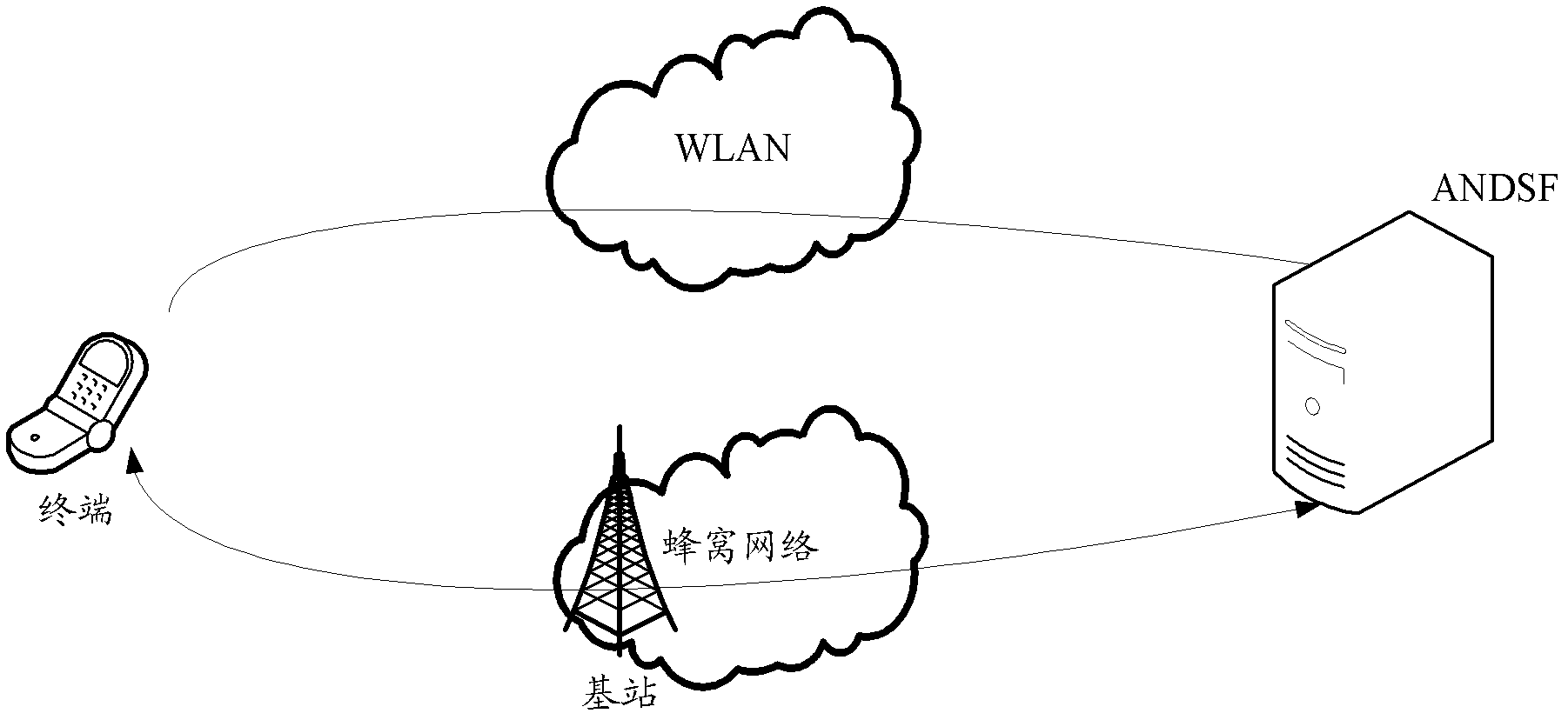

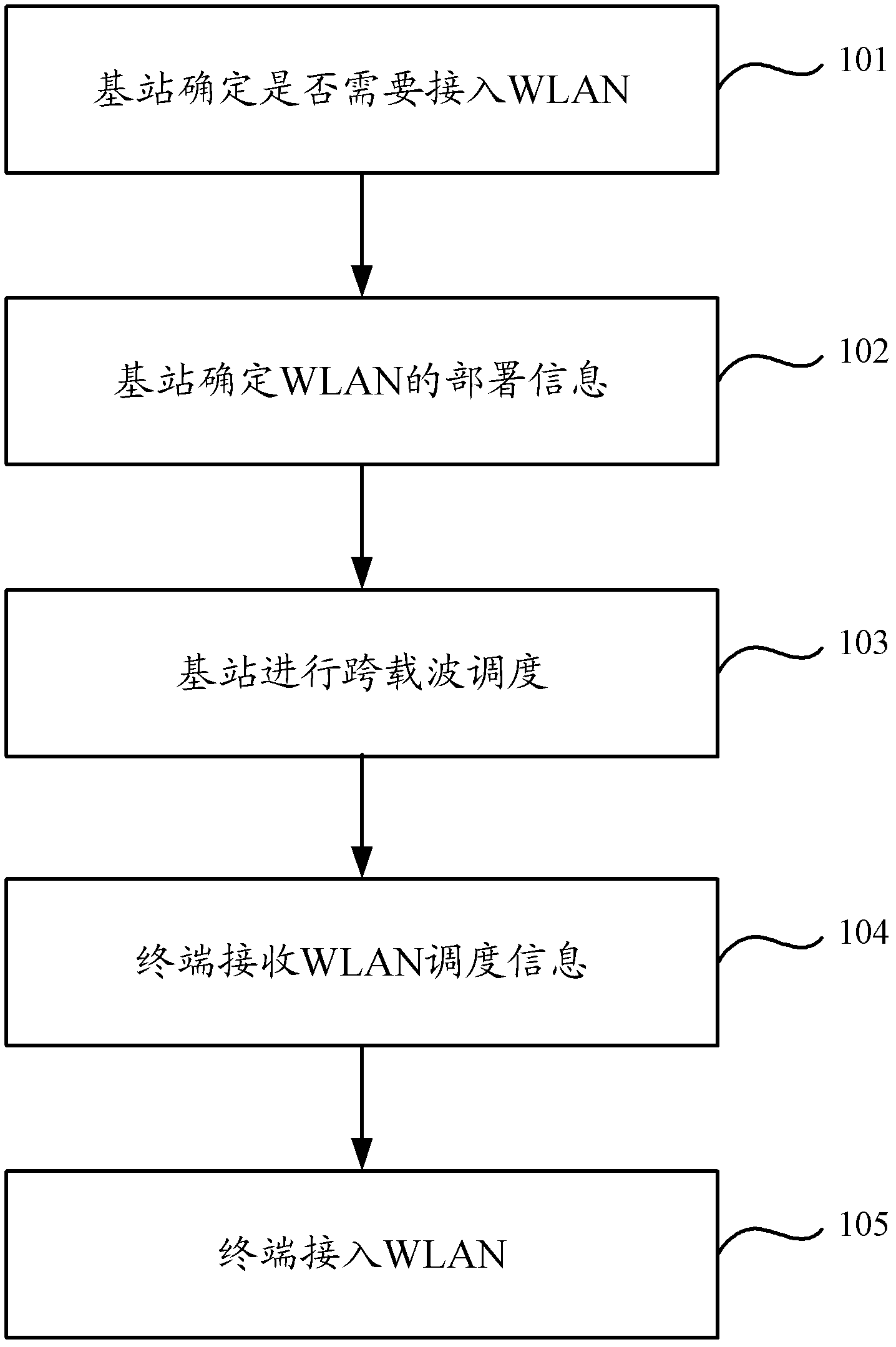

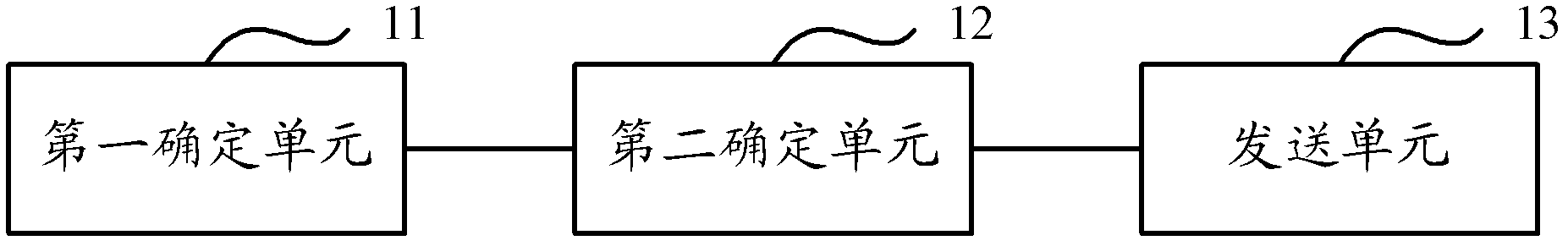

Method, base station, terminal and system for cooperative work of wireless local area network (WLAN) and cellular network

ActiveCN103220786AAvoid timeAvoid resourcesNetwork traffic/resource managementAssess restrictionAccess timeCarrier signal

The invention provides a method, a base station, a terminal and a system for cooperative work of a wireless local area network (WLAN) and a cellular network. The method comprises the steps that when the base station confirms that the WLAN should be accessed into the terminal, namely the WLAN needs to be used for distributing services of the cellular network, deployment information of the WLAN is confirmed, a frequency point of work of the WLAN is used as a sub-carrier, a physical downlink control channel (PDCCH) of the cellular network is used for carrying out cross-carrier scheduling on the WLAN through a carrier aggregation mode, and the WLAN can be accessed into the terminal according to WLAN scheduling information sent by the base station through the PDCCH. Therefore, the problems that when the fact that the WLAN should be accessed into the terminal is confirmed, access time is long and system resources are wasted in the prior art are solved, and speed that the WLAN is accessed into the terminal is improved.

Owner:CHINA MOBILE COMM GRP CO LTD

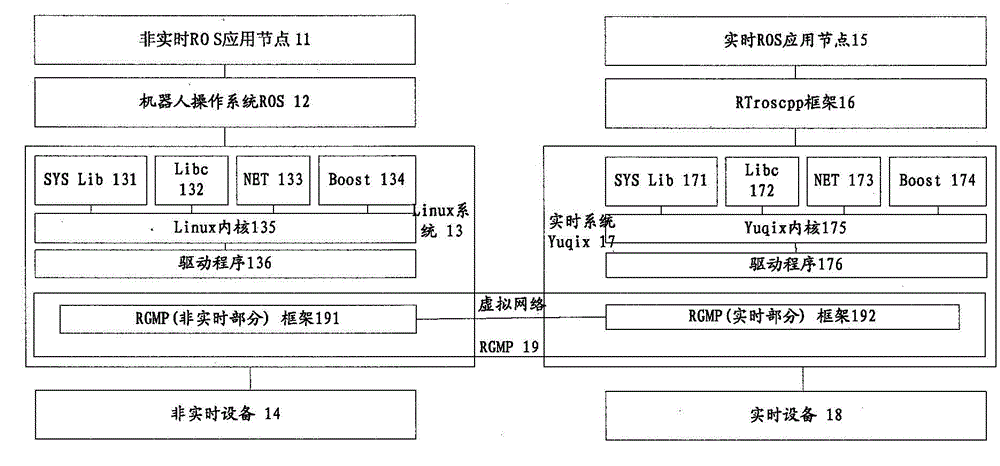

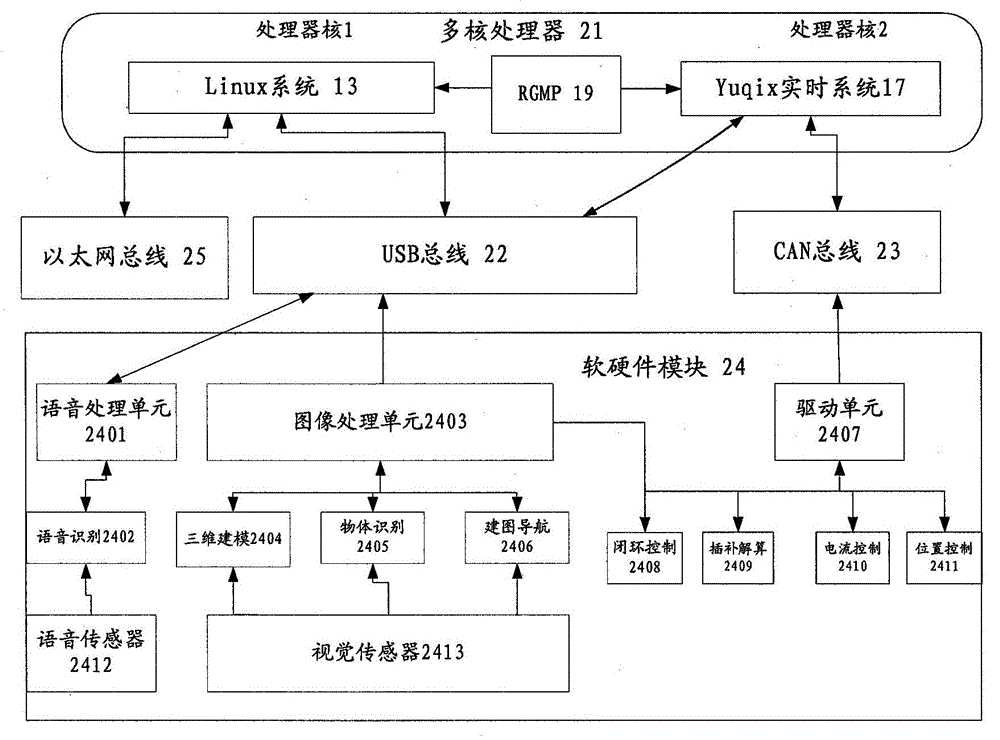

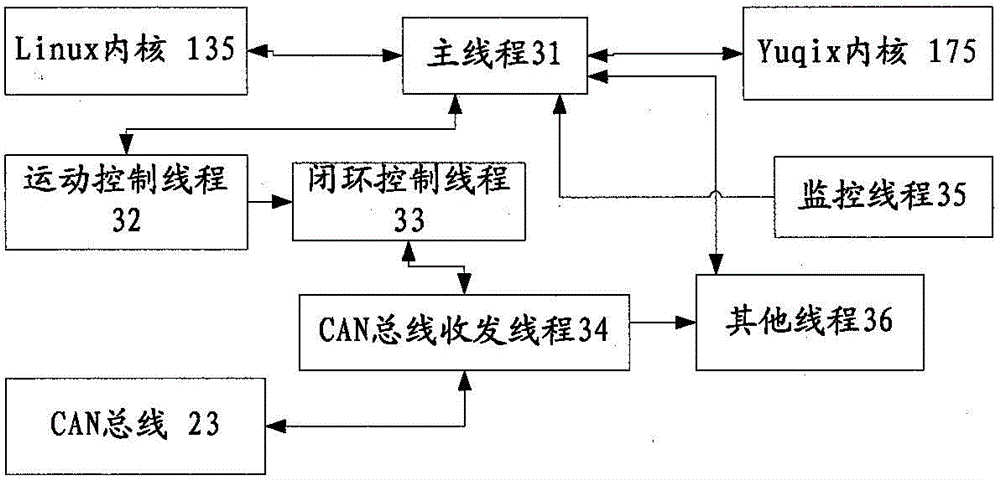

Robotic hybrid system application frame based on multi-core processor architecture

InactiveCN105278940ARun independently of each otherDebug each other independentlySpecific program execution arrangementsFrame basedStructure of Management Information

The invention describes a robotic hybrid system application frame based on a multi-core processor architecture. In a robotic system which takes an ARM (Advanced RISC Machines) / X86 multi-core processor as a controller, a multi-core parallel processing structure of the ARM / X86 multi-core processor is used for operating the robotic hybrid system application architecture consisting of a real-time operating system, non-real-time operating systems and a system supporting frame on a whole robotic controller so as to provide improved operating system service, wherein the real-time operating system, non-real-time operating systems and the system supporting frame simultaneously operate. In the application frame, one real-time operating system independently operates in one ARM / X86 core, meanwhile, a plurality of non-real-time operating systems operate in other ARM / X86 cores, the operating systems mutually individually occupy processor resources and peripherals, robotic application programs with different real time requirements are independently operated, and the application programs can be used (drawing 1) in a uniform ROS (Robotic Operating System) application node form.

Owner:BEIHANG UNIV

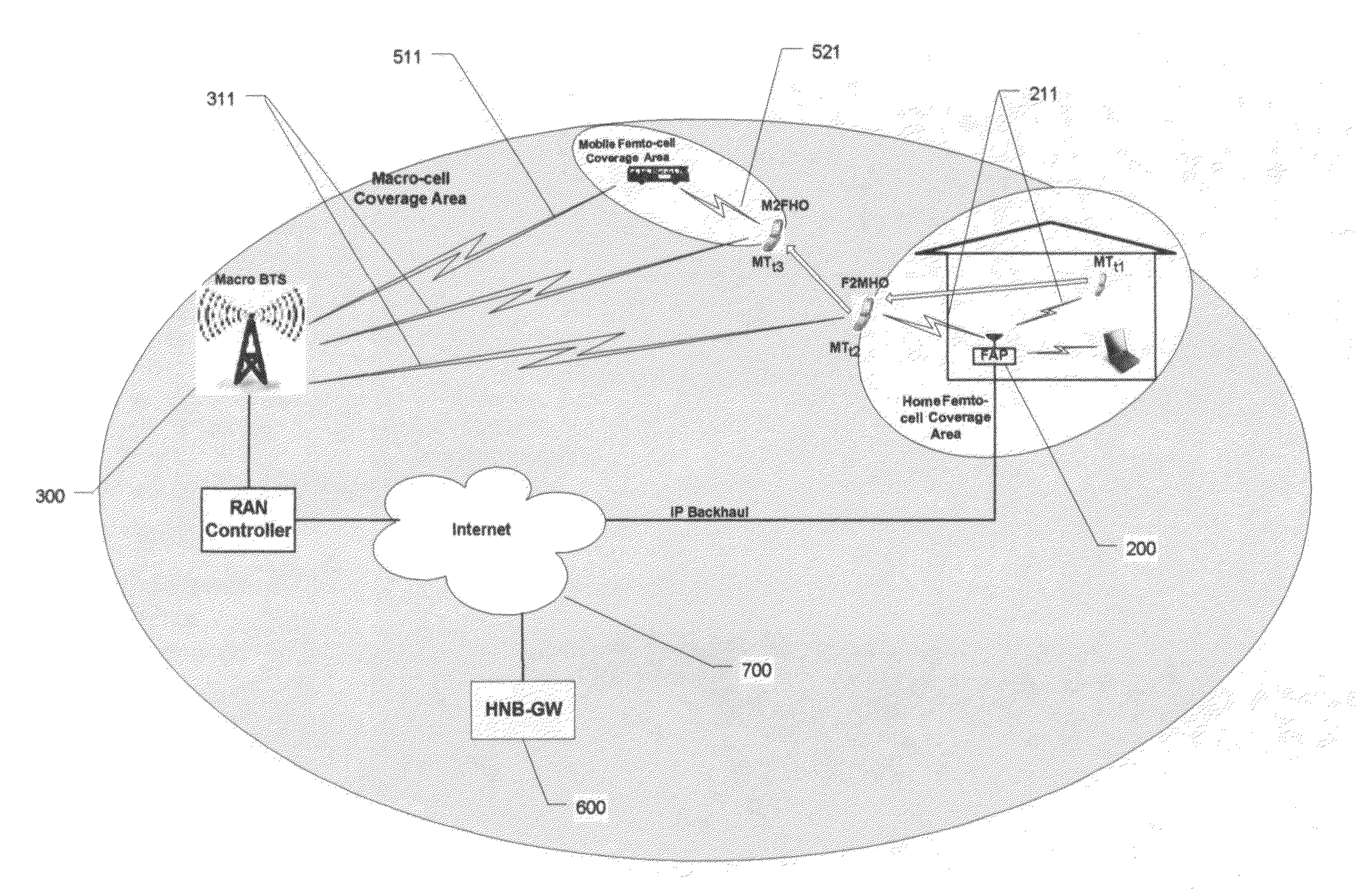

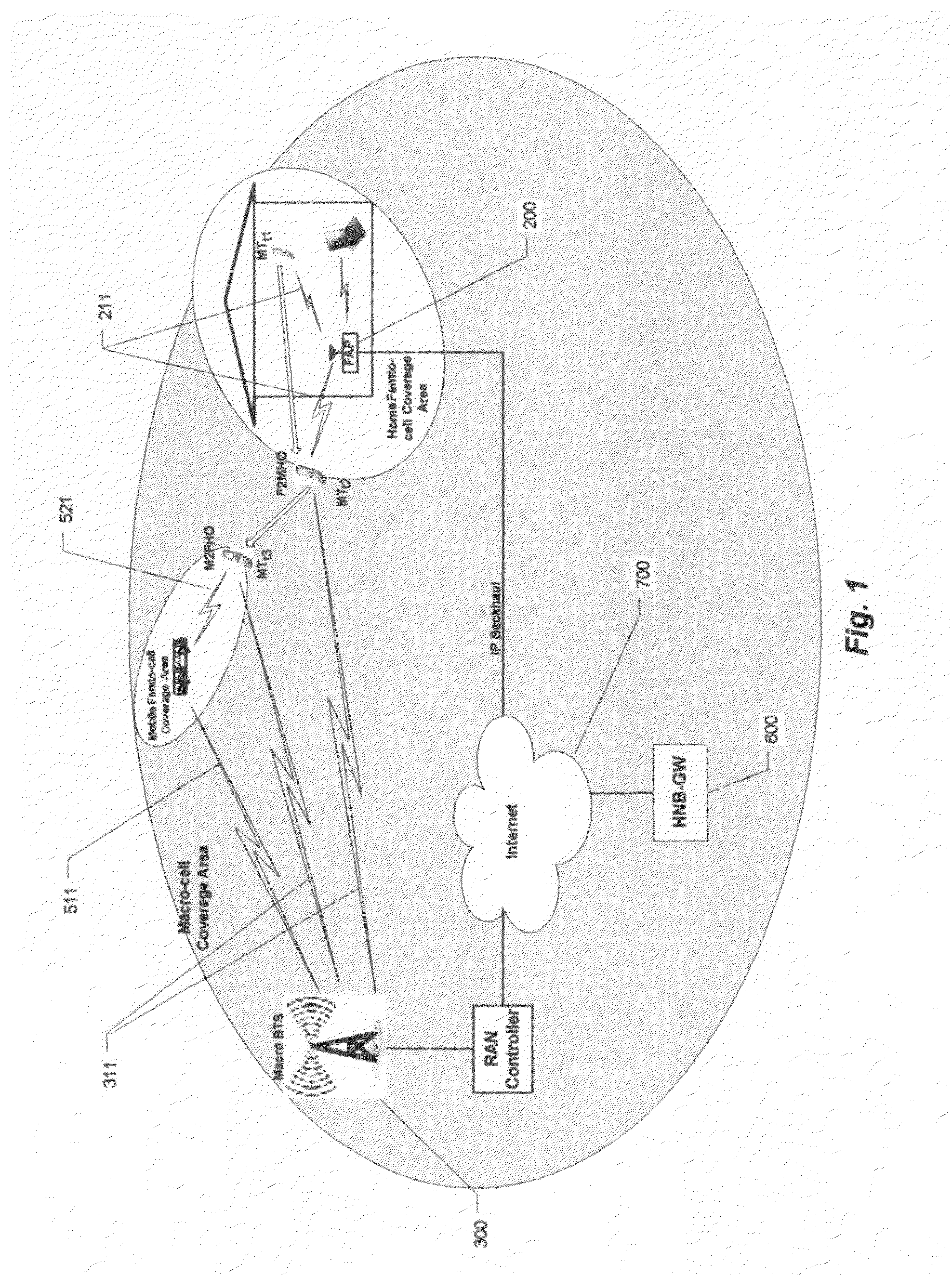

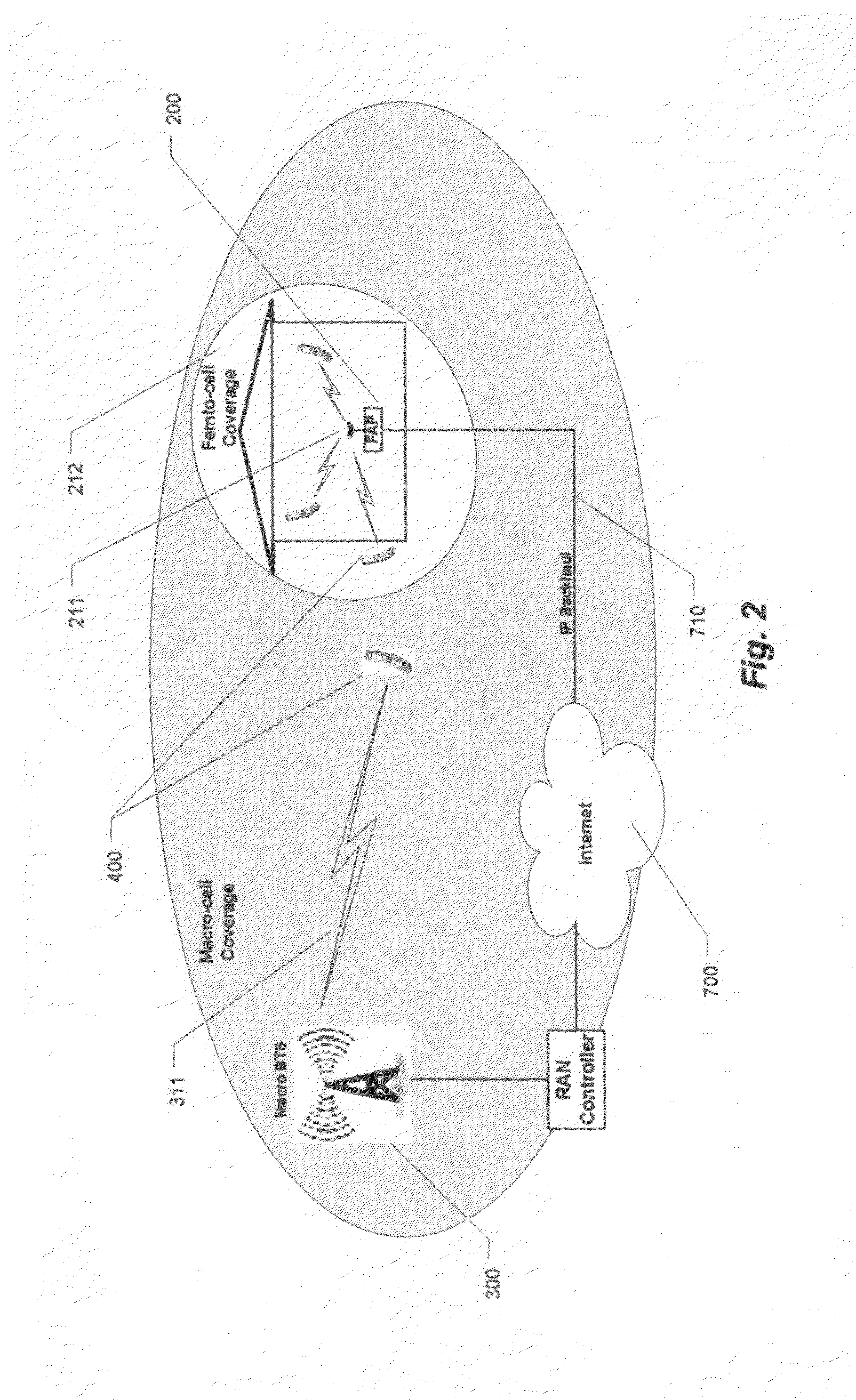

Mobile Femto-cell in a Wireless Safety Network

ActiveUS20110217947A1Provide experienceIncrease macro-cell capacity qualityNetwork topologiesConnection managementEngineeringPicocell

This invention provides wireless safety network through the integration of mobile femto-cells (mFAP), into macro-cellular system. Such network provides safety management for students during their travel to and from school through the supervision of handovers between home and mobile femto-cell and the macro-cellular environment as well as supervision of class attendance, emergency function, and other services.

Owner:IPCOMM

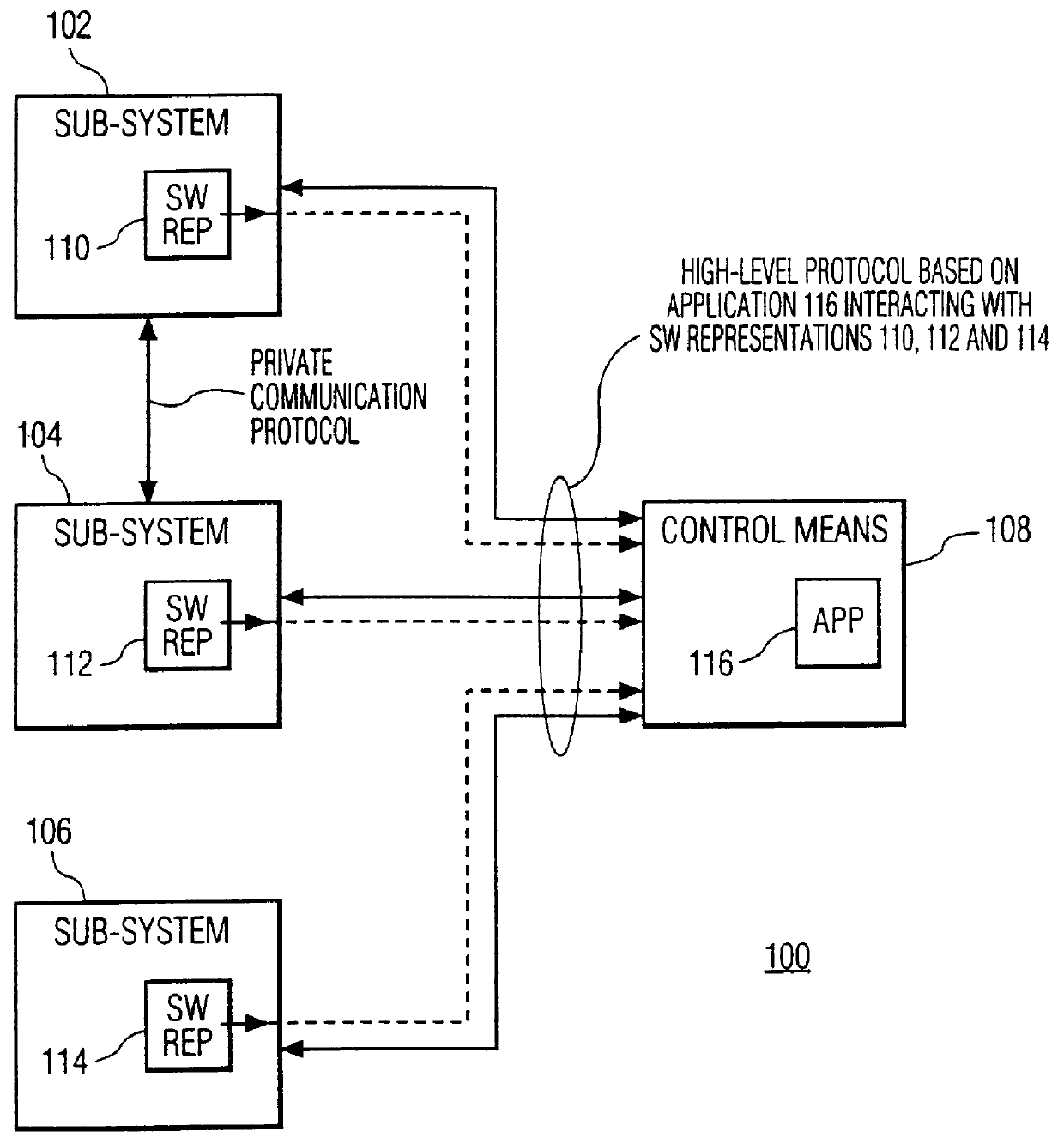

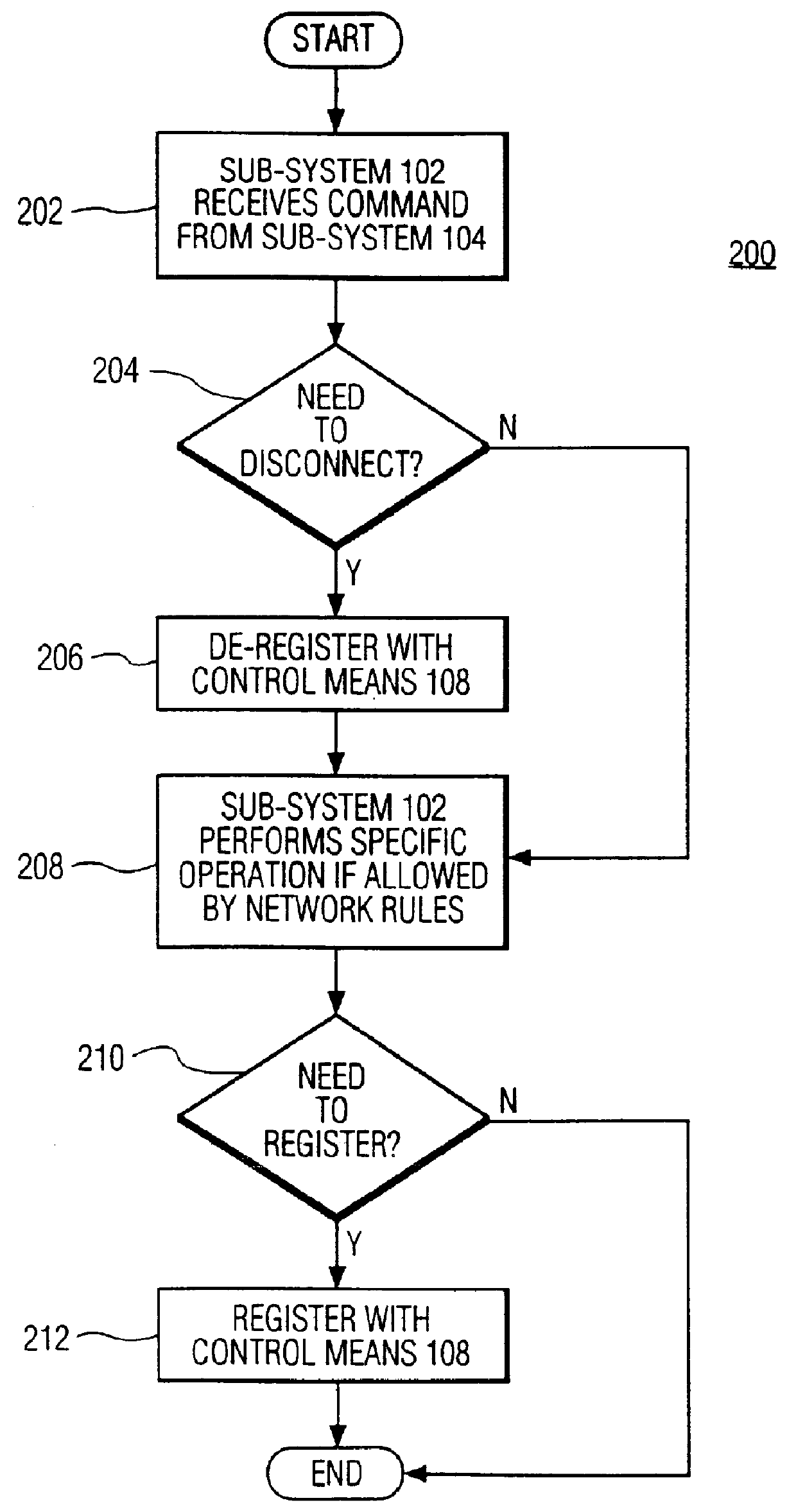

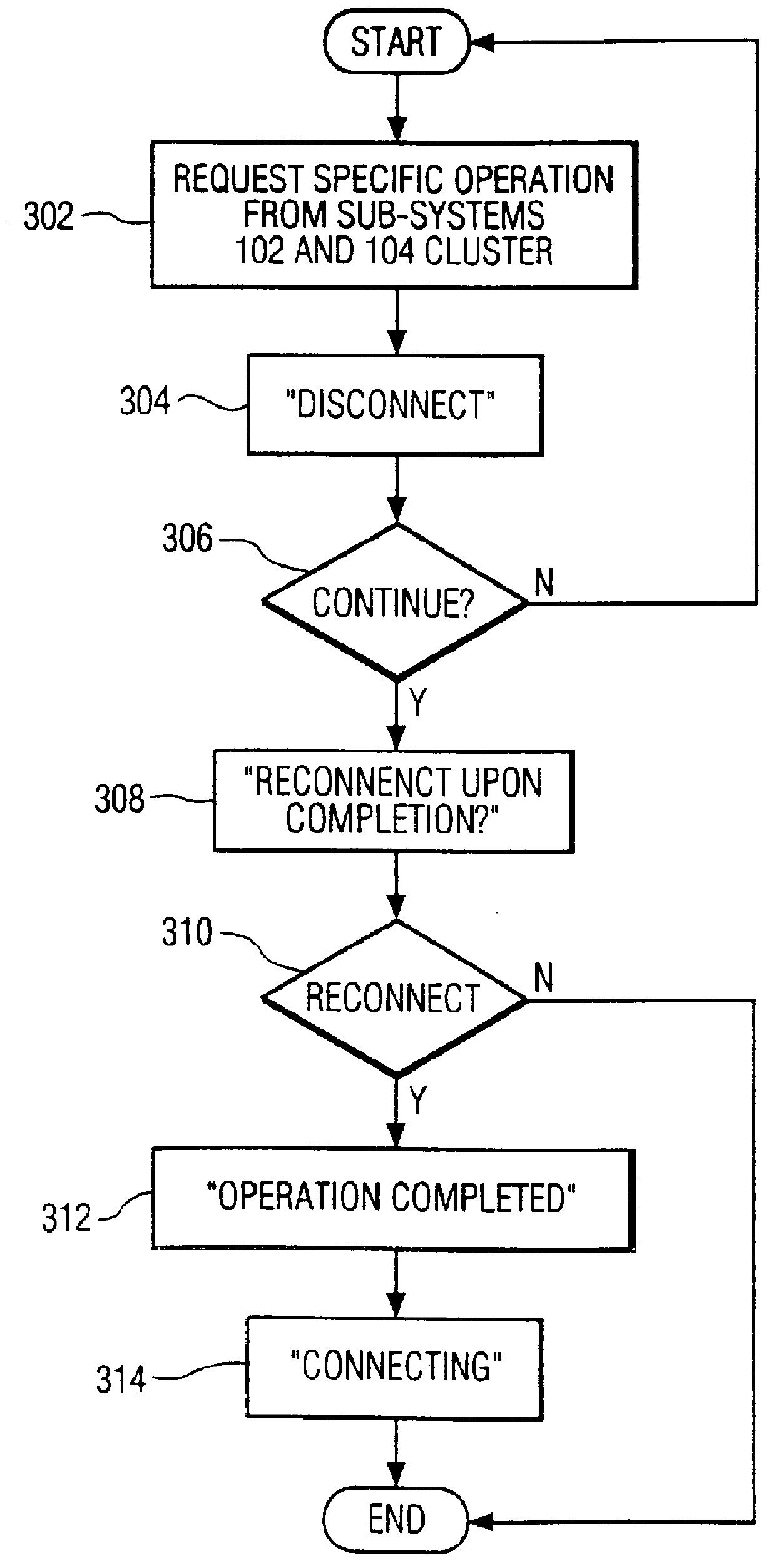

Dynamically disabling and enabling of devices in consumer system with multiple communication protocols

InactiveUS6163817AAvoid confictAvoid controlTelemetry/telecontrol selection arrangementsProgram control using stored programsInformation processingInformation handling system

An information processing system has first and second electronic sub-systems, and control means for controlling the sub-systems. At least the first sub-system has a software representation registered with the control means. The control means changes a state of the first sub-system through interacting with the software representation. The first and second sub-systems are also capable of interacting directly with one another without the control means being involved. To avoid conflicts, at least the first sub-system is capable of de-registering with the control means so as to functionally disable its software representation at the control means.

Owner:U S PHILIPS CORP

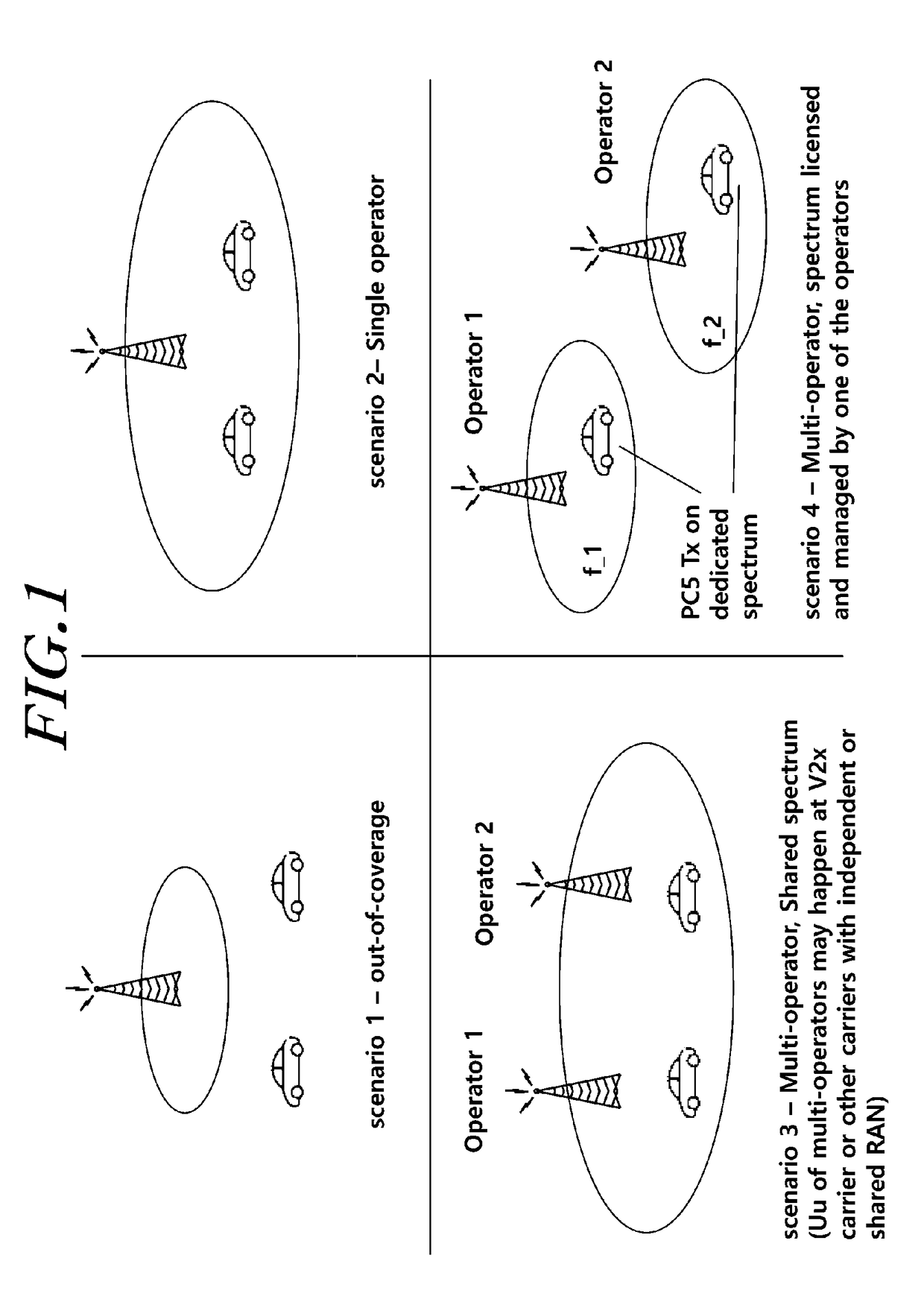

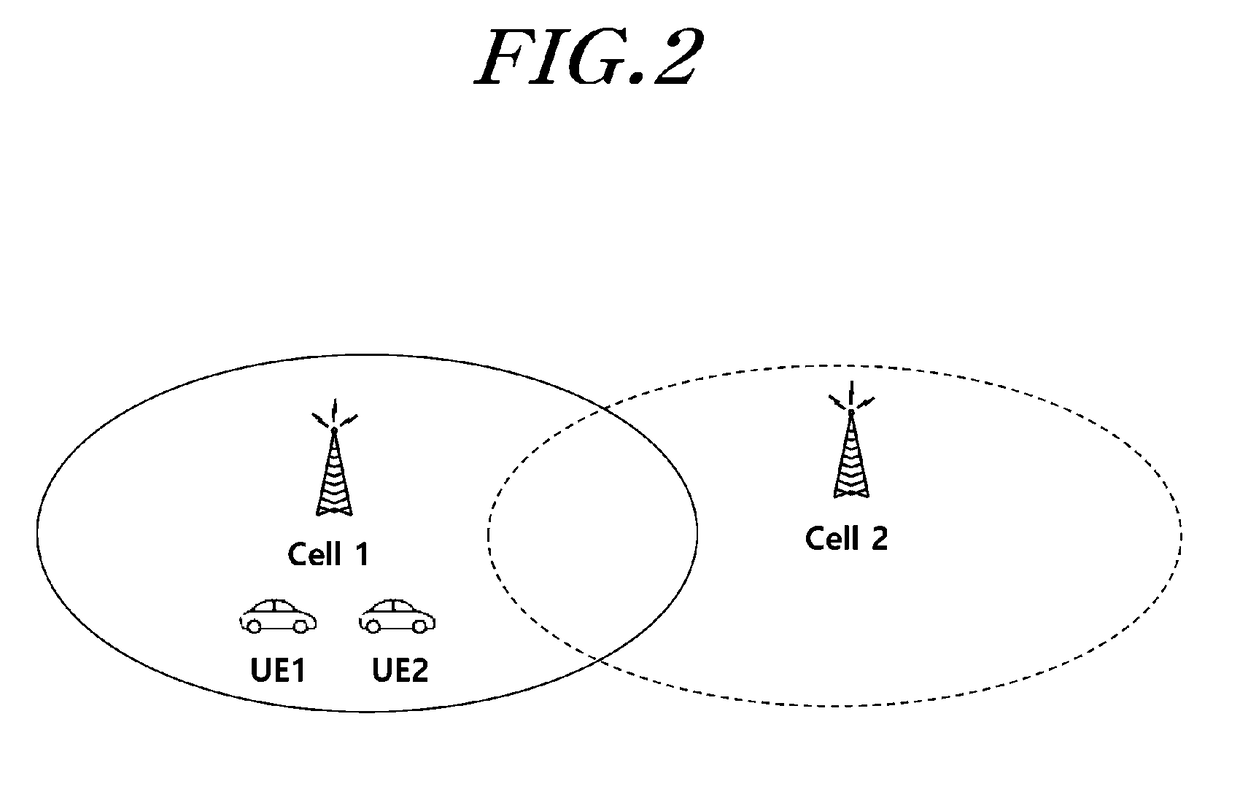

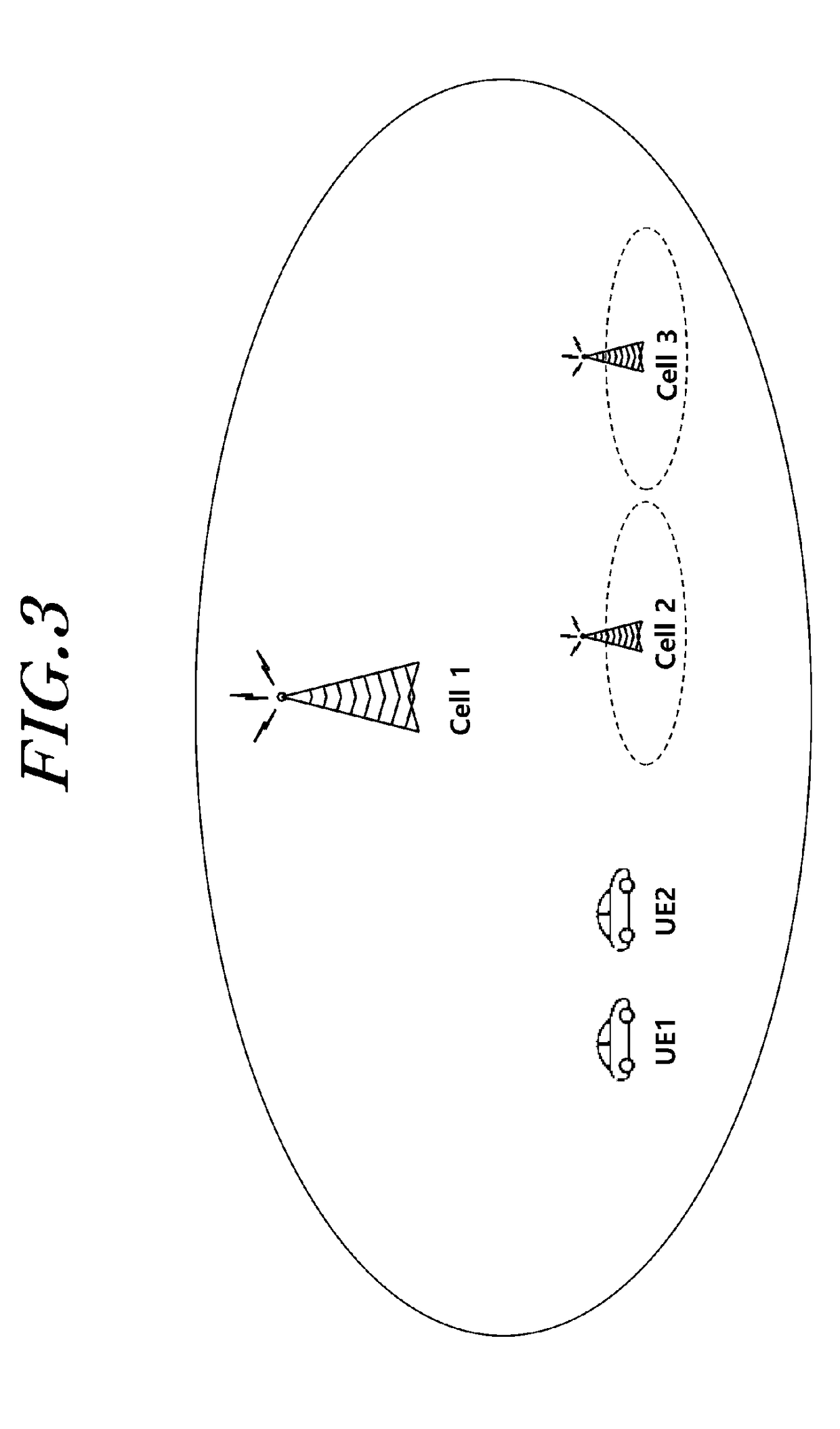

Vehicle to everything communication control method and apparatus therefor

ActiveUS20190045521A1Efficiently providedAvoid resourcesSynchronisation arrangementParticular environment based servicesTelecommunicationsCommunication control

Provided are a method and apparatus for supporting mobile communication network-based vehicle to everything (V2X) communication. The method may include: transmitting, to a base station, terminal assistance information for semi-persistent scheduling (SPS) of radio resources for V2X communication; receiving, from the base station, SPS configuration information generated using the terminal assistance information; and performing V2X communication by using the SPS configuration information.

Owner:KT CORP

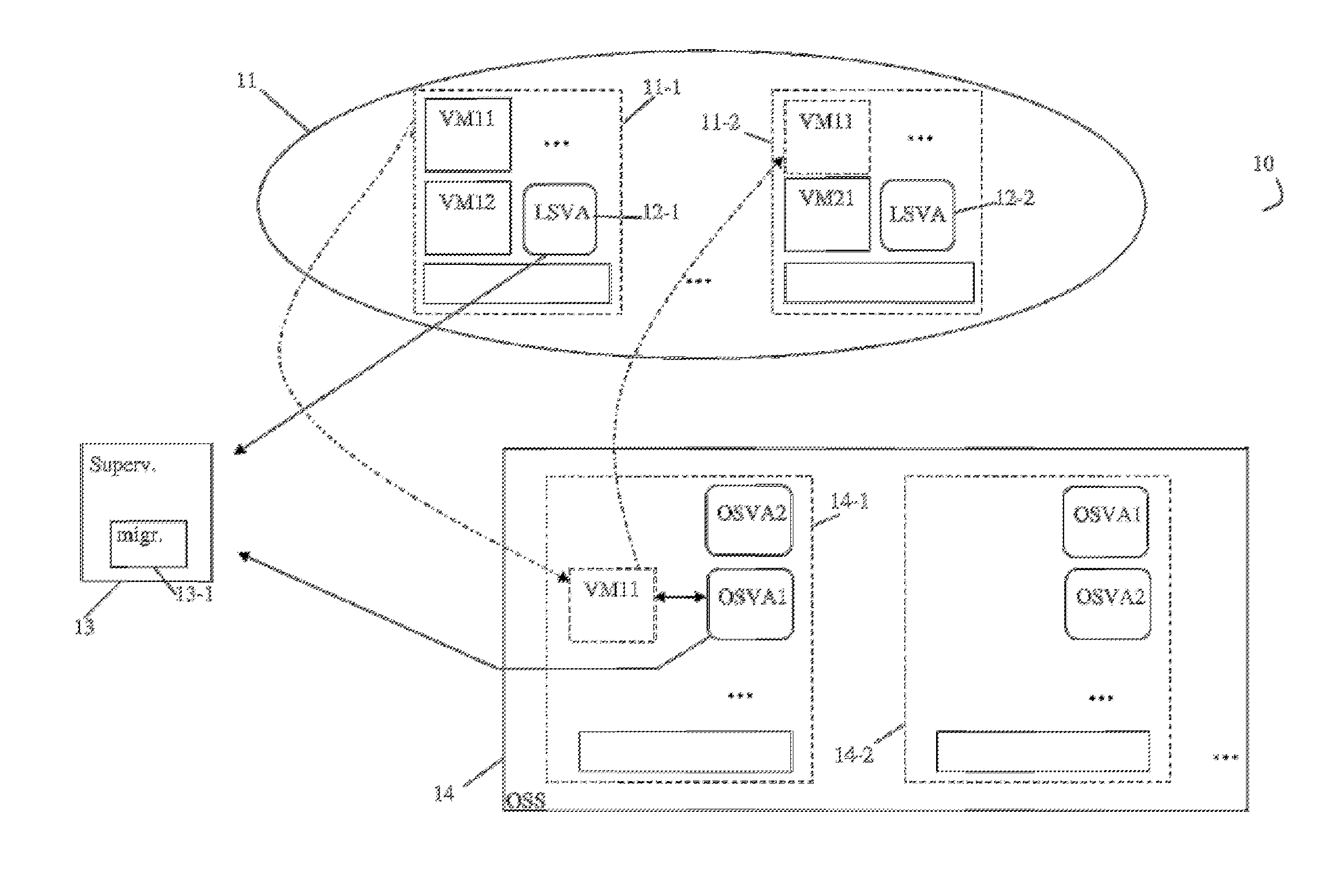

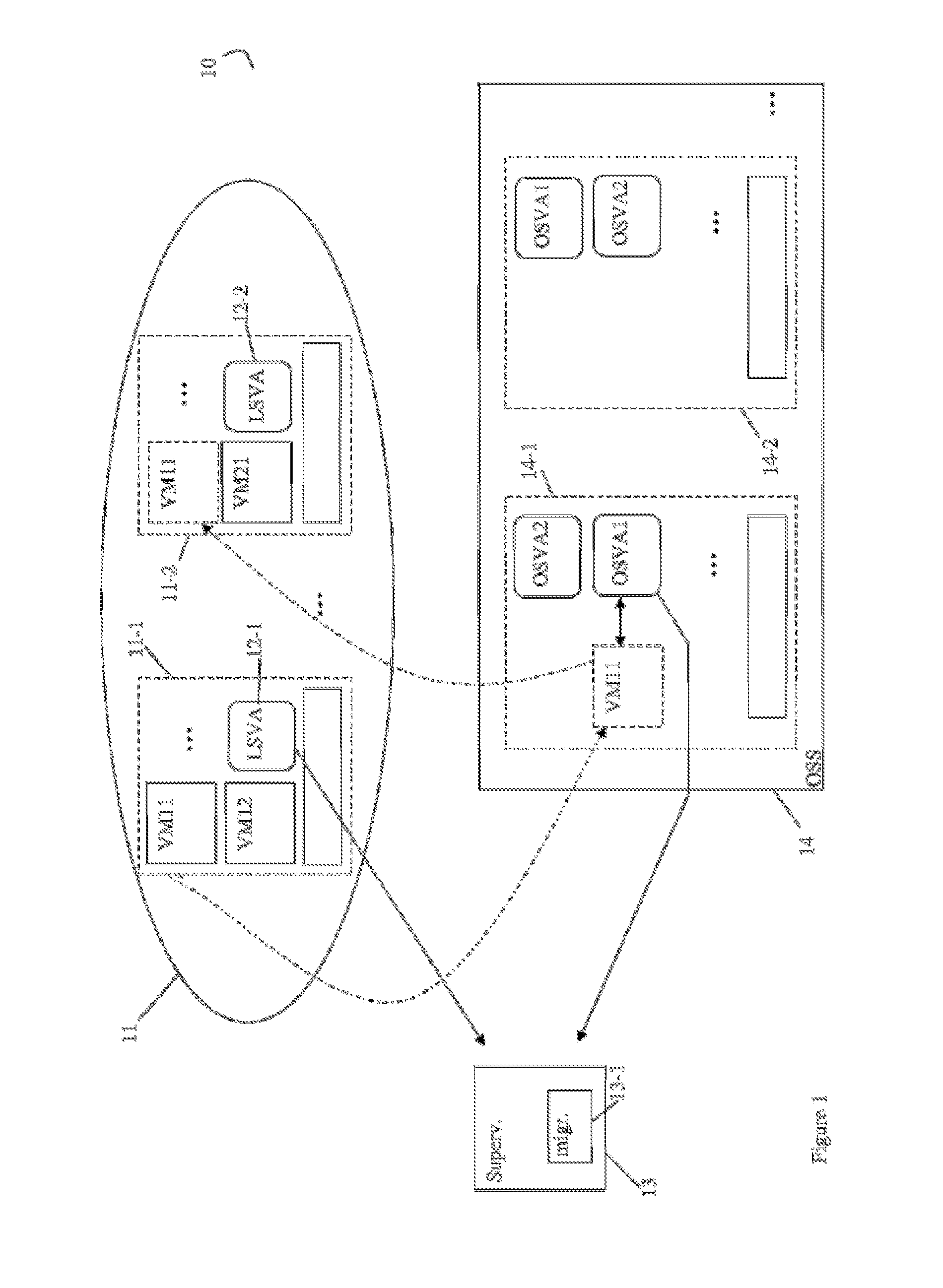

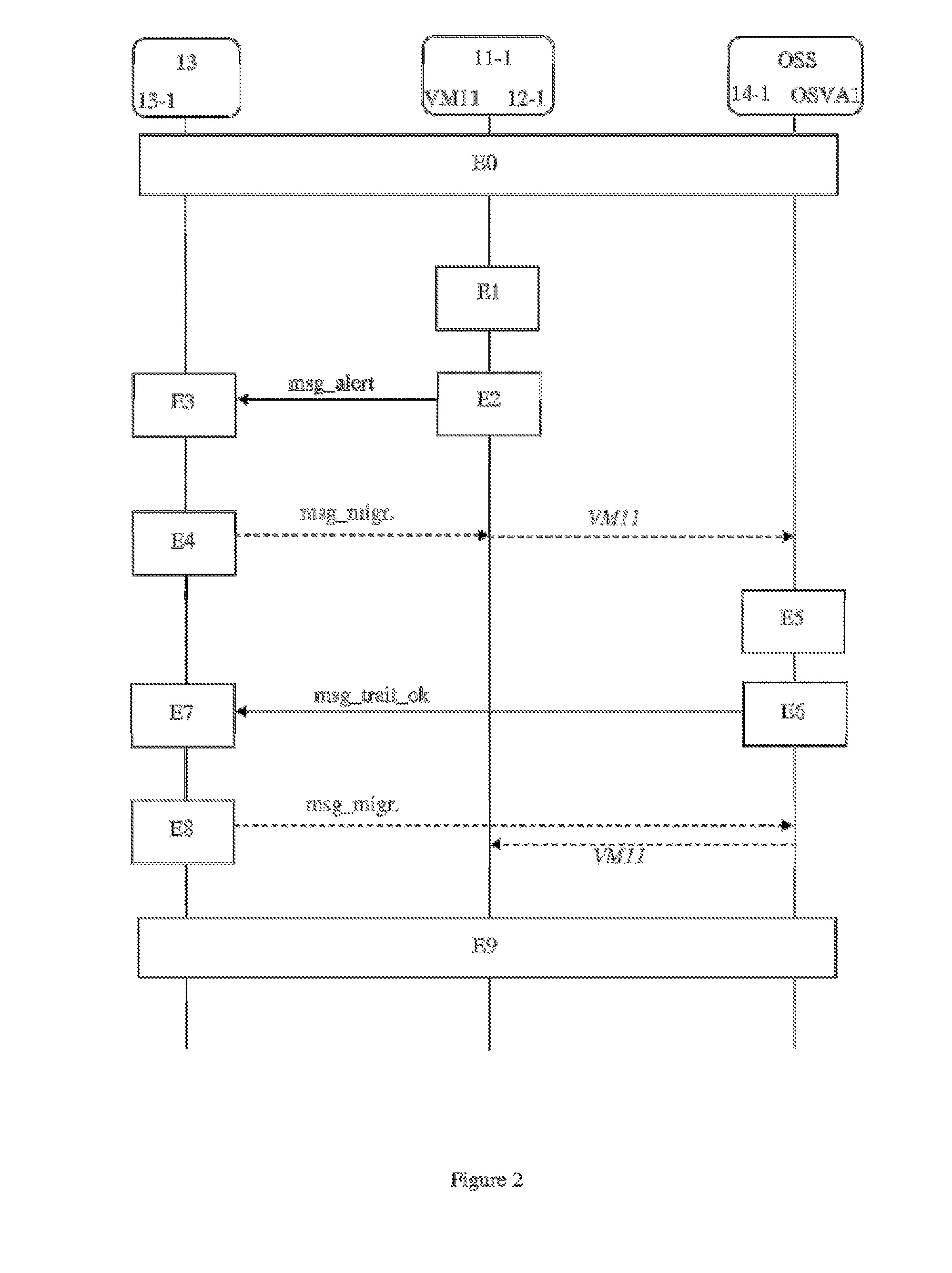

Method for Detecting Attacks and for Protection

ActiveUS20140223556A1RiskIncreased resource requirementMemory loss protectionError detection/correctionSecurity systemVirtual machine

A method is provided for attack detection and protection of a set of virtual machines in a system, which includes at least one first host server hosting said set of virtual machines. The method includes: receiving an attack detection message regarding a virtual machine, triggering a first migration of the virtual machine from the first host server toward a security system, and receiving an attack treatment message regarding the migrated virtual machine.

Owner:ORANGE SA (FR)

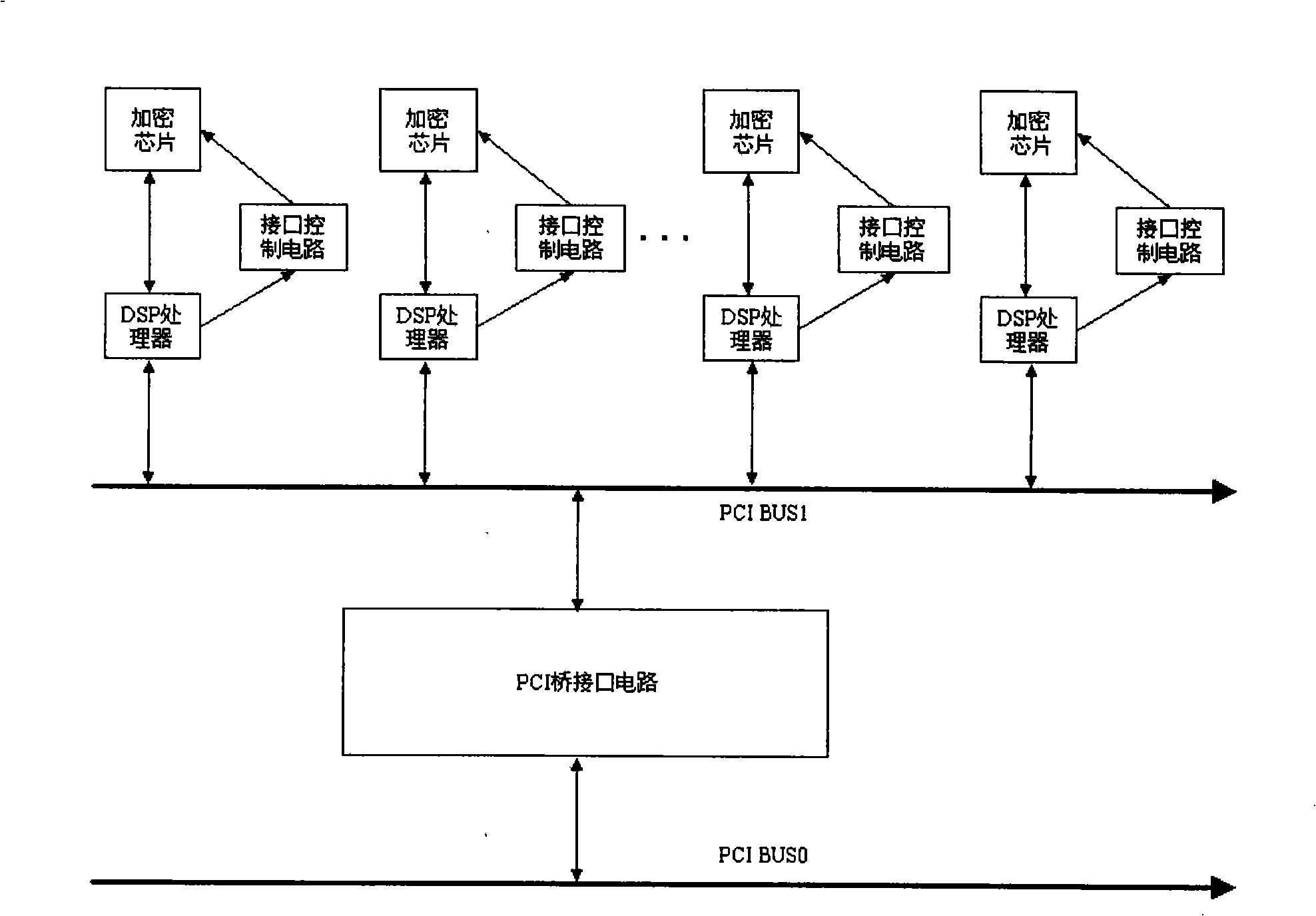

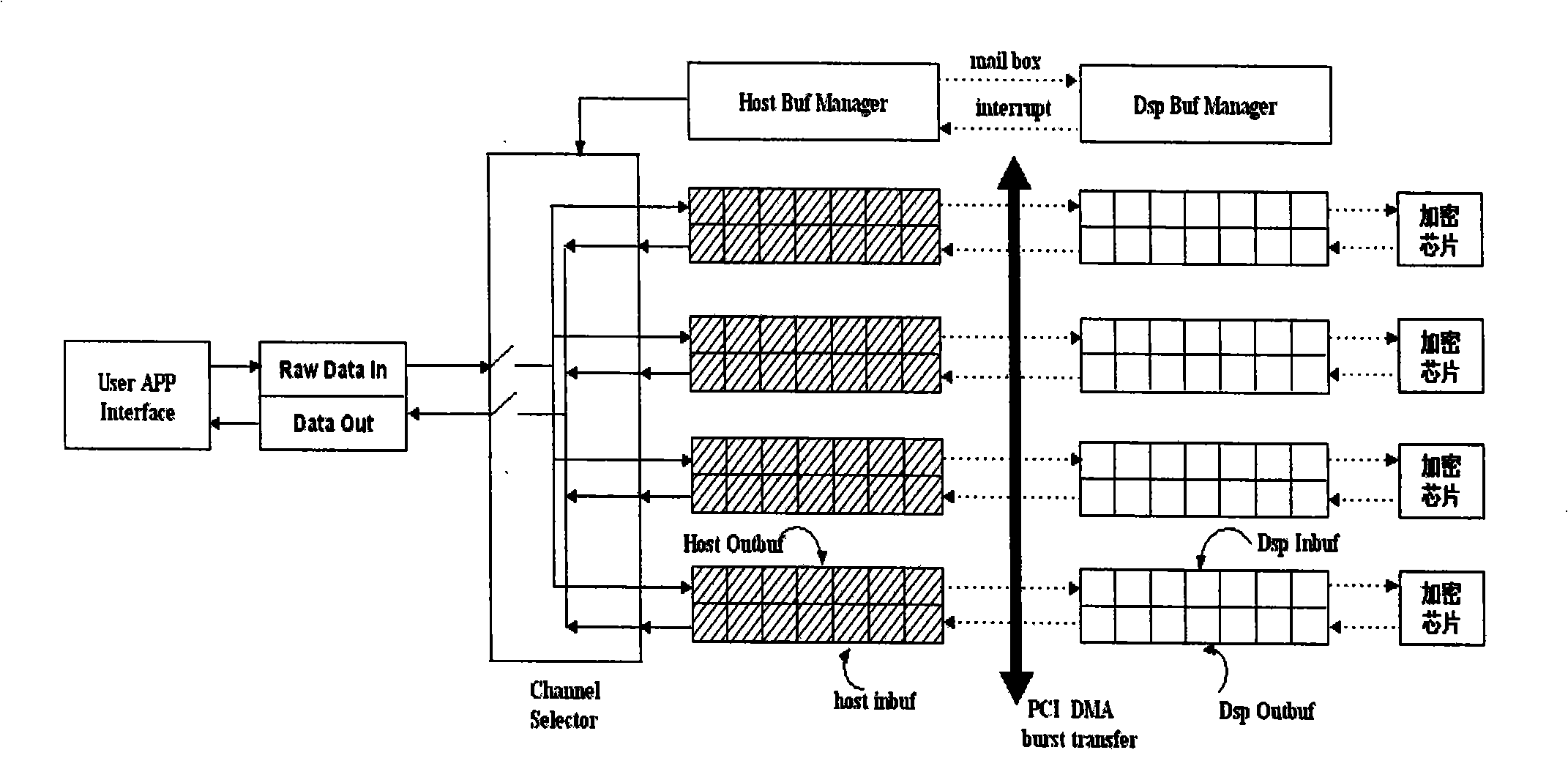

Method for parallel data processing adopting multi- password chip

InactiveCN101290569AFast encryption and decryptionAvoid resourcesConcurrent instruction executionSecuring communicationPasswordDsp processor

The invention relates to a data encryption and decryption technology, in particular to a method adopting the parallel data processing of multi-crypto chips to improve the encryption and decryption speed of a system. A parallel data processing unit for the multi-crypto chips and a high-speed encryption method for the data have the following advantages that: the operation of the system does not occupy extra resource of a main CPU, all the encryption and decryption operations are performed in a DSP processor, and the extreme improvement of the encryption and decryption speed is realized through the parallel processing of a plurality of crypto chips and the DSP.

Owner:STATE GRID ELECTRIC POWER RES INST +1

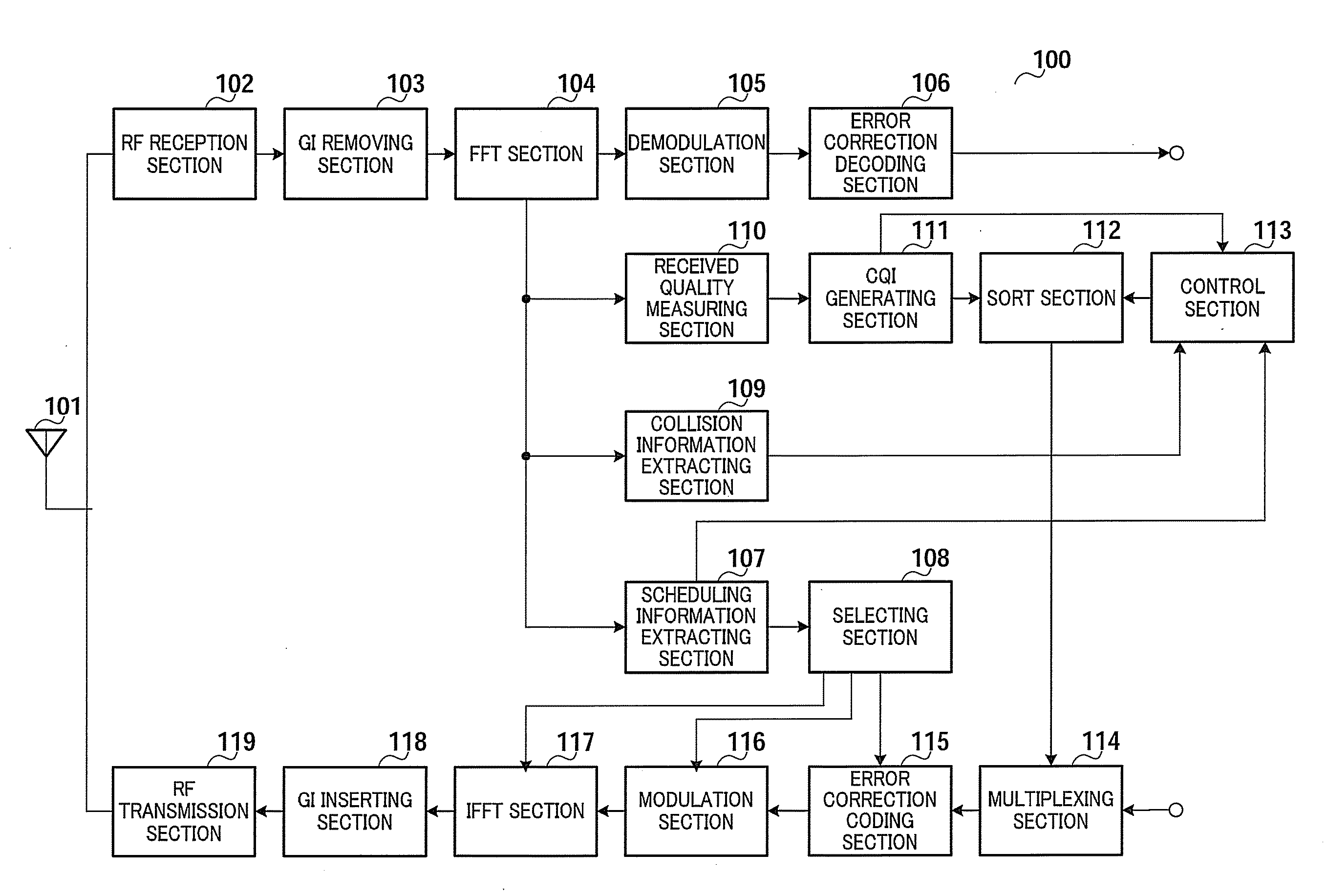

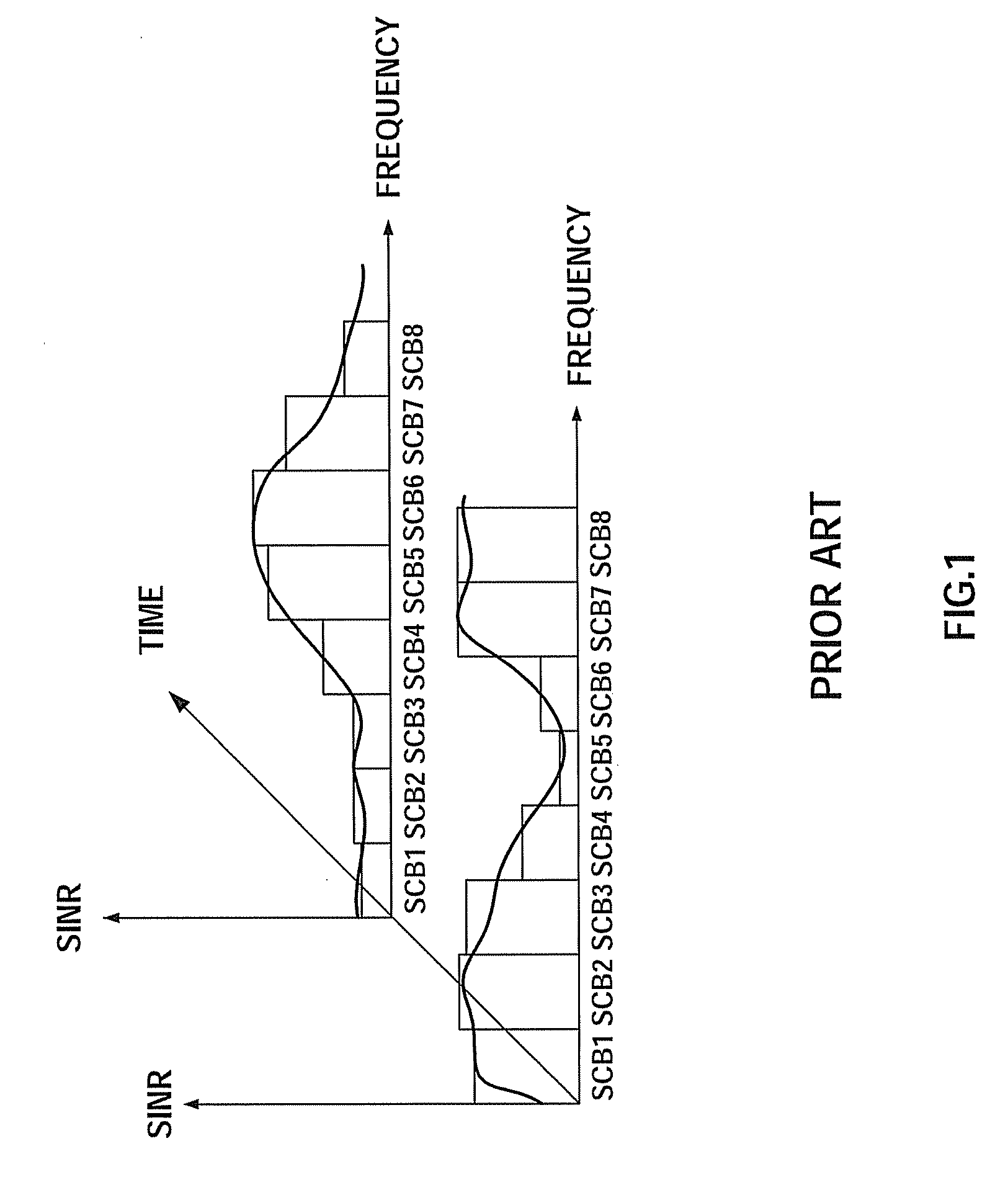

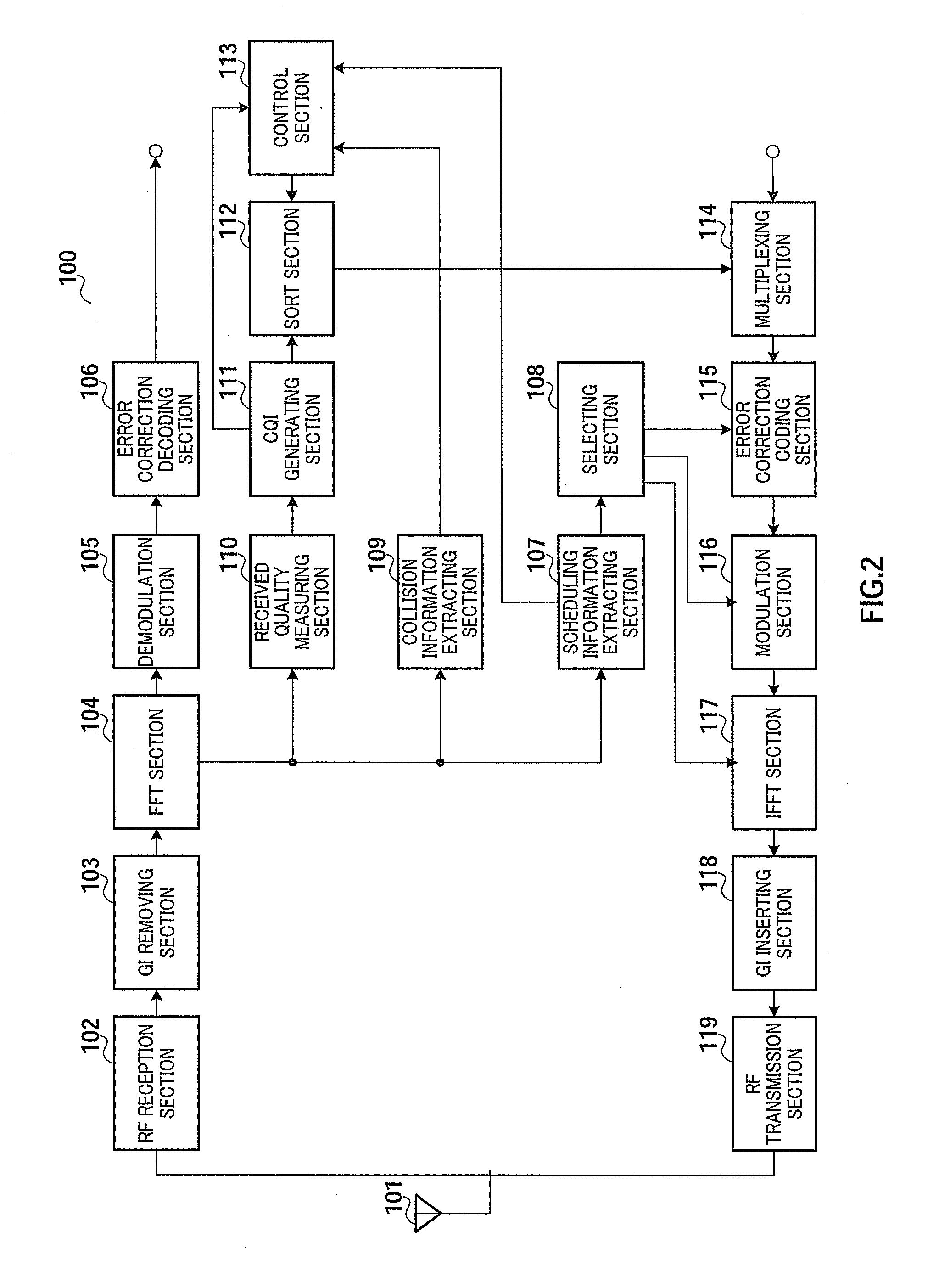

Communication terminal apparatus, base station apparatus and reception quality reporting method

InactiveUS20090147869A1Reduce distractionsAvoid resourcesMultiplex system selection arrangementsSpecial service provision for substationTerminal equipmentEngineering

A communication terminal apparatus that can eliminate the waste of reception quality report, suppress the interference of an upstream network, perform an optimum assignment using a scheduling, prevent the loss of resources, and ensure the fairness of transmission assignment using the scheduling. In this apparatus, a reception quality determining part (110) uses a pilot signal, which is included in a received signal, to determine the reception quality for each of subcarrier blocks. A CQI generating part (111) generates CQIs each of which is the information indicative of a result of the determination by the reception quality determining part (110). A sorting part (112) sorts the CQIs in descending or ascending order of the reception quality. A control part (113) instructs, based on information about the number of subcarrier blocks in which the CQIs have been transmitted, collision information and scheduling information, the sorting part (112) with respect to the number of subcarrier blocks in which the CQIs are outputted.

Owner:INTERDIGITAL PATENT HLDG INC

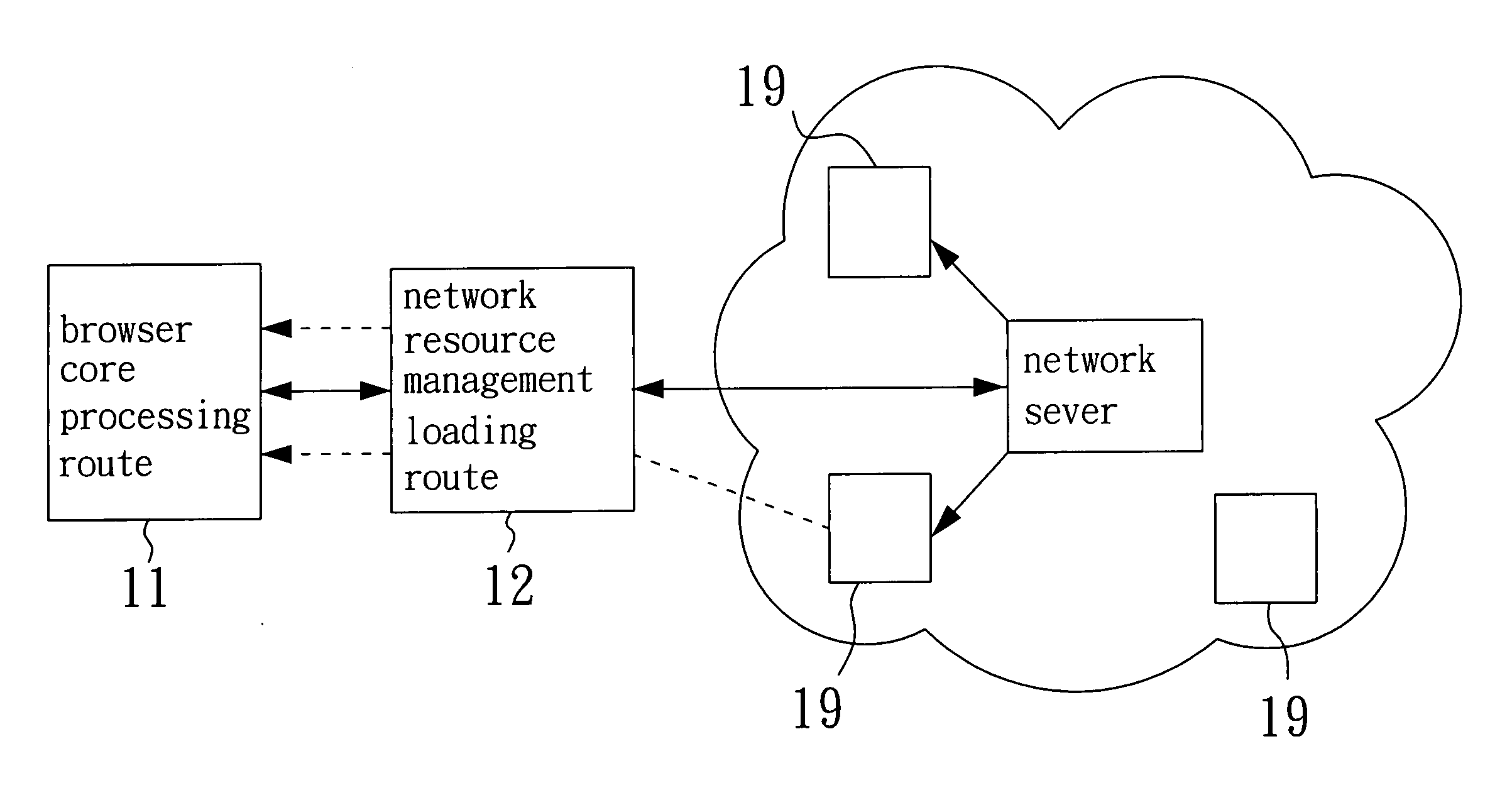

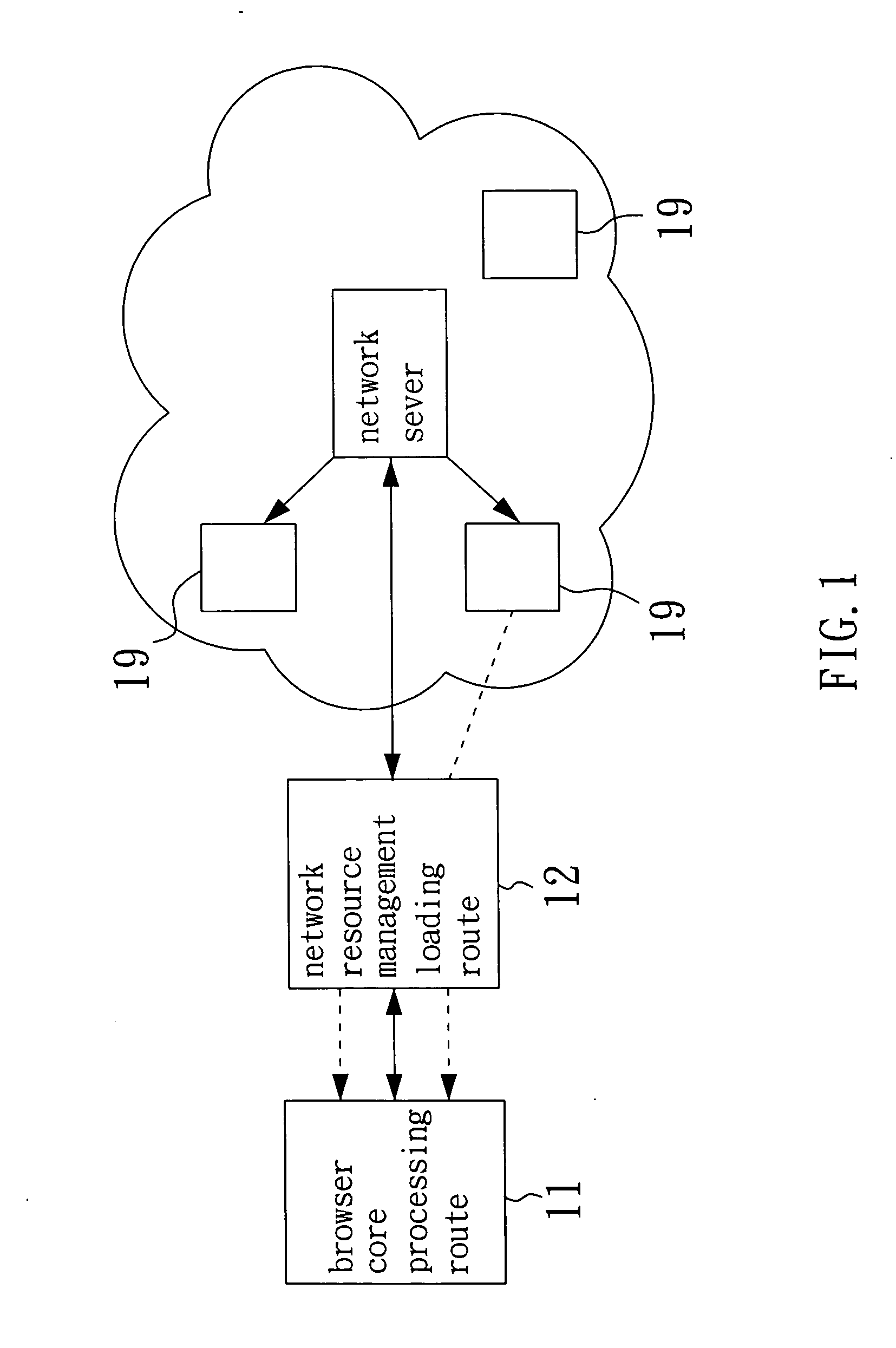

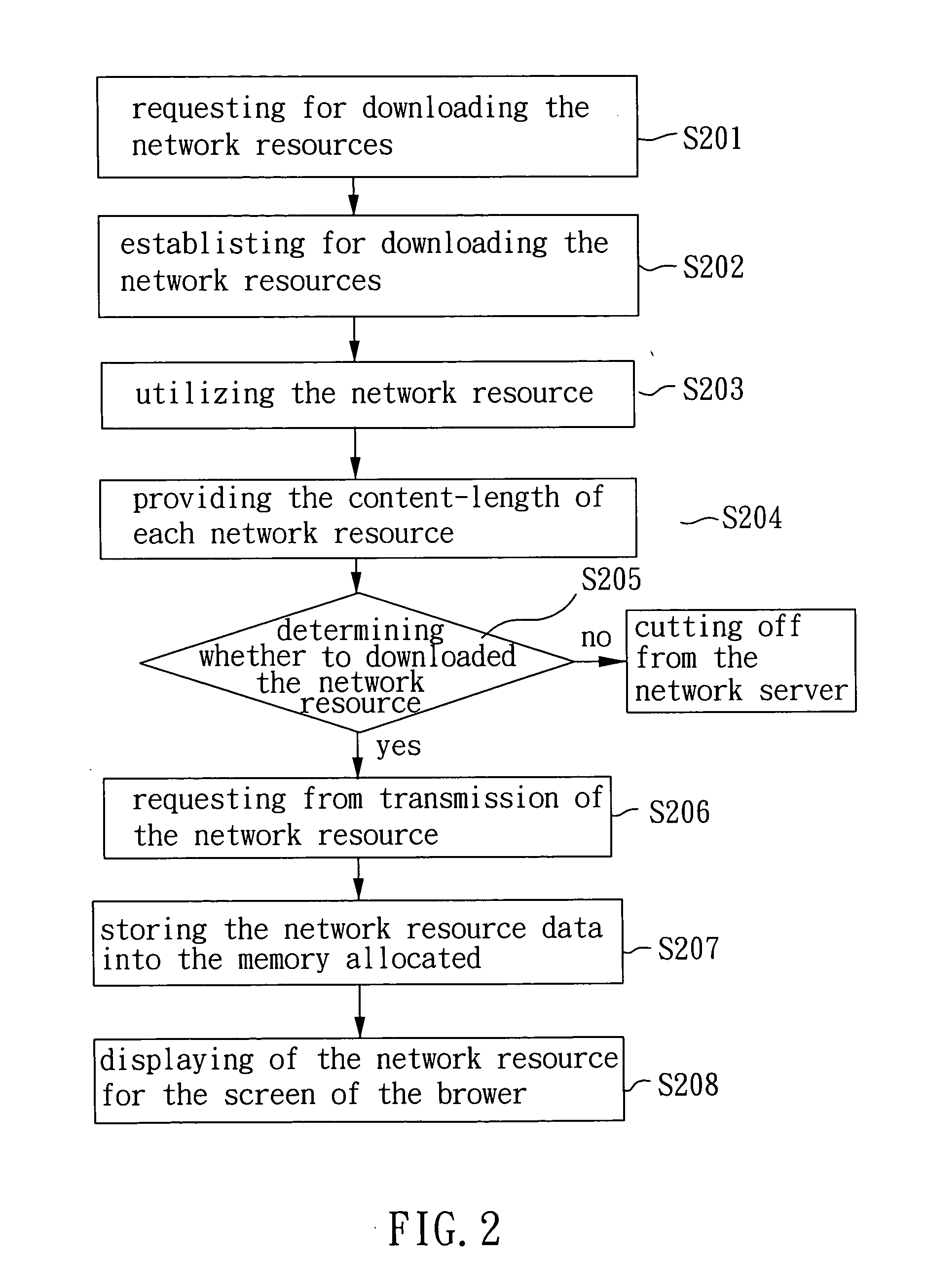

Method and system for dynamically determining web resource to be loaded and saving space

ActiveUS20050138140A1Improve download speedSave spaceDigital data information retrievalError preventionComputer networkWeb page

A method for dynamically determining web resource to be loaded and saving space is provided which determines whether to download a network resource according to a current network bandwidth and available memory space. When a user uses an embedded device in a wireless network environment to download a web-page, the browser only downloads a small part of the network resource to present, and if the user desires to download all network resources, he or she can select to download all network resources, so as to save the download time.

Owner:8324450 DELAWARE +1

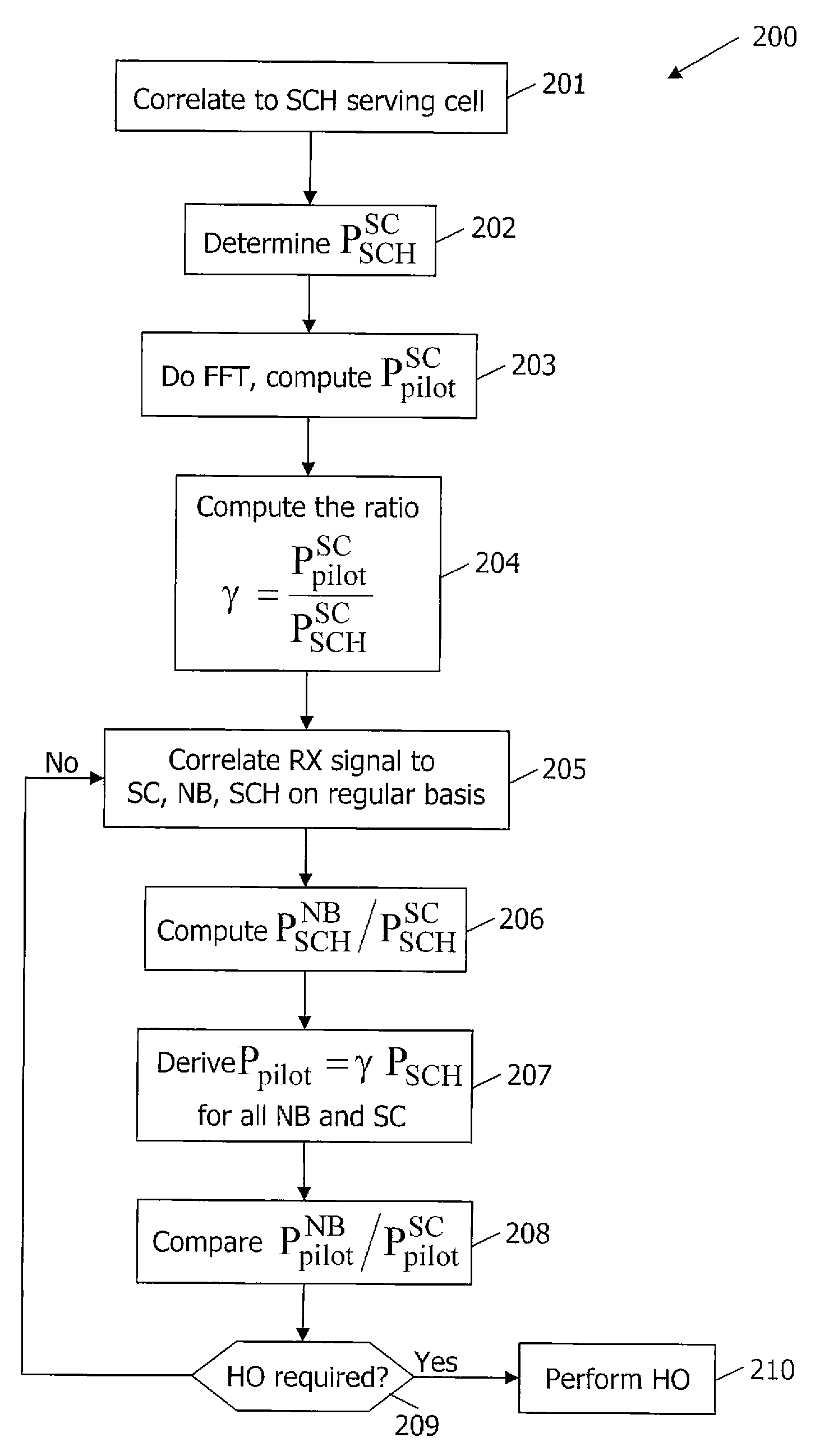

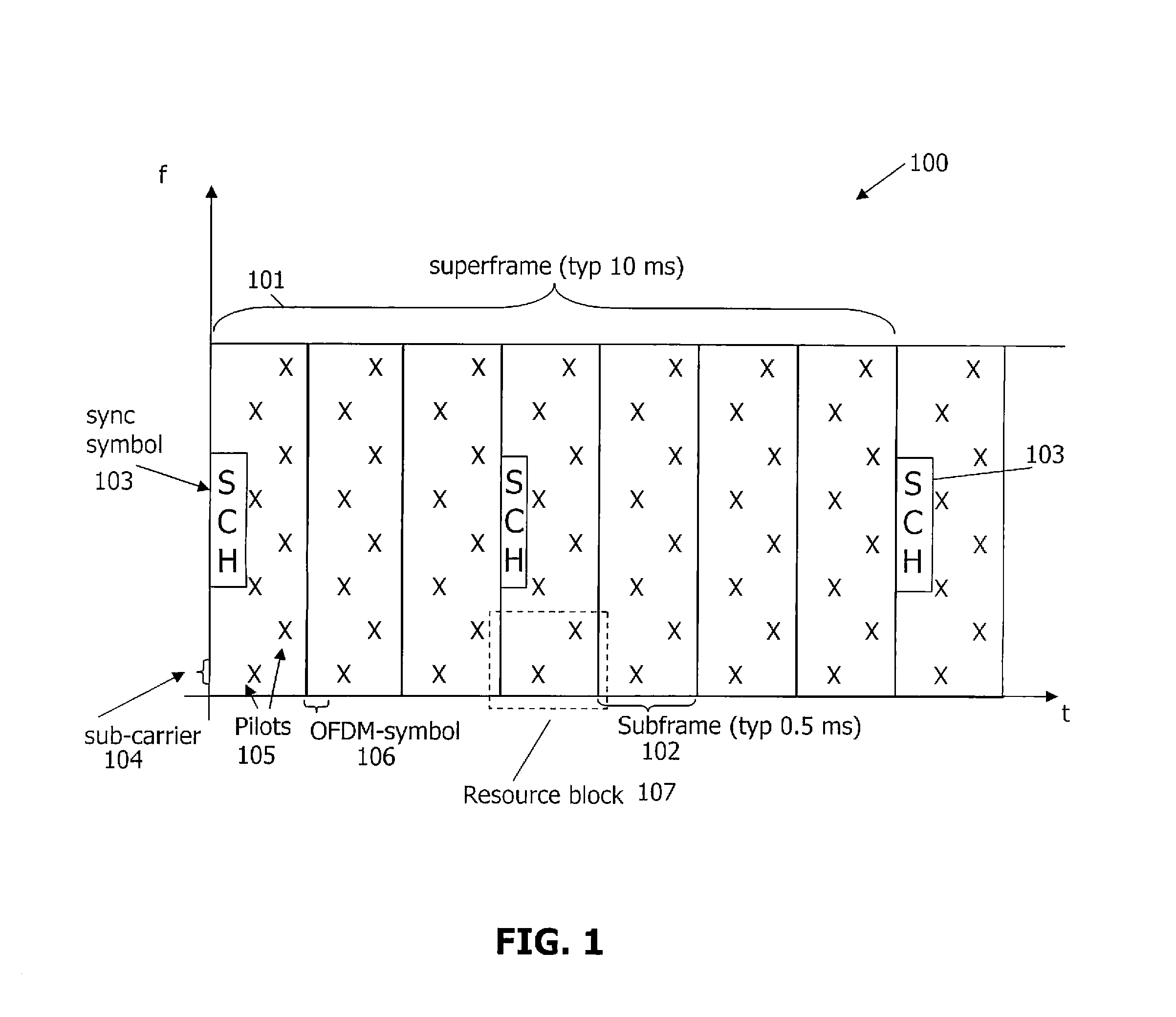

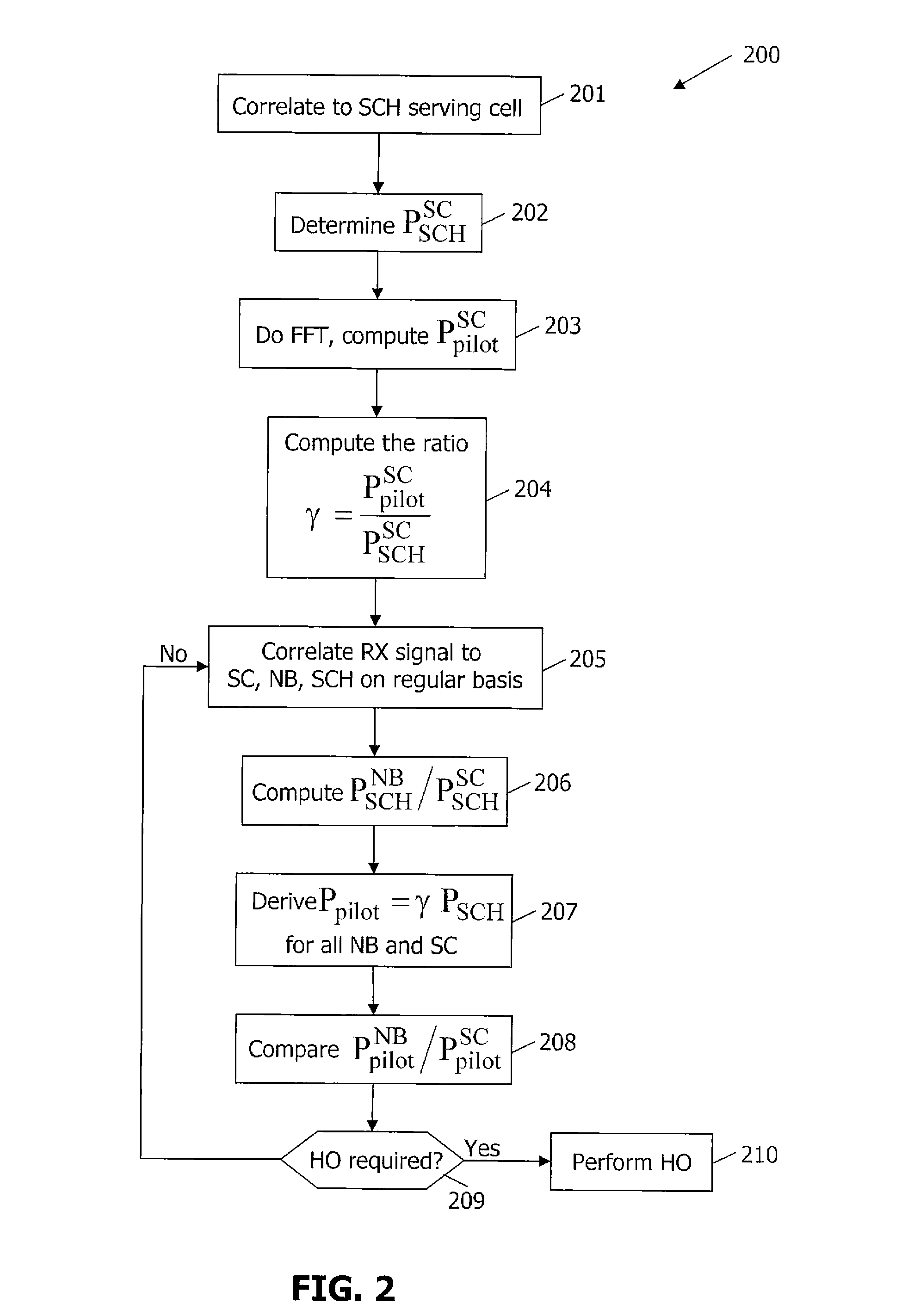

Method and system for using the synchronization channel to obtain measurements in a cellular communications system

ActiveUS20070297324A1Increase capacityReduce pilot overheadSynchronisation arrangementAssess restrictionConstant powerCommunications system

A method and apparatus that utilizes the synchronization channel (SCH) by the user equipment (UE) to obtain time synchronization information and to perform cell search. In order to perform the SCH detection, only a correlation between the known SCH signal and the received sequence is needed, hence the FFT is not involved in the synchronization step. Typically the SCH and pilot symbols are transmitted with a constant power which is the same for all base stations. Hence, based on the serving cell (SC) SCH and pilot symbols, the power relation between these signals is estimated and the ratio applied when performing time synchronization to other cells (i.e. correlation the received sequence with the SCH from that particular NC) to estimate the pilot signal strength for the NB cell.

Owner:TELEFON AB LM ERICSSON (PUBL)

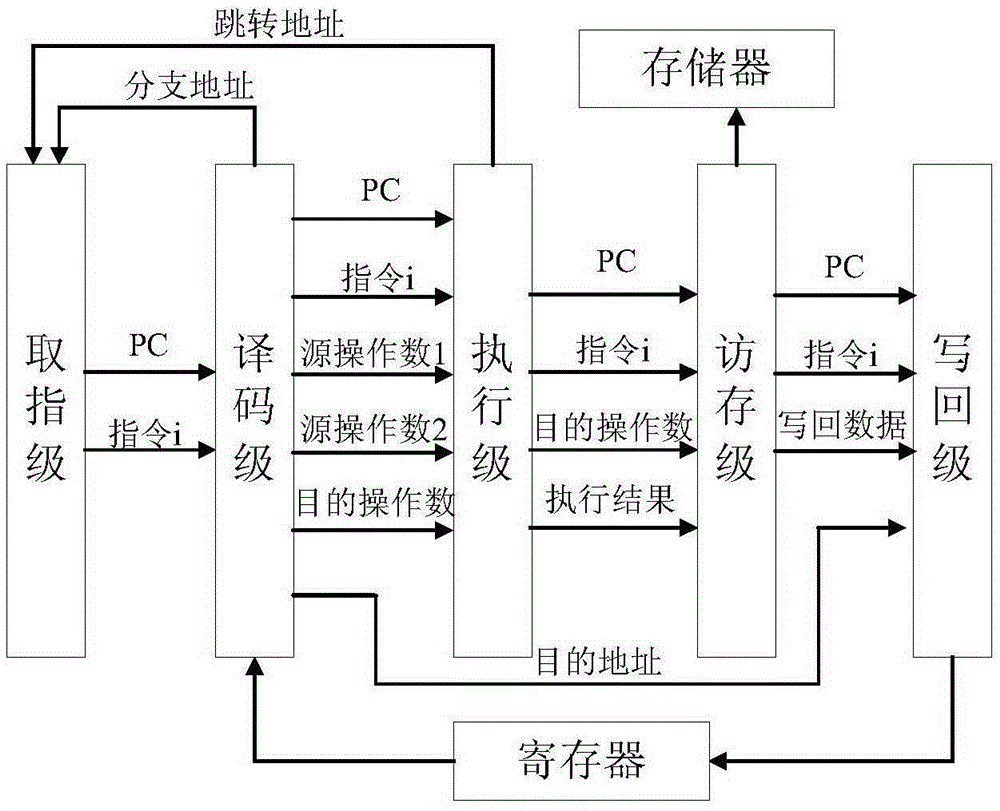

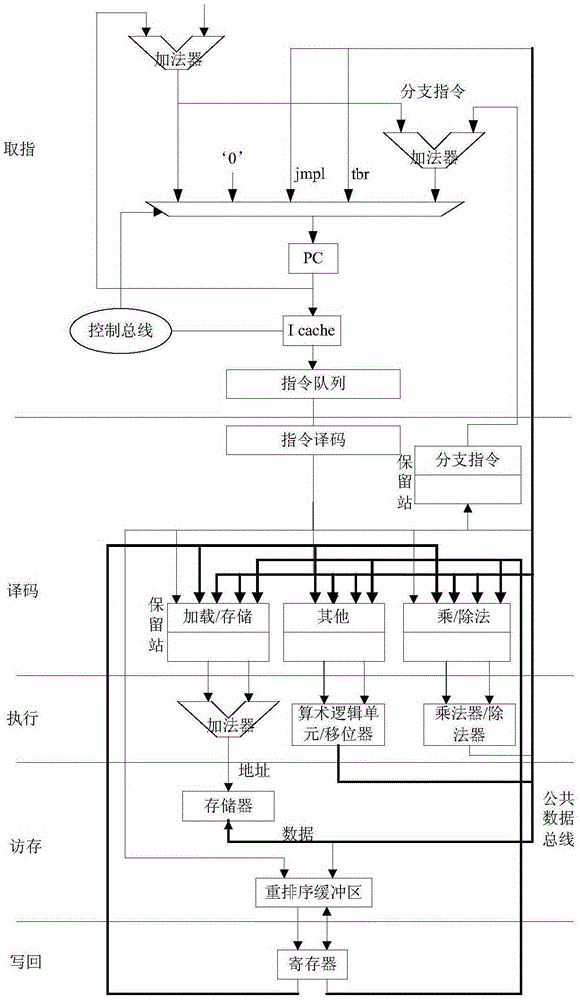

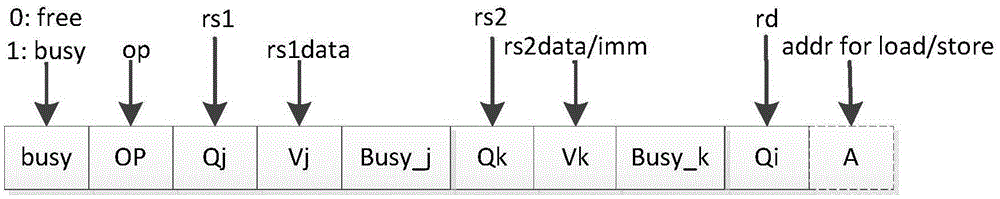

Instruction classified multi-emitting method based on SPRAC V8 instruction set

ActiveCN105426160ASmall area costImprove execution efficiencyMachine execution arrangementsInstruction setRe-order buffer

The invention provides an instruction classified multi-emitting method based on an SPRAC V8 (Scalable Processor Architecture V8) instruction set. According to the method, SPARC V8 instructions are divided into four classes; an SPRAC V8 processor is divided into five flow stages including an instruction fetching stage, a decoding stage, an execution stage, a memory accessing stage and a writing-back stage; the five flow stages are connected through a common data bus; (n-1) instruction fetching paths are added at the instruction fetching stage; (n-1) decoding units are added at the decoding stage; n groups of reservation stations are added between the decoding stage and the execution stage; reordering buffer regions are added between the execution stage and the memory accessing stage; corresponding execution units are added in the execution stage; a multi-emitting five-stage flow line structure is built for the SPRAC V8 processor; the conflict among parallel instructions is detected through the reservation stations; different instructions are processed through different execution units; finally, the instruction execution results are sequentially submitted by the reordering buffer regions; the parallel execution of the instructions is realized; and the processing performance of the SPRAC V8 processor is improved.

Owner:BEIJING MXTRONICS CORP +1