Instruction classified multi-emitting method based on SPRAC V8 instruction set

A multi-launch, instruction set technology, applied in program control design, instrumentation, electrical digital data processing, etc., to achieve the effect of improving processing efficiency, ensuring correctness, and small area cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

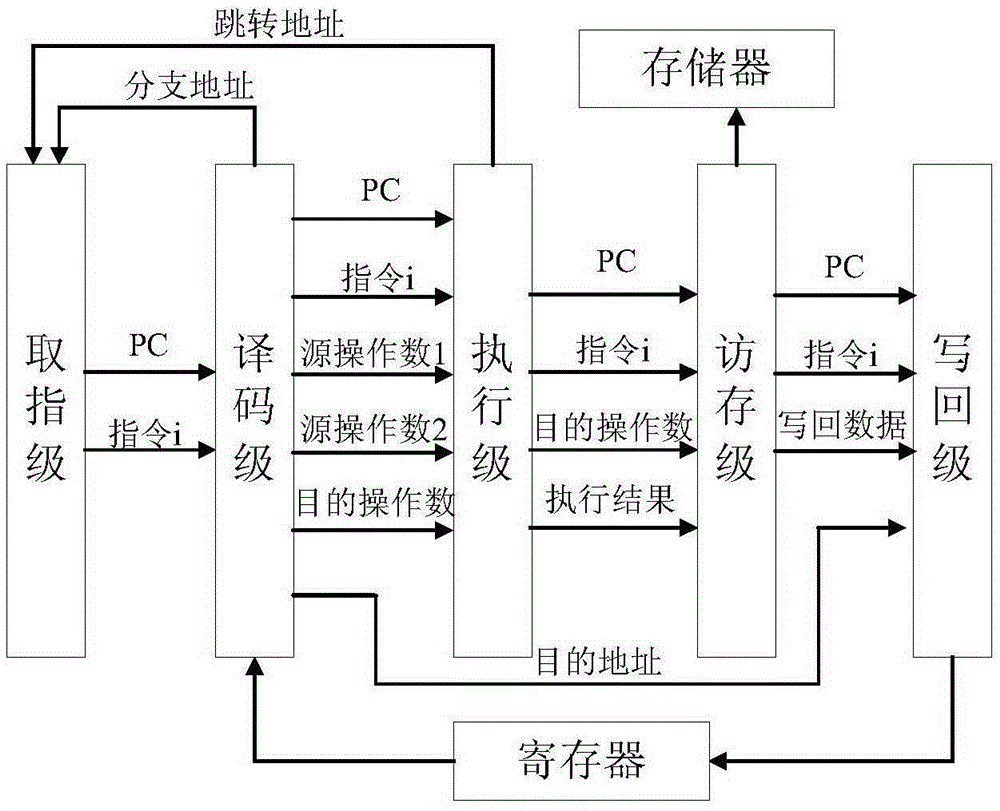

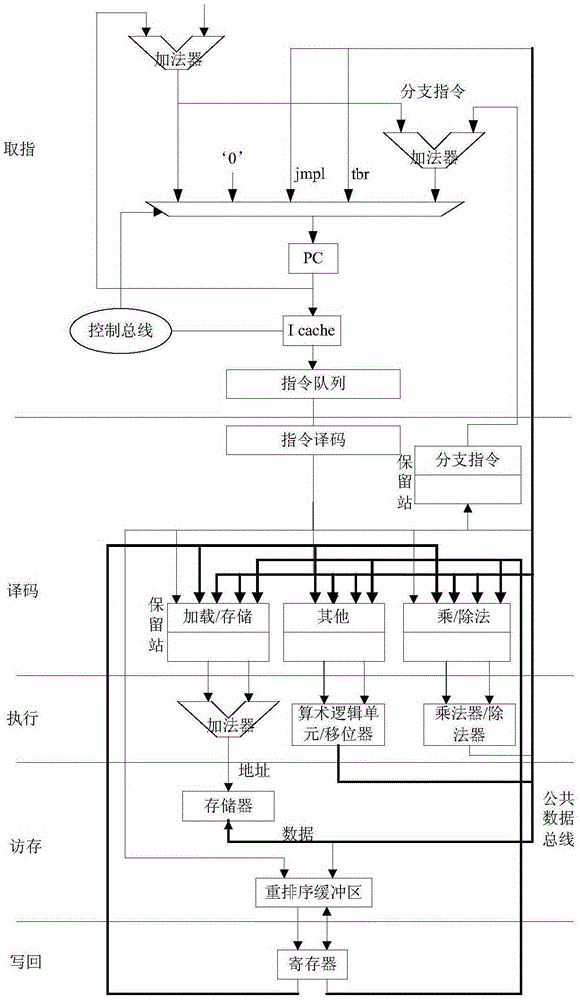

[0079] When n=4, what the inventive method realized was four emission five-stage pipeline processors, and its structural block diagram is as follows figure 2 shown.

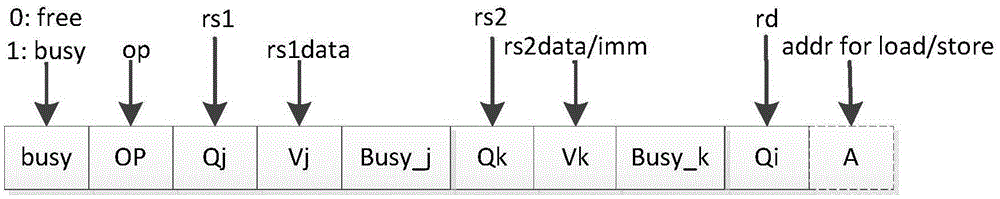

[0080] The five pipeline stages are connected by a common data bus, 3 instruction fetch channels are added at the instruction fetch stage, 3 decoding units are added at the decoding stage, and 4 sets of reservation stations are added between the decoding stage and the execution stage. The group reservation station corresponds to a class of instructions; a reordering buffer is added between the execution level and the memory access level; the instructions to be executed include load / store instructions, multiplication / division instructions, branch instructions and arithmetic logic instructions, according to the instructions to be executed For the arithmetic operations done at the execution level, an adder and a shifter are added to the execution level on the original basis.

[0081] The instruction fetch stage re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More