CMOS (complementary metal oxide semiconductor) circuit of memory

A memory and MOS tube technology, applied in static memory, read-only memory, information storage, etc., can solve problems such as reliability risks of high-voltage functional circuits, reduce hot carrier injection effects, improve circuit reliability, and improve endurance The effect of high pressure performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

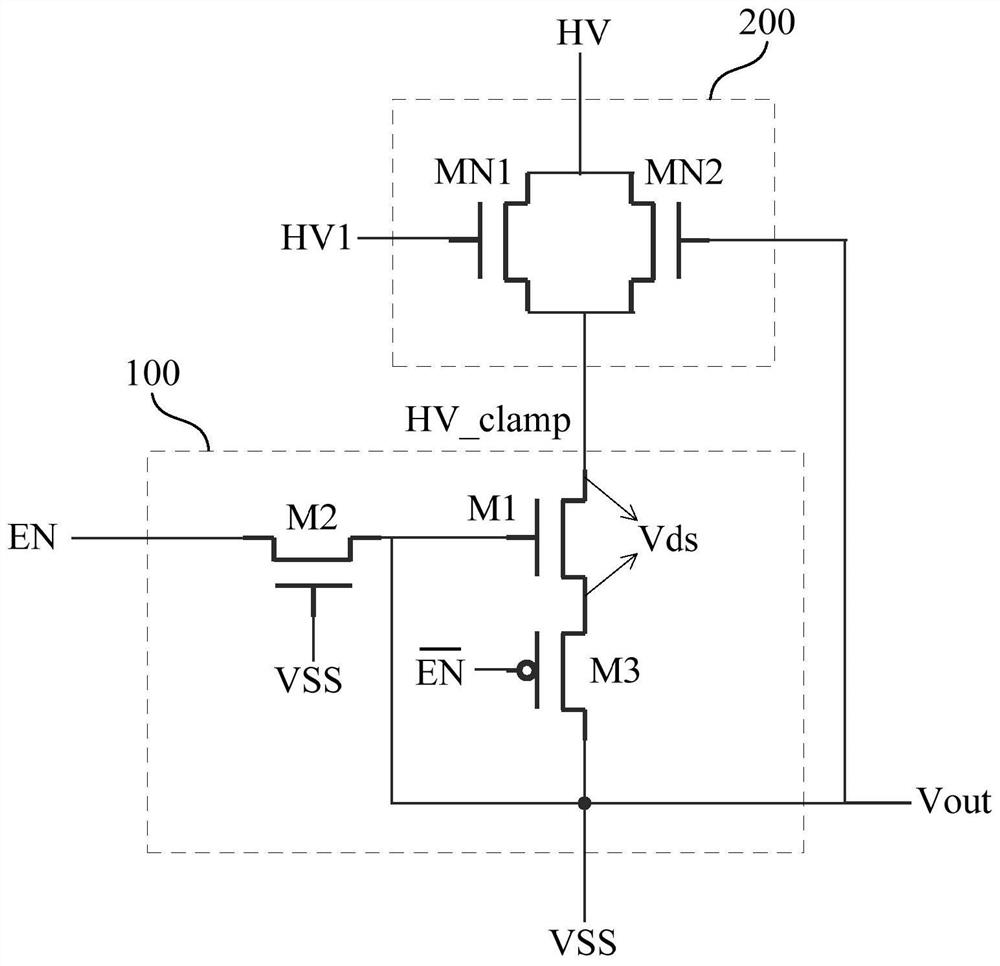

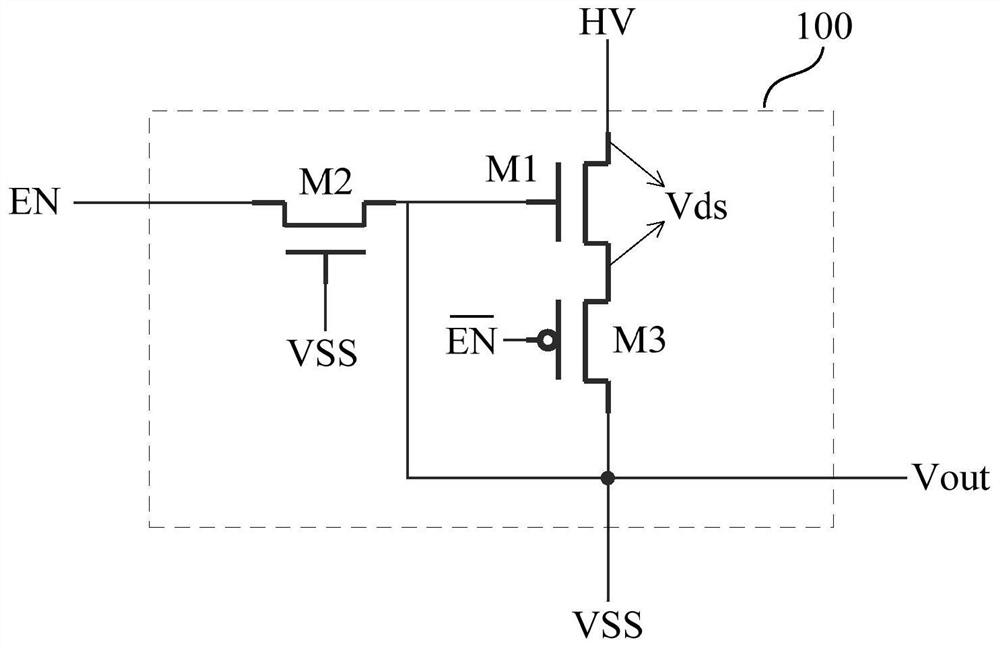

[0029] Such as figure 1 As shown, this embodiment provides a memory CMOS circuit, and the memory CMOS circuit includes:

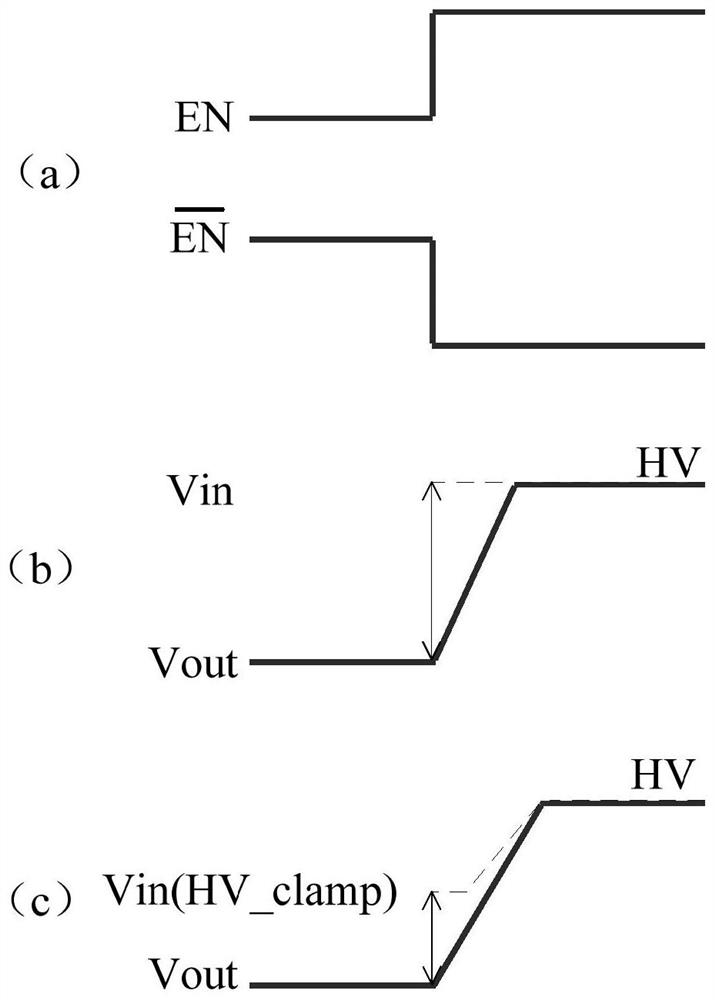

[0030] The high-voltage functional circuit 100 includes at least one MOS transistor, wherein the source terminal or drain terminal of one of the MOS transistors M1 is connected to the input high voltage HV; the high-voltage functional circuit 100 is used to realize that when the enable signal is valid, its output voltage gradually Increase and reach the maximum value HV;

[0031] The auxiliary clamping circuit 200 is arranged between the input high voltage HV and the source terminal or the drain terminal of the MOS transistor M1, and is used for inputting the source terminal or the drain terminal of the MOS transistor M1 during the rising phase of the output voltage. The voltage is clamped so that the clamping voltage HV_clamp is smaller than the input high voltage HV.

[0032] As an example, the high voltage functional circuit 100 includes one of a switc...

Embodiment 2

[0041] Such as Figure 4 As shown, the difference between this embodiment and Embodiment 1 is that the auxiliary clamp circuit 200 in this embodiment further includes: at least one third depletion-type high-voltage NMOS transistor MN3, and the third depletion-type high-voltage NMOS transistor MN3 The first connection end of the first depletion-type high-voltage NMOS transistor MN1 is connected to the first connection end of the first depletion-type high-voltage NMOS transistor MN1, and the second connection end of the third depletion-type high-voltage NMOS transistor MN3 is connected to the first depletion-type high-voltage NMOS transistor MN3. The second connection terminal of the transistor MN1 is connected, and the gate terminal of the third depletion-type high-voltage NMOS transistor MN3 is connected to another preset voltage HV2; wherein, the gate terminal of the third depletion-type high-voltage NMOS transistor MN3 is connected to The preset voltage HV2 is smaller than t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More