Dual-Rail Precharge Logic Cell Architecture

A logic unit, pre-charging technology, applied in the direction of logic circuits with logic functions, etc., can solve the problem of small area cost and so on

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

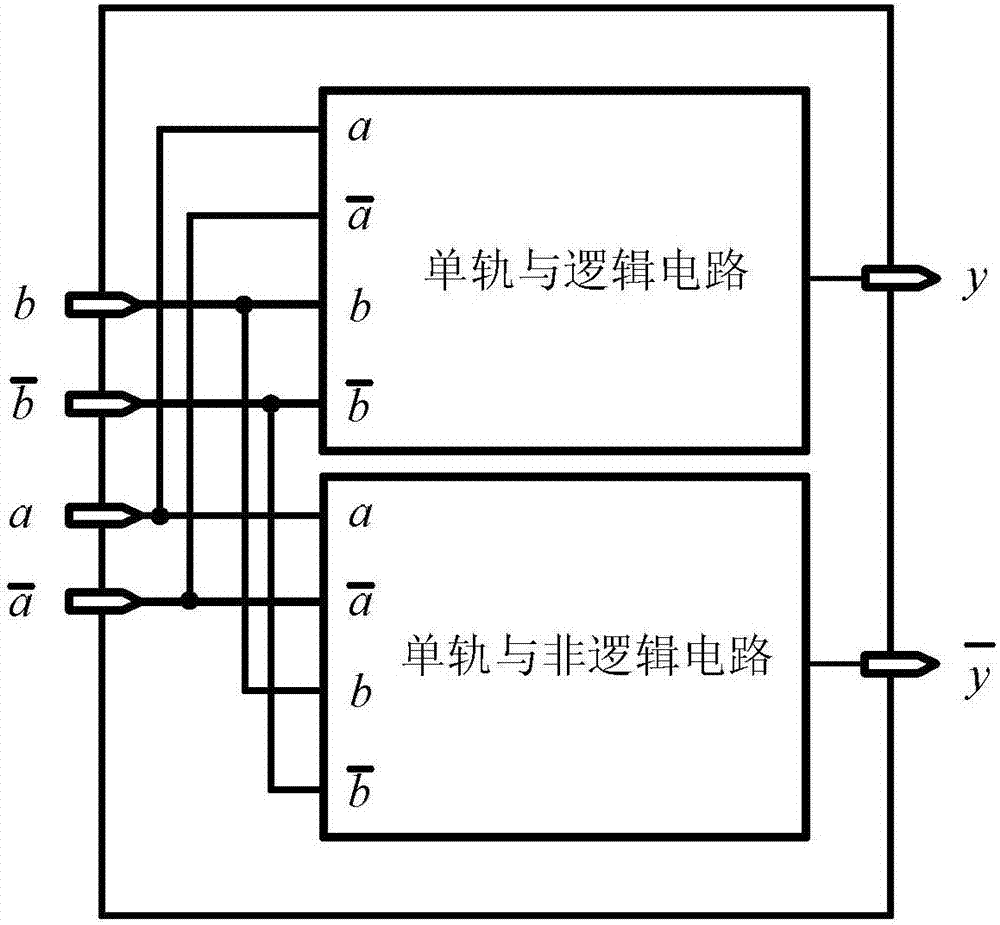

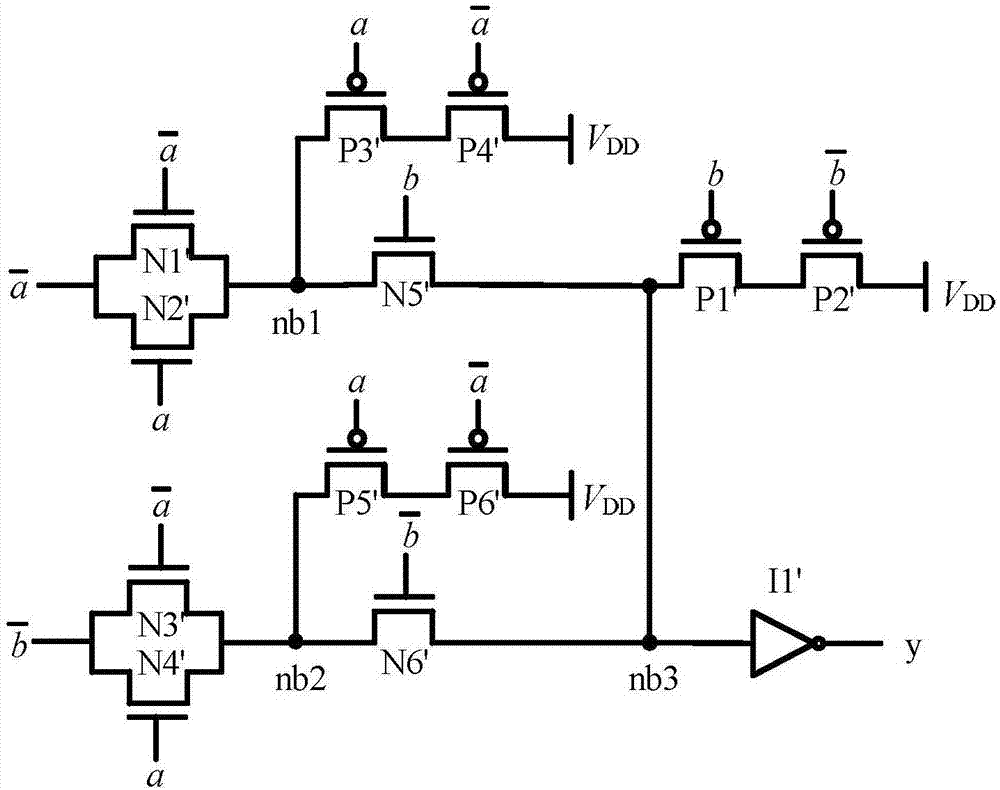

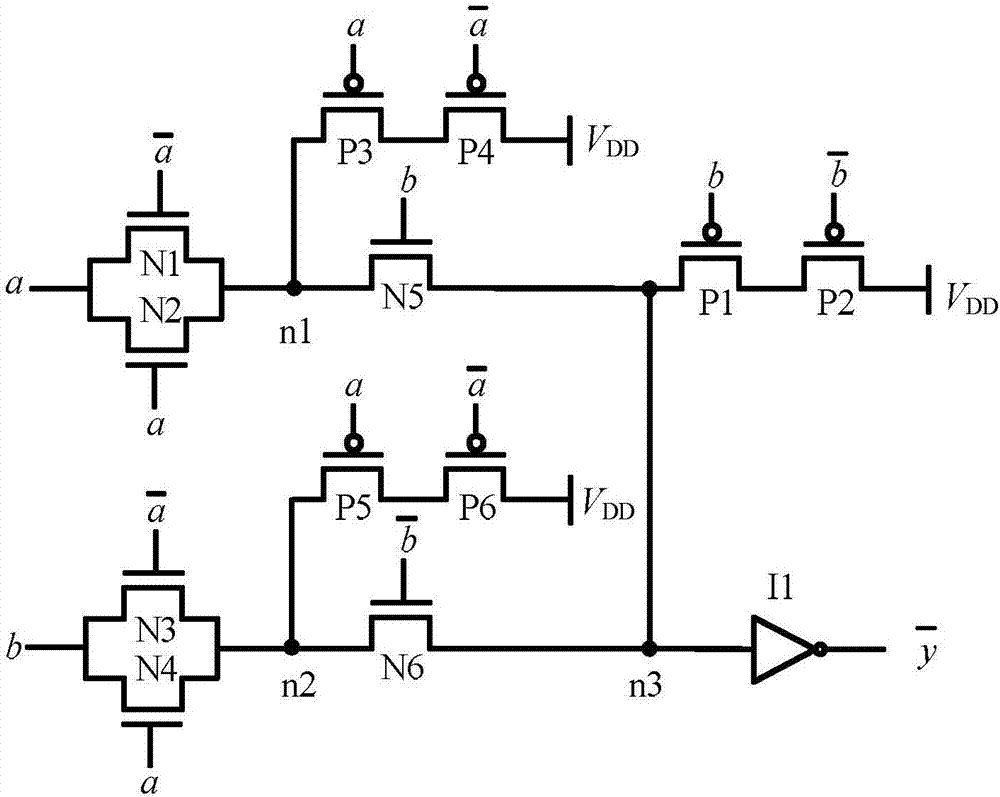

[0029] Specific implementation mode one: the following combination Figure 1 to Figure 3 Describe this embodiment mode, the dual-rail precharge logic unit structure described in this embodiment mode, it comprises monorail and logic circuit and monorail and non-logic circuit; Both monorail and logic circuit and monorail and non-logic circuit have four input ends, connect respectively Four input signals a, b and The output signal y of the single-rail AND logic circuit is the AND logic result of the input signals a and b; the output signal of the single-rail AND non-logic circuit is the AND logic result of input signals a and b;

[0030] input signal a, b and Both are 0, the logic unit is in the precharge state; the input signal a and are complementary signals, and b and When it is also a complementary signal, the logic unit is in the logic operation state;

[0031] The single rail and logic circuit includes NMOS transistor N1', NMOS transistor N2', NMOS transistor ...

specific Embodiment approach 2

[0049] Specific implementation mode two: the following combination Figure 4 to Figure 6 Describe this embodiment mode, the dual-rail precharge logic unit structure described in this embodiment mode, it comprises monorail or logic circuit and monorail or non-logic circuit; Both monorail or logic circuit and monorail or non-logic circuit have four input ends, connect respectively Four input signals a, b and The output signal y of the single-rail OR logic circuit is the OR logic result of the input signals a and b; the output signal of the single-rail or non-logic circuit is the logical result of the OR of the input signals a and b;

[0050] input signal a, b and Both are 0, the logic unit is in the precharge state; the input signal a and are complementary signals, and b and When it is also a complementary signal, the logic unit is in the logic operation state;

[0051] The single-rail or logic circuit includes NMOS transistor N1', NMOS transistor N2', NMOS transis...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More